(5) УСТРОЙСТВО для ВЫЧИСЛЕНИЯ ФУНКЦИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций синуса и косинуса | 1983 |

|

SU1140116A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для вычисления полиномиальной функции от аналогового аргумента | 1990 |

|

SU1737444A1 |

| Устройство для вычисления обратной величины нормализованной двоичной дроби | 1986 |

|

SU1405050A1 |

| Устройство для деления | 1986 |

|

SU1425657A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Устройство для вычисления функций синуса и косинуса | 1981 |

|

SU1012249A1 |

| Устройство для интерполяции | 1984 |

|

SU1171807A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМА | 1991 |

|

RU2006916C1 |

| Вычислительное устройство | 1986 |

|

SU1432510A1 |

1

Изобретение относится к вычислительным машинам, предназначено для вычисления функций одного аргумента И может быть использовано в специализированной вычислительной аппаратуре и измерительных устройствах.

Известно устройство для вычисления функций, содержащее делитель, коммутатор, дешифратор, реверсивный счетчик, два элемента И и триггер, входы которого соединены с выходами элементов И, входы которых соединены с выходами дешифратора и входами коммутатора, выходы которого соединены с управляющими входами делителя, вход и выход которого соединены соответственно со входом устройства И счетным входом реверсивного счетчика, управляющие входы и выходы которого соединены соответственно с выходами триггера и входами дешифра.тора 1 .

Недостатки данного устройства относительно низкое быстродействие

И ограниченные функциональные возможности. Это связано с длительностью получения одного значения функции,так как требует накопления серий импуль-сов, определяемых кодом задаваемым коммутатором.

Наиболее близким к предлагаемому по технической сущности является устройство содержащее постоянные запоминающие узлы, управляющие входы

10 которых соединены с узлом управления, а также арифметический узел.И

Недостатки известного устройства для вычисления функций - относитель15но большое количество оборудования, ограниченные функциональные возможности и унификация, что связано с .тем, что этим устройством вычисляется только значение одной функции

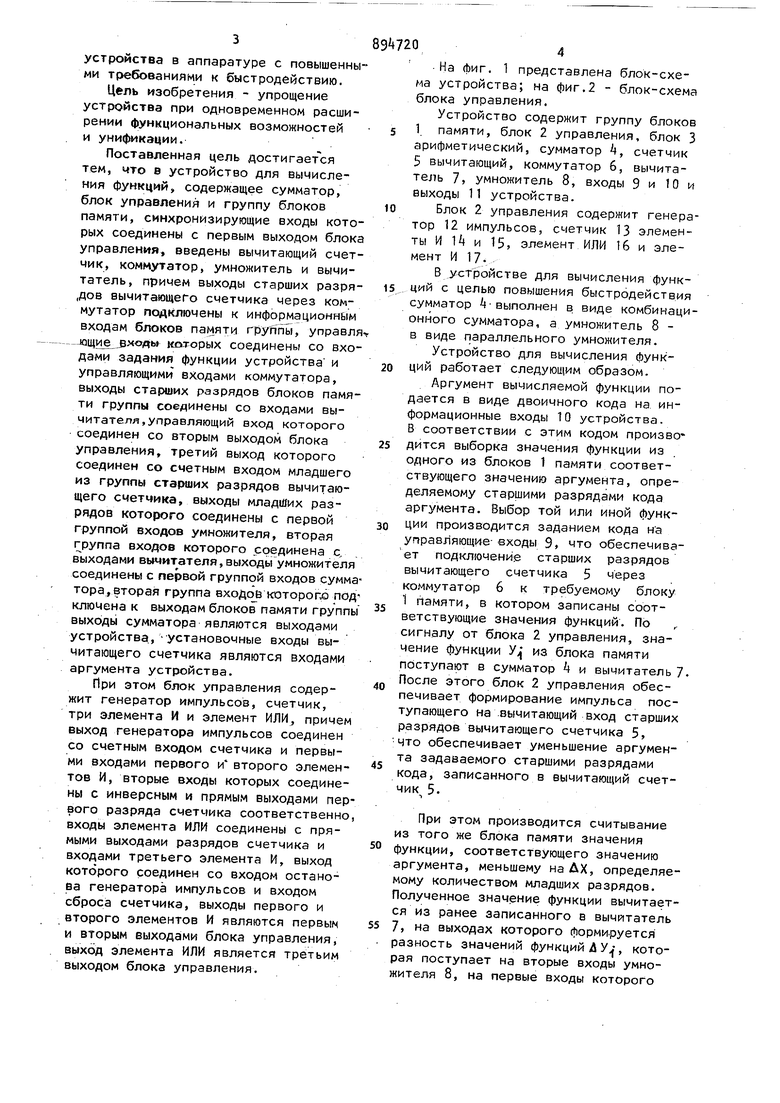

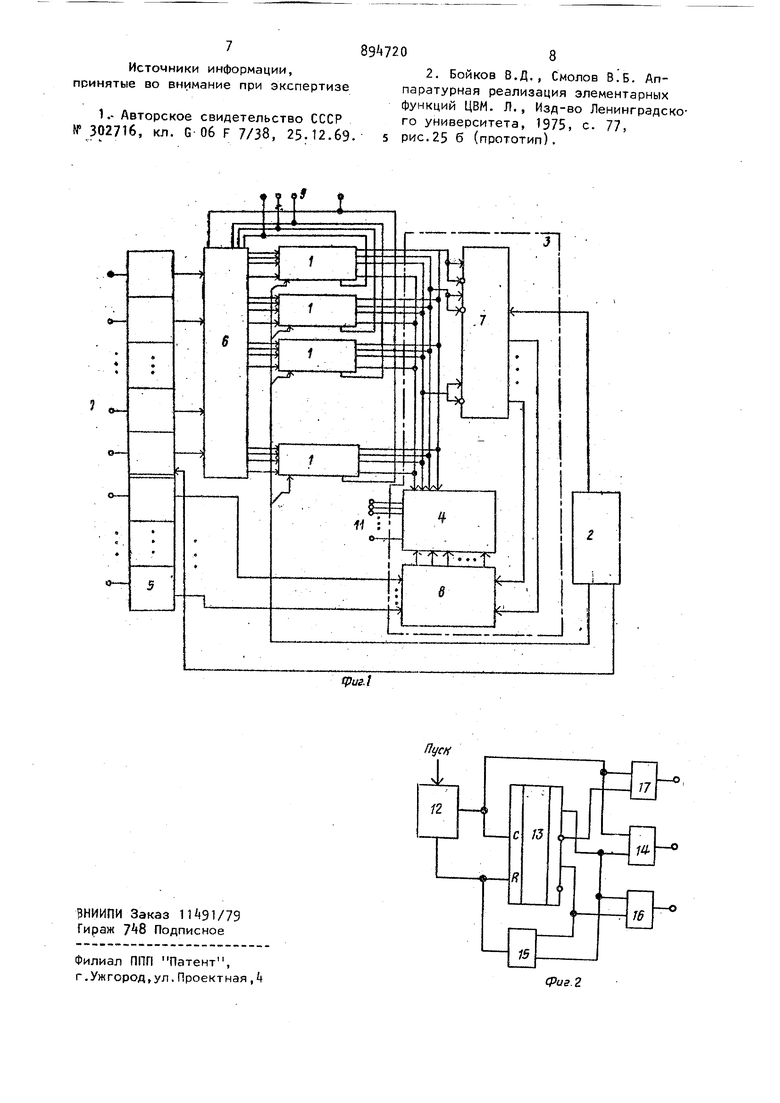

20 и процесс получения этой функции состоит в выполнении относительно большого количества операций, а это ограничивает возможности применения устройства в аппаратуре с повышенными требованиями к быстродействию. Цель изобретения - упрощение устройства при одновременном расширении функциональных возможностей и унификации. Поставленная цель достигается тем, что в устройство для вычисления функций, содержащее сумматор, блок управления и группу блоков памяти, синхронизирующие входы которых соединены с первым выходом блока управления, введены вычитающий счетчик, коммутатор, умножитель и вычитатель, причем выходы старших разря,дов вычитающего счетчика через коммутатор подключены к инфор иационным входам блоков памяти груг1пы, управля -JQЩиe Jxoдb которых соединены со вхо дами задания функции устройства и управляющими входами коммутатора, выходы старших разрядов блоков памяти группы соединены со входами вычитателя,управляющий вход которого соединен со вторым выходом блока управления, третий выход которого соединен со счетным входом младшего из группы старших разрядов вычитающего счетчика, выходы младших разрядов которого соединены с первой группой входов умножителя, вторая группа входов которого соединена с, вь1ходами вычитателя,выходы умножителя соединены с первой группой входов сумм тора,вторая группа вxoдqjзкoтopoг под ключена к выходам блоков памяти групп выходь сумматора являются выходами устройства., Установочные входы вычитающего счетчика являются входами аргумента устройства. При этом блок управления содержит генератор импульсов, счетчик, три элемента И и элемент ИЛИ, причем выход генератора импульсов соединен со счетным входом счетчика и первыми входами первого и второго элементов И, вторые входы которых соединены с инверсным и прямым выходами пер вого разряда счетчика соответственно входы элемента ИЛИ соединены с прямыми выходами разрядов счетчика и входами третьего элемента И, выход которого соединен со входом останова генератора импульсов и входом сброса счетчика, выходы первого и второго элементов И являются первым и вторым выходами блока управления, выход элемента ИЛИ является третьим выходом блока управления. 4 На фиг. 1 представлена блок-схема устройства; на фиг.2 - блок-схема блока управления. Устройство содержит группу блоков I памяти, блок 2 управления, блок 3 арифметический, сумматор 4, счетчик 5 вычитающий, коммутатор б, вычитатель 7, умножитель 8, входы 9 и 10 и выходы 11 устройства. Блок 2 управления содержит генератор 12 импульсов, счетчик 13 элементы И 14 и 15, элемент ИЛИ 16 и элемент И 17В устройстве для вычисления функций с целью повышения быстродействия сумматор 4Выполнен в виде комбинационного сумматора, а умножитель 8 в виде параллельного умножителя. Устройство для вычисления функций работает следующим образом. Аргумент вычисляемой функции подается в виде двоичного кода на информационные входы 10 устройства. В соответствии с этим кодом производится выборка значения функции из одного из блоков 1 памяти соответствующего значению аргумента, определяемому старшими разрядами кода аргумента. Выбор той или иной функции производится заданием кода на управляющие- входы 9, что обеспечивает подключение старших разрядов вычитающего счетчика 5 через коммутатор 6 к требуемому блоку 1 памяти, в котором записаны соответствующие значения функций. По сигналу от блока 2 управления, значение функции из блока памяти поступают в сумматор 4 и вычитатель 7. После этого блок 2 управления обеспечивает формирование импульса поступающего на вычитающий вход старших разрядов вычитающего счетчика 5, что обеспечивает уменьшение аргумента задаваемого старшими разрядами кода, записанного в вычитающий счетчик 5. При этом производится считывание из того же блока памяти значения функции, соответствующего значению аргумента, меньшему на ДХ, определяемому количеством младших разрядов. Полученное значение функции вычитается из ранее записанного в выч татель 7, на выходах которого формируется разность значений функций Л Ух, которая поступает на вторые входы умножителя 8, на первые входы которого 5 яодан код младших разрядов аргумента АХ;,-. Так является кон,, равной 2 , где К - число стантой, младших разрядов вычитающего счетчи A/I AYi величина получается и величины сдвигом информац на постоянное число разрядов К. Пол Л Хя-ДУ-i манное значение поправки суммируется со значением функции Уи обеспечивает получение на вых 11 значения вычисляемой функции &Xi ДУ У. У. Таким образом, использованиепостоянных запоминающих устройств относительно невысокой разрядности обеспечивает построение экономичного по оборудованию устройства, причем количество функций определяется коли чеством 0ЛОКОВ памяти, в то время как остальная часть устройства не меняется при переходе от одной функции к другой, что обеспечивает высокую унификацию оборудования. Кроме того, предлагаемое устройство обеспечивает получение произведения значения функции на некоторый коэффициент, а также значения суммы функции и некотой гр числа. В первом и во втором случаях аргумен функции записывается в группу старших разрядов вычитающего счетчика 5 в группу младших разрядов которого записывается задаваемый коэффициент или число. В первом случае блок 2 управления подает на управляющий вход вычитателя 7 сигнал, обеспечивающий -пропускание функции с выхода блока 1 памяти непосредственно на вы ходы вычитателя 7. При этом на выход умножителя формируется код числа тУ гдеm-заданный коэффициент, а У значение функции. На выходах 10 при этом формируется значение У+тУ. Во втором случае блок управления формирует сигнал, обеспечивающий формирование на выходе вычитателя 7 кода, соответствующего единице. В этом случае код числа т, записанный в младшие разряды регистра вычитающего счетчика 5, передается на выходы умножителя 8 и на выходах формируется код, соответствующий m+Y. 20 Формула изобретения 1. Устройство для вычисления функций, содержащее сумматор, блок управления и группу блоков памяти, синхронизирующие входы которых соединены с первым выходом блока управления, отличающееся тем, что, с целью упрощения устройства, оно содержит вычитающий счетчик, коммутатор, умножитель и вычитатель, причем выходы старших разрядов вычитающего .счетчика через коммутатор ц подключены к информационным входам блоков памяти группы, управляющие входы которых соединены со входами задания функции устройства и управляющими входами коммутатора, выходы старших разрядов блоков памяти группы соединены со входами вычитателя, управляющий вход которого соединен со вторым выходом блока управления, третий выхор которого соединен со счетным входом младшего из группы старших разрядов вычитающего счетчика, выходы младших разрядов которого соединены с первой группой входов умножителя, вторая группа входов которого соединена с выходами вычитателя, выходы умножителя соединены с первой группой входов сумматора, вторая группа входов которого подключена к выходам блоков памяти группы, выходы сумматора являются выходами устройства, установочные входы вычитающего счетчика являются входами аргумента устройства. 2. Устройство по п.1, о т ли ающееся тем, что блок управения содержит генератор импульсов, четчик, три элемента И и элемент ЛИ, причем выход генератора импульов соединен со счетчным входом четчика и первыми входами первого второго элементов И, вторые входы оторых соединены с инверсным и пряым выходами первого разряда счетчика оответственно, входы элемента ИЛИ оединены с прямыми выходами разрядов четчика и входами третьего элемена И, выход которого соединен со ходом останова генератора импульов и входом сброса счетчика, выходы ервого и второго элементов И являтся первым и вторым выходами блока правления, выход элемента ИЛИ являтся третьим выходом блока управлеия.

789 7208

Источники информации,2. Бойков В.Д. , Смолов В.в. Аппринятые во внимание при экспертизе паратурная реализация элементарных

К- Авторское свидетельство СССР го университета, 1975 с 77 № 302716, кл. G 06 F 7/38, 25.12.69. 5 рис.25 б (прототип).

функций ЦВМ. Л., Изд-во Ленинградско

Авторы

Даты

1981-12-30—Публикация

1980-02-11—Подача