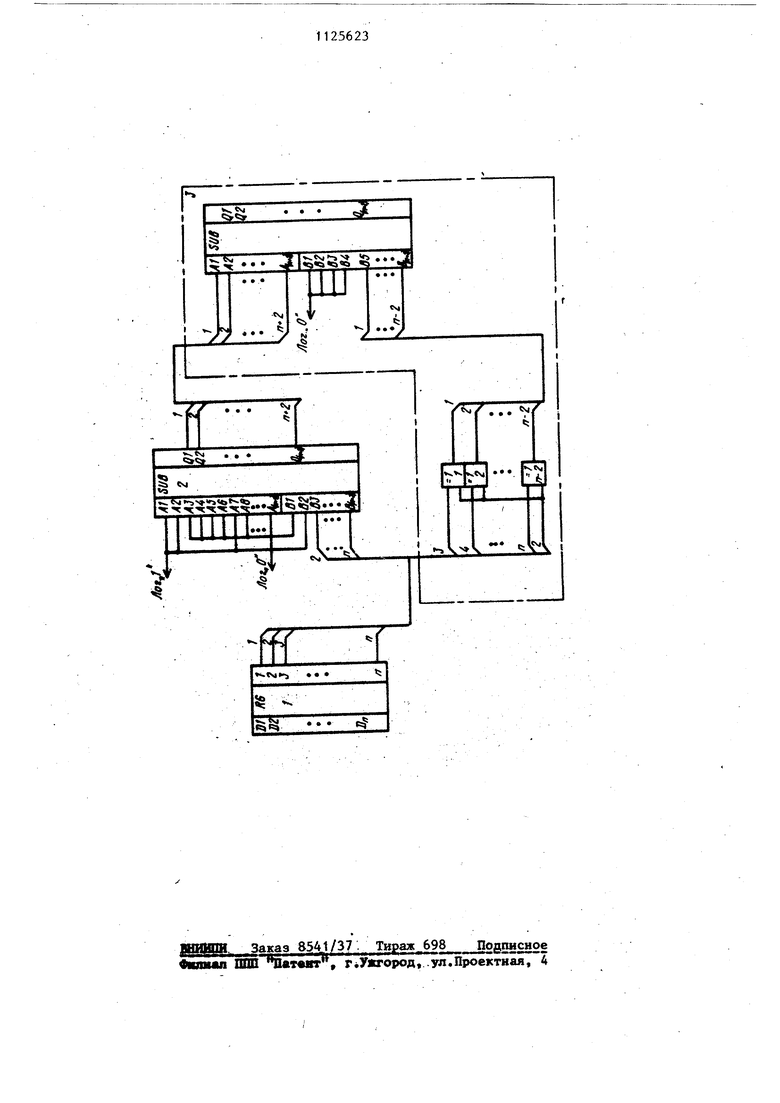

111 Изобретение относится к вычислительной технике и может быть использовано при создании арифметических устройств вычислительных комплексов. Известно устройство для вычисления обратной величины, содержащее ре гистр аргумента, сумматоры, элементы ИЛИ и блок анализа разрядов .ij , Недостатком устройства является его низкое быстродействие. Наиболее близким по технической сущности к изобретению является цифровое устройство для. получения начального приближения к обратной вели чине, содержащеерегистр аргумента, выходы которого соединены с входами узла постоянной памяти для хранения , опорных значений обратной величины аргумента и входом узла умножения, узел вычитания, один вход которого соединен с выходом узла постоянной памяти для хранения опорных значе. НИИ обратной в.еличины аргумента, а . другой - с выходом узла умножения, и узел постоянной памяти для хранения значений разрядов приближенных разностей соседних опорных значений обратной величины, входы которого соединены с выходами старших разрядов регистра аргумента, а выходы - с входами узла умножения 2J . Однако известное устройство обладаегт недостаточным быстродействием. Целью изобретения является повы.шение быстродействия устройства. Цель достигается.тем, что в устройство для приближенного вычисления обратной величины нормализованной двоичной дроби, содержащее регистр аргумента и узел вычитания, введен блок коррекции, содержащий сумматорвычитатель и группу из (п-2) элементов ИСКПЮЧАЩЕЕ ИЛИ (где п - разрядность аргумента), выходы которых со динены соответственно с пятого по (п+2)-й разрядами первой группы входов сумматора-вычитателя, разряды с первого по четвертый которой соеди нены с шиной логического нуля устрой ства, причем первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы объединены и соединены с выходом второго разряда регистра аргумента, выходы с третье го по -и разрядов 1 оторого соедин ны соответственно с вторыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы, узел вычитания устройства выполнен в виде сумматорагвычитателя, первый второй и седьмой разряды первой группы входов И второй разряд второй группы входов которого соединены с щиной логической единицы устройства, а остальные разряды первой группы входов и первый разряд второй группы входов узла вычитания соединены с шиной логического нуля устройства, выходы с второго по и -и регистра аргумента соединены соответственно с третьего по (п+2)-й разрядами второй группы входов узла вычитания, выходы разрядов которого соединены соответственно с разрядами второй группы входов сумматора-вычитателя блока коррекции устройства. На чертеже представлена функциональная схема устройства для приближенного вычисления обратной величины нормализованной двоичной дроби. Устройство содержит регистр 1 аргумента, узел 2 вычитания и блок 3 коррекции, причем выход второго разряда регистра 1 аргумента соединен с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ блока 3 коррекции, вторые входы которых соединены соответственно с выходами-с третьего поп -и разрядов регистра 1 аргумента, а.вькоды элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с пятого по (+2)-й разрядами -первой группы входов сумматора-вычитателя блока 3 коррекции, разряды с первого по четвертый которой соединены с шиной логического нуля устройства, первый, второй и седьмой разряды первой группы входов и второй разряд второй группы входов узла 2 вычитания соединены с шиной логической единицы устройства, а остальные разряды первой группы входов и первый разряд второй группы входов узла 2 вычитания соединены с шиной логического нуля устройства, выходы с второго по п-й регистра 1 аргумента соединены соответственно с третьего по (п+2)-й разрядами второй группы входов узла 2 вычитания, выходы разрядов которого соединены соответственно с разрядами второй группы входов сумматора-вычитателя блока 3 коррекции устройства. Устройство работает следующим образом. В начальный момент в регистр 1 аргумента заносится прямой ход нормализованной двоичной дроби. С выхода регистра 1 аргумента прямой код нормализованной двоичной дроби, сдвинутый на один разряд в сторону старших раз рядов, поступает на узел 2 вычитания постоянной величигде вычитается из ны 3+2, а разряды с третьего по п-й зтого. кода поступают на вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ блока 3 коррекции, на первые входы кото рых поступает разряд кода с весом 2 С выходов элементов ИСКЛЮЧАЮЩЕЕ ИЛИ код коррекции поступает на вторую группу входов сумматора-вычитателя блока 3 коррекции, на первую группу входов которого поступает код разнос ти с выходов узла 2 вычитания. На выходе блока 3 коррекции формируется прямой код приблютенного значения обратной величины нормализованной двоичной дроби. Узел 2 вычитания осуществляет линейную аппроксимацию функции функцией в интервале 0,. Блок 3 коррекции производит опера цию (3+25-2х)-8, , если 0,,75 1-(х+2), если 0,. Величина 8 равна числу в (п-2) мпадших разрядах прямого кода нормализованной двоичной дроби, если разряд кода с весом 2 равен нулю, и инверсии этого числа, если разряд,с весом 2 равен единице. Время, необходимое для вычисления обратной величины нормализованной двоичной дроби в известном устройстве, составляет Josu, ) уми выс , где tpf - время задержки переключения регистра аргумента; - время, необходимое для считывания информации из ПЗУ; uмн время, необходимое для вычисления произведения двух чисел; 9biii время, необходимое для вычисления разности двух чисел. .Время, необходимое для вычисления обратной величины нормализованной двоичной дроби в предлагаемом устройстве, составляет Т i 2-вмч ОБЦ V Поскольку с ,. заведомо больше выи быстродействие предлагаемого устройства выше бьютродействия известного.

tf

«Sl

S

I «

v.. l

J

UiLJ

Г

Лс:::

t

f ... f

,K(44l .

I I I

g:4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приближенного вычисления обратной величины нормализованной двоичной дроби | 1987 |

|

SU1425678A1 |

| Устройство для вычисления обратной величины нормализованной двоичной дроби | 1986 |

|

SU1335985A1 |

| Устройство для вычисления обратной величины нормализованной двоичной дроби | 1986 |

|

SU1405050A1 |

| Устройство для деления чисел | 1988 |

|

SU1580353A1 |

| Устройство для приближенного вычисления обратной величины нормализованной двоичной дроби | 1986 |

|

SU1332321A2 |

| Устройство для деления | 1988 |

|

SU1541598A1 |

| Устройство для деления | 1990 |

|

SU1783521A1 |

| Устройство для деления | 1986 |

|

SU1357947A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для деления | 1989 |

|

SU1709301A1 |

УСТРОЙСТВО ДЛЯ ПРИБЛИЖЕННОГО ВЫЧИСЛЕНИЯ ОБРАТНОЙ ВЕЛИЧИНЫ НОРМАЛИЗОВАННОЙ ДВОИЧНОЙ ДРОБИ, содержащее регистр Аргумента и узел вычитания, о т л и ч а ю щ е е с я тем, что, с целью повьшения быстродействия устройства в него введен блок коррекции, содержащий сумматор-вычи- : татель и группу из (И-2) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ (где п - разрядность аргумента), выходы которых соединены соответственно с пятого по (п+2)-й разрядами первой группы входов сумматора-вычйтателя,; разряды с первого по четвертый которой соединены с щиной логического нуля устройства. Причем первые входы элементов ИСКЛЮЧАЩЕЕ НИИ группы, объединены и соединены с выходом второго разряда регистра аргумента, вькоды с третьего по tl-й разрядов которого соединены соответственно с вторыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы, узел вычитания устройства выполнен в виде сумматора-вычитателя, первый, второй и седьмой разряды первой группы входов и второй разряд второй группы входов которого соединены с шиной логической единицы устройства, а остальные разряды первой группы входов и первый разряд второй группы входов узла вьгчитания соединены с шинбй логического нуля устройства, выходы с второго поп -и регистры аргумента соединены соответственно с третьего по (П+2)-й разрядами второй группы входов узла вычитания, выходы разрядов которого соединены соответственно с разрядами второй группы N9 СЛ входов сумматора-вычитателя блока коррекции устройства. О) N9 СО

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вычисления обратной величины | 1976 |

|

SU732861A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ВО СОЮЗНАЯ-:.l;Jbi.{) 'ii.K^i'-EOiiliБИБЛИОТЕКАВ. И. Жук | 0 |

|

SU318940A1 |

Авторы

Даты

1984-11-23—Публикация

1983-04-01—Подача