4

О

СП

О СП

Изобретение относится к вычислительной технике и предназначено для использования в распределенных многопроцессорных системах цифровой обра- борки сигналов.

Цель изобретения - повышение быстродействия при одновременном сокращении аппаратурных затрат.

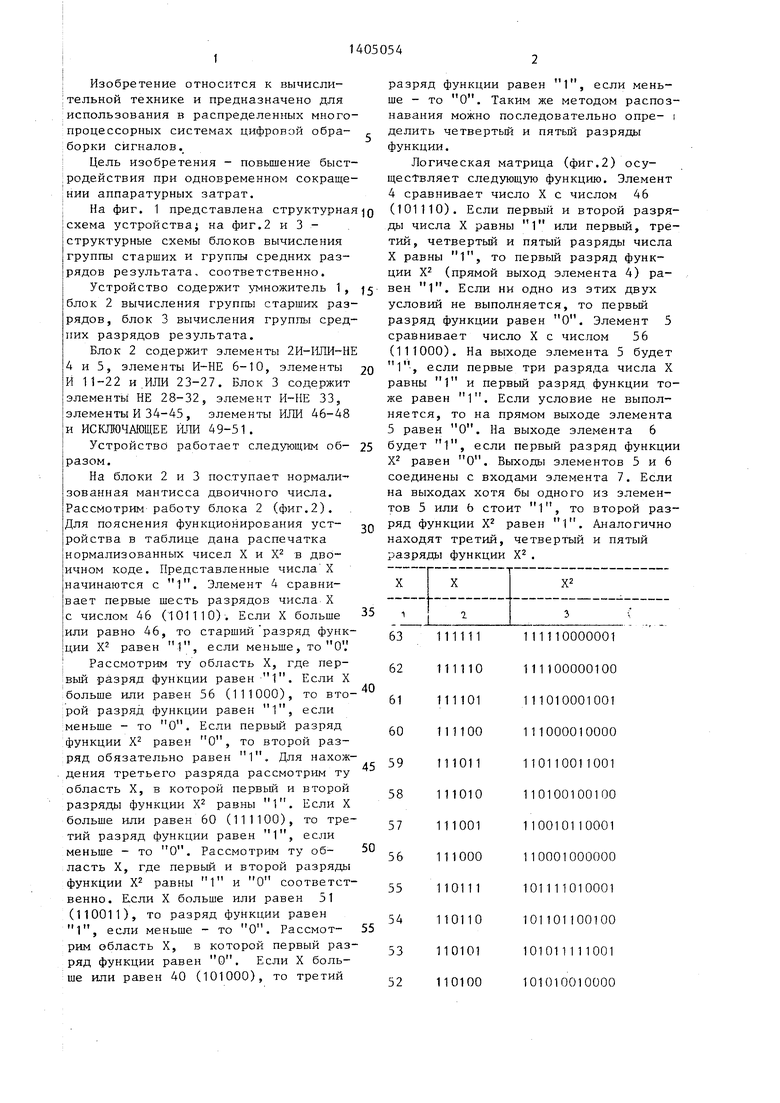

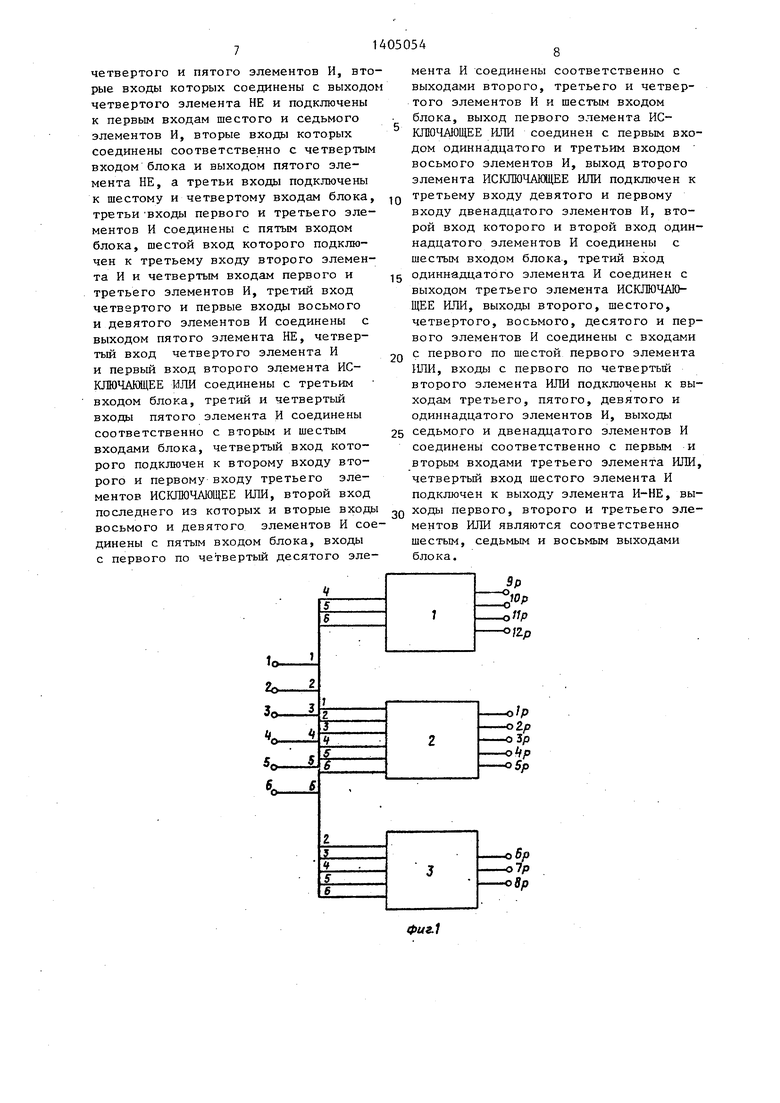

На фиг. 1 представлена структурная схема устройства,; на фиг.2 и 3 - структурные схемы блоков вычисления группы старших и группы средних разрядов результата, соответственно.

Устройство содержит умножитель 1, блок 2 вычисления группы старших разрядов, блок 3 вычисления группы средних разрядов результата.

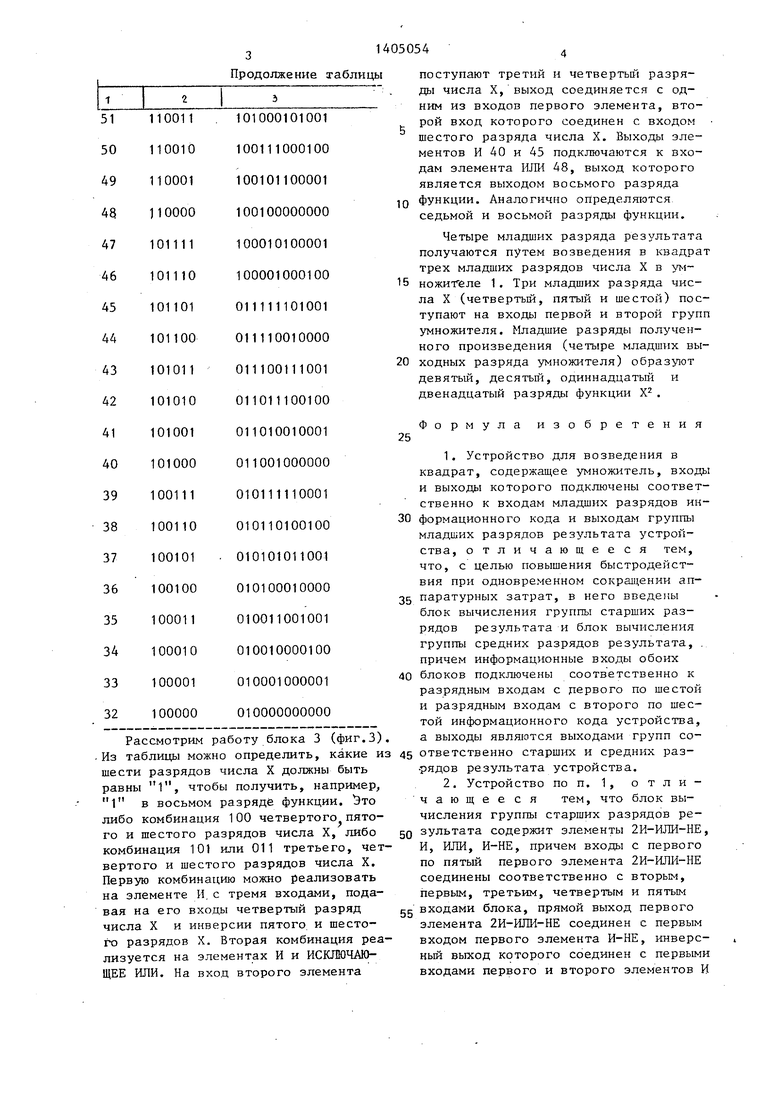

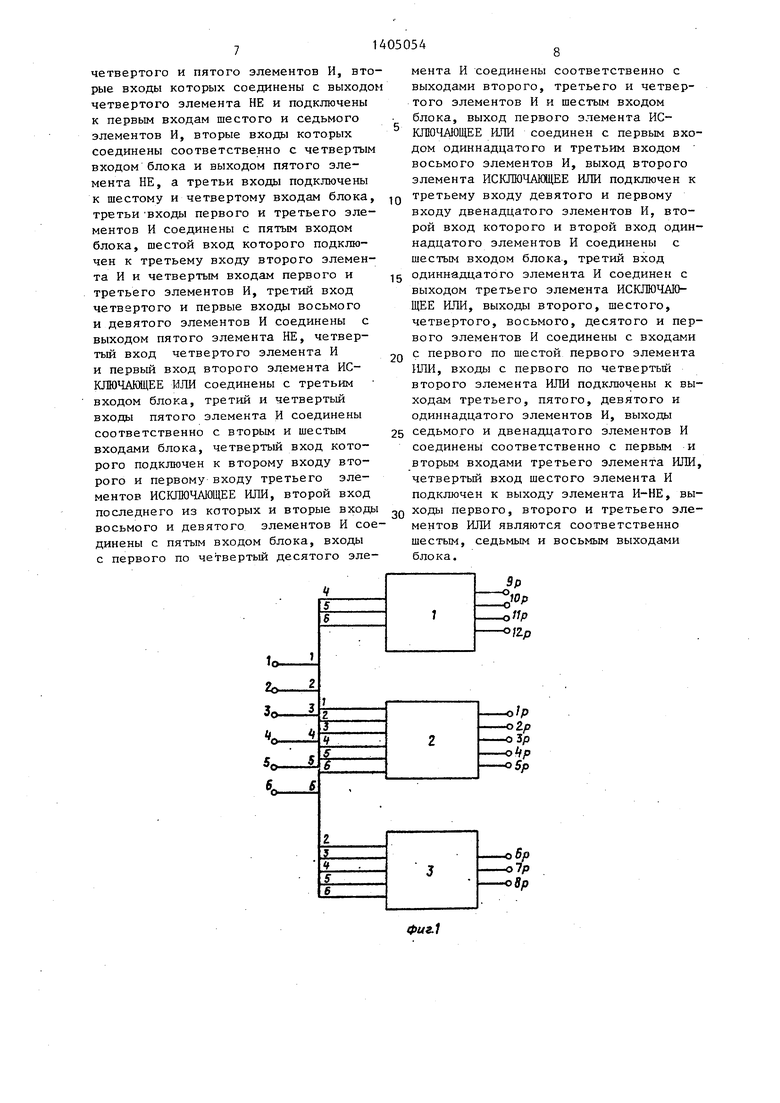

Блок 2 содержит элементы 2И-11ПИ-НЕ 4 и 5, элементы И-НЕ 6-10, элементы И 11-22 и.ИЛИ 23-27. Блок 3 содержит элементы НЕ 28-32, элемент И-НЕ 33, элементы И 34-45, элементы ИЛИ 46-48 и ИСКЛЮЧАЮЩЕЕ 1ШИ 49-51.

Устройство работает следуюш;им об- разом.

На блоки 2 и 3 поступает нормали-- зованная мантисса двоичного числа. Рассмотрим работу блока 2 (фиг.2). Для пояснения функционирования устройства в таблице дана распечатка нормализованных чисел X и Х в двоичном коде. Представленные числа X начинаются с 1. Элемент 4 сравнивает первые шесть разрядов числа X с числом 46 (101110). Если X больше или равно 46, то старший разряд функции Х равен 1, если меньше, то OV

Рассмотрим ту область X, где пер

Q

5

0

5

0

разряд функции равен 1, если меньше - то О. Таким же методом распознавания можно последовательно опре- i делить четвертый и пятый разряды функции.

Логическая матрица (фиг.2) осуществляет следующую функцию. Элемент

4сравнивает число X с числом 46 (101110). Если первый и второй разряды числа X равны 1 или первый, третий, четвертый и пятый разряды числа X равны 1, то первый разряд функции Х (прямой выход элемента 4) равен 1. Если ни одно из этих двух условий не выполняется, то первый разряд функции равен О. Элемент 5 сравнивает число X с числом 56 (111000). На выходе элемента 5 будет 1, если первые три разряда числа X равны 1 и первый разряд функции тоже равен 1. Если условие не выполняется, то на прямом выходе элемента

5равен О. На выходе элемента 6 будет 1, если первый разряд функции Х равен О. Выходы элементов 5 и 6 соединены с входами элемента 7. Если на выходах хотя бы одного из элементов 5 или 6 стоит 1, то второй разряд функции Х равен 1. Аналогично находят третий, четвертый и пятый разряды функции Х.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПРИВЕДЕНИЯ ФУНКЦИЙ К МУЛЬТИПЛИКАТИВНОМУ АЛГОРИТМУ ВЫЧИСЛЕНИЙ | 1990 |

|

RU2028659C1 |

| Устройство для извлечения квадратного корня | 1988 |

|

SU1569827A1 |

| Устройство для вычисления логарифмачиСлА | 1979 |

|

SU849210A1 |

| Устройство для сложения в двоичном избыточном коде | 1987 |

|

SU1413623A1 |

| Управляемый арифметический модуль | 1979 |

|

SU832553A1 |

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ СОВМЕСТНО ХРАНИМЫХ ГРАНИЦ ПРИ ИНТЕРВАЛЬНЫХ ВЫЧИСЛЕНИЯХ | 2012 |

|

RU2497179C1 |

| Устройство для умножения чисел | 1990 |

|

SU1741129A1 |

| Устройство для извлечения квадратного корня | 1989 |

|

SU1658150A2 |

| Функциональный преобразователь угла поворота вала в код | 1984 |

|

SU1218465A1 |

Изобретение относится к вычислительной технике и предназначено для использования в системах цифровой обработки сигналов. Цель изобретения - повышение быстродействия при одновременном сокращении аппаратурных затрат - достигается тем, что устройство позволяет осуществлять одновременную обработку старших и младших разрядов. Четыре младших разряда результата получаются путем возведения в квадрат трех младших разрядов аргумента в умножителе. В устройство введены блоки вычисления группы старших и средних разрядов результата, представляющие собой логические матрицы. 2 з.п. ф-лы, 3 ил. Ф

вый разряд функции равен 1 . Если X больше или равен 56 (111000), то второй разряд функции равен 1, если меньше - то О. Если первый разряд функции Х равен О, то второй разряд обязательно равен 1. Для нахождения третьего разряда рассмотрим ту область X, в которой первьм и второй разряды функции Х равны 1. Если X больше или равен 60 (111100), то третий разряд функции равен 1, если меньше - то О. Рассмотрим ту об- ласть X, где первый и второй разряды функции Х равны 1 и О соответственно. Если X больше или равен 51 (110011), то разряд функции равен 1, если меньше - то О. Рассмот- рим область X, в которой первый разряд функции равен О. Если X больше или равен 40 (101000), то третий

Продолжение таблицы

Рассмотрим работу блока 3 (фиг.З). Из таблицы можно определить, какие из шести разрядов числа X должны быть равны 1, чтобы получить, например, 1 в восьмом разряде функции, то либо комбинация 100 четвертого пятого и шестого разрядов числа X, либо комбинация 101 или 011 третьего, четвертого и шестого разрядов числа X, Первую комбинацию можно реализовать на элементе И,с тремя входами, подавая на его входы четвертый разряд числа X и инверсии пятого и шестого разрядов X. Вторая комбинация реализуется на элементах И и ИСКЛЮЧАЮЕЕ ИЛИ. На вход второго элемента

поступают третий и четвертый разряды числа X, выход соединяется с одним из входов первого элемента, второй вход которого соединен с входом шестого разряда числа X. Выходы элементов И 40 и 45 подключаются к входам элемента ИЛИ 48, выход которого является вь ходом восьмого разряда 0 функции. Аналогично определяются седьмой и восьмой разряды функции.

Четыре младших разряда результата получаются путем возведения в квадрат трех младших разрядов числа X в ум5 ножи-геле 1 . Три младших разряда числа X (четвертьй, пятый и шестой) поступают на входы первой и второй групп умножителя. Младшие разряды полученного произведения (четыре младших вы0 ходных разряда умножителя) образ пот девятый, десятый, одиннадцатый и двенадцатый разряды функции Х.

Формула изобретения 5

0 блоков подключены соответственно к разрядным входам с первого по шестой и разрядным входам с второго по шестой информационного кода устройства, а выходы являются выходами групп со5 ответственно старших и средних разрядов результата устройства.

с входами блока, прямой выход первого элемента 2И-ИЛИ-НЕ соединен с первым входом первого элемента И-НЕ, инверс- ньй выход которого соединен с первыми входами первого и второго элементов И

; второго элемента 2И-ИЛИ-НЕ, .вторые входы которых подключены к прямому выходу первого элемента 2 И-ИЛИ-НЕ, второй и третий входы первого элемента ; И-НЕ соединены с одноименными вхо- ;дами блока, а его прямой выход под- 1 ключей к первому входу первого эле- I мента ИЛИ и первьпч входам первого, второго и третьего элементов И, вто- i рые входы которых соединены с одноименными входами блока, а их выходы подключены к первым входам соответственно второго, третьего и четвертого элементов ШМ, второй вход первого элемента ИЛИ соединен с выходом четвертого элемента И, с первыми входами второго элемента И-НЕ и пятого и шестого элементов И, инверсный выход первого элемента 2И-ИЛИ-НЕ соединен с первым входом четвертого элементов И, второй вход которого подключен к первому входу блока, инверсный выход второго элемента И-НЕ подключен к вторым входам пятого и шестого элементов И, третьи входы которых и второй вход второго элемента И-НЕ подключены соответственно к четвертому, пятому и третьему входам блока, прямой выход второго элемента И-НЕ подключен к первым входам седьмого элемента И, третьего и четвёртого элементов И-НЕ и второму входу второго элемента ИЛИ, третий вход которого и первые входы вось- Мого, элемента И и пятого элемента |И-НЕ соединены с прямым выходом вто- Sporo элемента 2И-ИЛИ-НЕ, инверсный iвыход которого и инверсный выход пер- 1вого элемента И-НЕ подключены соответственно к первому и второму входам девятого элемента И, третий вход которого соединен с вторым входом блока, а выход подключен к первому входу десятого элемента И и второму входу третьего элемента ИЛИ, третий вход которого соединен с прямым, выходом четвертого элемента И-НЕ, второй и третий входы которого подключены соответственно к пятому и шестому входам блока,, а инверсный выход - к второму входу седьмого элемента И, третий и четвертый входы которого соединены соответственно с выходом пятого элемента ИЛИ и инверсным выходом третьего элемента И-НЕ, второй вход которого подключен к четвертому входу блока, а прямой выход - к четвертому входу третьего элемента КПИ и второ

0

5

му входу четвертого элемента ИЛИ, входы которого с третьего по восьмой подключены соответственно к выходам одиннадцатого, восьмого, десятого, седьмого, шестого и двенадцатого элементов И, входы с первого по четвертый которого соединены соответственно с входами с третьего по шестой блока, третий, четвертый и пятый входы первого элемента И второго элемента 2И-ИЛИ-НЕ соединены соответственно с пятым, шестым и вторым входами блока, третий и четвертый входы вто- 5 рого элемента И и второго элемента 2И-ИЛИ-НЕ подключены соответственно к четвертому и второму входам блока, пятый вход третьего элемента ИЛИ и первый вход одиннадцатого элемента И подключены к прямому выходу пятого элемента И-НЕ, второй и третий входы которого подключены к четвертому и пятому входам блока соответственно, а инверсный выход соединен с вторым входом восьмого элемента И, третий вход которого подключен к четвертому входу блока, шестой вход третьего элемента РШИ подключен к выходу пятого элемента И, первый и второй входы пятого элемента ИЛИ - к пятому и шестому входам блока, вторые входы десятого и одиннадцатого элементов И - соответственно к пятому и шестому входам блока, прямой выход первого элемента 2И-ИЛИ-НЕ и выходы первого, второго, третьего и четвертого элементов ИЛИ являются соответственно первым, вторым, третьим, четвертым и пятым выходами блока.

0

5

0

5

0

5

четвертого и пятого элементов И, вторые входы которых соединены с выходом четвертого элемента НЕ и подключены к первым входам шестого и седьмого элементов И, вторые входы которых соединены соответственно с четвертым входом блока и выходом пятого элемента НЕ, а третьи входы подключены к шестому и четвертому входам блока, третьи ВХОДЫ первого и третьего элементов И соединены с пятым входом блока, шестой вход которого подключен к третьему входу второго элемента И и четвертым входам первого и третьего элементов И, третий вход четвертого и первые входы восьмого и девятого элементов И соединены с выходом пятого элемента НЕ, четвертый вход четвертого элемента И и первый вход второго элемента ИС- КЛЮЧАЩЕЕ ИЛИ соединены с третьим входом блока, третий и четвертый входы пятого элемента И соединены соответственно с вторым и шестым входами блока, четвертый вход которого подключен к второму входу второго и первому входу третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход

10

мента И соединены соответственно с выходами второго, третьего и четвертого элементов И и шестым входом блока, выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом одиннадцатого и третьим входом восьмого элементов И, выход второго элемента ИСКЛЮЧАЩЕЕ ИЛИ подключен к третьему входу девятого и первому входу двенадцатого элементов И, второй вход которого и второй вход одиннадцатого элементов И соединены с шестым входом блока, третий вход

g одиннадцатого элемента И соединен с выходом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы второго, шестого, четвертого, восьмого, десятого и первого элементов И соединены с входами

2Q с первого по шестой первого элемента ИЛИ, входы с первого по четвертый второго элемента ИЛИ подключены к выходам третьего, пятого, девятого и одиннадцатого элементов И, выходы

25 седьмого и двенадцатого элементов И соединены соответственно с первым и вторым входами третьего элемента ИЛИ, четвертый вход шестого элемента И

подключен к выходу элемента И-НЕ, вы- последнего из которых и вторые входы Q ходы первого, второго и третьего эле- восьмого и девятого элементов И сое- ментов ИЛИ являются соответственно динены с пятым входом блока, входы шестым, седьмым и восьмым выходами с первого по четвертый десятого эле- блока.

мента И соединены соответственно с выходами второго, третьего и четвертого элементов И и шестым входом блока, выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом одиннадцатого и третьим входом восьмого элементов И, выход второго элемента ИСКЛЮЧАЩЕЕ ИЛИ подключен к третьему входу девятого и первому входу двенадцатого элементов И, второй вход которого и второй вход одиннадцатого элементов И соединены с шестым входом блока, третий вход

одиннадцатого элемента И соединен с выходом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы второго, шестого, четвертого, восьмого, десятого и первого элементов И соединены с входами

с первого по шестой первого элемента ИЛИ, входы с первого по четвертый второго элемента ИЛИ подключены к выходам третьего, пятого, девятого и одиннадцатого элементов И, выходы

седьмого и двенадцатого элементов И соединены соответственно с первым и вторым входами третьего элемента ИЛИ, четвертый вход шестого элемента И

t

J« f

2B

| Квадратор | 1979 |

|

SU788106A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Мурога С | |||

| Системное проектирование сверхбольших интегральных схем: Перев | |||

| с англ./Под ред | |||

| В.М.Кисель- никова | |||

| - М., 1985, кн.2, с | |||

| Аппарат, предназначенный для летания | 0 |

|

SU76A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1988-06-23—Публикация

1986-12-01—Подача