Изобретение относится к вычислительной технике и предназначено для использо- вания в цифровых вычислительных машинах различного назначения.

Известно устройство для умножения, содержащее счетчик, блок микропрограммного управления, элементы ИЛИ, регистр множителя, регистр результата, сумматор, регистр множимого и соответствующие связи.

Недостатком устройства является отсутствие возможности умножения чисел двойной разрядности (2п) при наличии в устройстве n-разрядного операционного блока, так как отсутствуют для этого аппаратно-микропрограммные средства.

Наиболее близким к предлагаемому является устройство для умножения чисел с фиксированной запятой, содержащее операционный блок, регистр адреса, регистр

микрокоманд, счетчик циклов, блок синхронизации, семь элементов И, четыре элемента НЕ, элемент ИЛИ-НЕ, пять элементов И-НЕ, два элемента 2И-ИЛИ, триггер коротких тактов, пять элементов ИЛИ, элемент 2И-ИЛИ-НЕ, триггер коррекции результата, триггер-округления, триггер выдвигаемых разрядов множителя, триггер анализа значащего бита, триггер знака множимого, триггер блокировки.

Недостатком этого устройства является невозможность умножения чисел двойной разрядности (2п) при n-разрядном операционном блоке.

Цель изобретения - расширение функциональных возможностей за счет умножения 2п-разрядных чисел HJI п-разрядном оборудовании.

Поставленная цель достигается тем, что в устройство для умножения чисел, содер-ч Јь

ю о

жащее счетчик циклов, регистр микрокоманд, элемент ИЛИ, три элемента И-НЕ, три элемента И, три элемента НЕ, элемент ИЛИ- НЕ, первый и второй элементы 2И-ИЛИ, триггер знака, триггер выдвигаемых разрядов множителя, триггер анализа значащего бита, блок синхронизации и операционный блок, информационные входы и выходы которого соединены соответственно с информационными входами и выходами устройства, входы микрокоманд, пуска и сброса которого соединены соответственно с информационным входом регистра микрокоманд и входами пуска и сброса блока син- хро.глзации, первый выход которого соединен с синхровходом регистра микрокоманд, первый выход которого соединен с первым входом первого элемента И-НЕ, второй вход которого соединен с вторым выходом блока синхронизации, выходы с третьего по пятый которого соединены с соответствующими входами элемента ИЛИ, выход которого соединен с первым входом второго элемента И-НЕ, второй вход которого соединен с вторым выходом регистра микрокоманд, а выход-с входом чтения операционного блока, выход знака которого соединен с информационным входом триггера знака, синхр овход которого соединен с выходом третьего элемента И-НЕ, первый вход которого соединен с третьим выходом регистра микрокоманд, а второй вход - с входом первого элемента НЕ и первым входом первого элемента И, второй вход которого соединен с четвертым выходом микрокоманд, а выход - с входом -1 счетчика циклов, вход записи которого соединен с выходом первого элемента И-НЕ и входом сброса триггера выдвигаемых разрядов множителя, прямой выход которого соединен с синхровходом триггера анализа значащего бита, информационный вход которого соединен с входом логической единицы устройства, первый выход условия ветвления которого соединен с выходом элемента ИЛИ-НЕ, первый вход которого соединен с выходом переполнения операционного блока, вход синхронизации которого соединен с выходом первого элемента НЕ, шестой выход блока синхронизации соединен с первым входом второго элемента И, второй вход которого соединен с пятым выходом регистра микрокоманд, введены формирователь адреса, триггер переноса, триггер частичных произведений, третий элемент 2И-ИЛИ и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с выходом триггера частичных произведений, информационный вход которого соеди- нен с выходом младшего разряда

информационного выхода операционного блока, вход переноса которого соединен с выходом первого элемента 2И-ИЛИ, первый вход которого соединен с шестым выходом

регистра микрокоманд, седьмой восьмой и девятый выходы которого соединены соответственно с входами -1 и +1, и входом установки нулевого адреса формирователя адреса, вход записи которого соединен с

0 выходом второго элемента И, а информационный вход - с входом адреса устройства, информационный вход которого соединен с информационным входом счетчика циклов, выход которого соединен с вторым входом

5 элемента ИЛИ-НЕ, выход формирователя адреса соединен с адресным входом операционного блока, выход младшего разряда множителя которого соединен с вторым выходом условия ветвления устройства и ин0 формационным входом триггера выдвигаемых разрядов множителя, синх- ровход которого соединен с выходом первого элемента НЕ и синхровходами триггера частичных произведений и триггера перено5 са, выход которого соединен с третьим входом первого элемента 2И-ИЛИ, второй вход которого соединен с десятым выходом регистра микрокоманд, одиннадцатый выход которого соединен с первым входом второго

0 элемента 2И-ИЛИ и входом второго элемента НЕ, выход которого соединен с четвертым входом второго элемента 2И-ИЛИ, второй и третий входы которого соединены соответственно с выходами триггера знака

5 и триггера анализа значащего бита, вход сброса которого соединен с двенадцатым выходом регистра микрокоманд, тринадцатый выход которого соединен с первым входом третьего элемента И, второй вход и

0 выход которого соединены соответственно с выходом элемента ИЛИ и входом первого элемента НЕ, первый вход сдвига операционного блока соединен с выходом второго элемента 2И-ИЛИ, пятый вход которого со5 единен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с информационным входом триггера переноса и выходом переноса операционного блока, второй вход сдвига которого соеди0 нен с выходом третьего элемента 2И-ИЛИ, первый вход которого соединен с четырнадцатым выходом регистра микрокоманд, пятнадцатый выход которого соединен со вторым входом третьего элемента 2И-ИЛИ

5 и входом третьего элемента НЕ, выход которого соединен с третьим входом первого элемента И.третьего элемента 2И-ИЛИ, четвертый вход которого соединен с инверсным выходом триггера выдвигаемых разрядов множителя, шестнадцатый выход

регистра микрокоманд соединен с входом микроопераций операционного блока, вход частоты блока синхронизации соединен с входом частоты устройства.

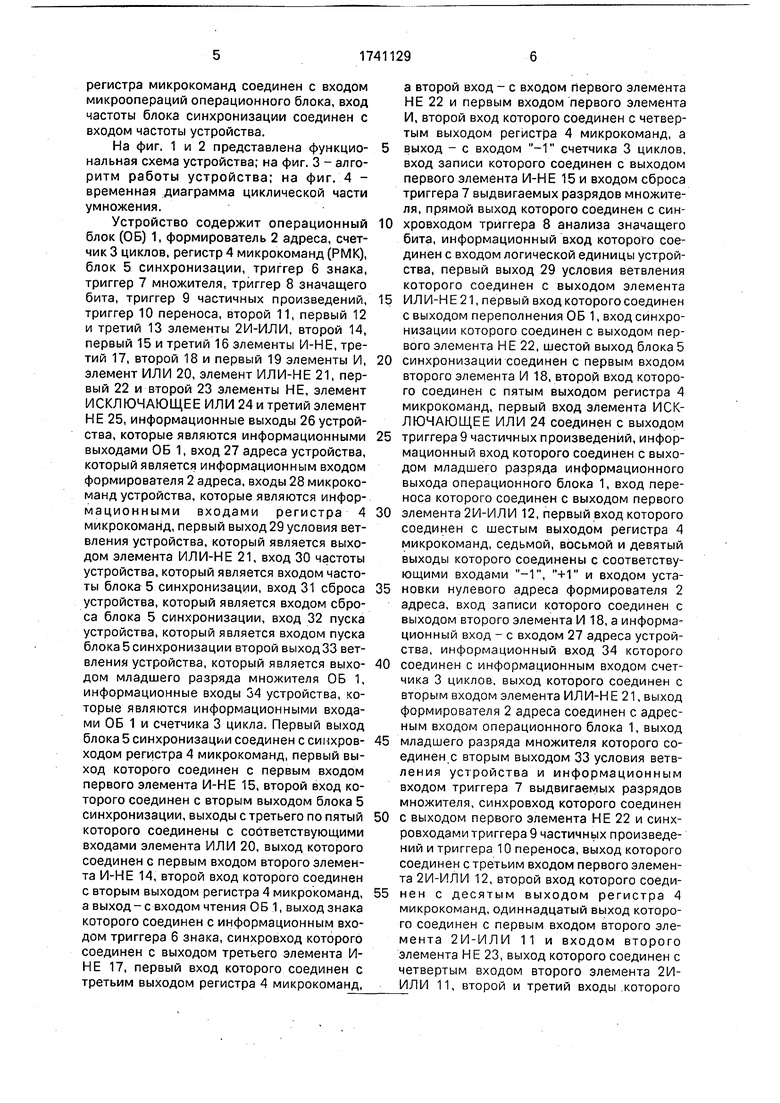

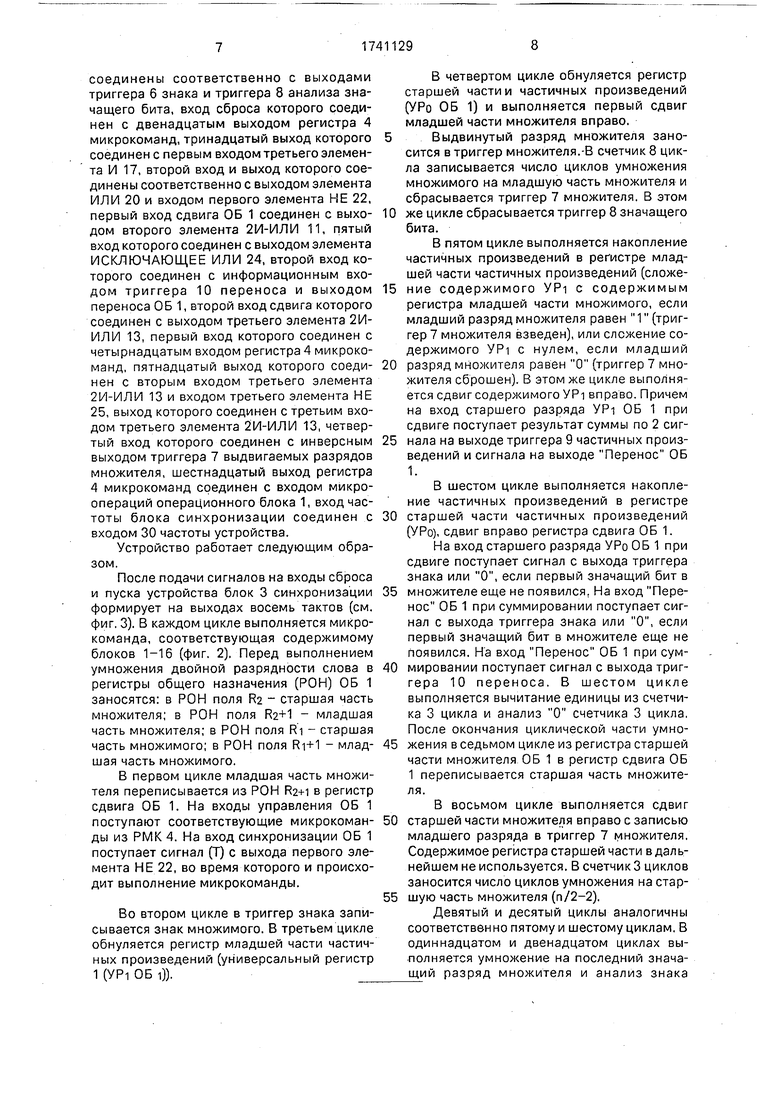

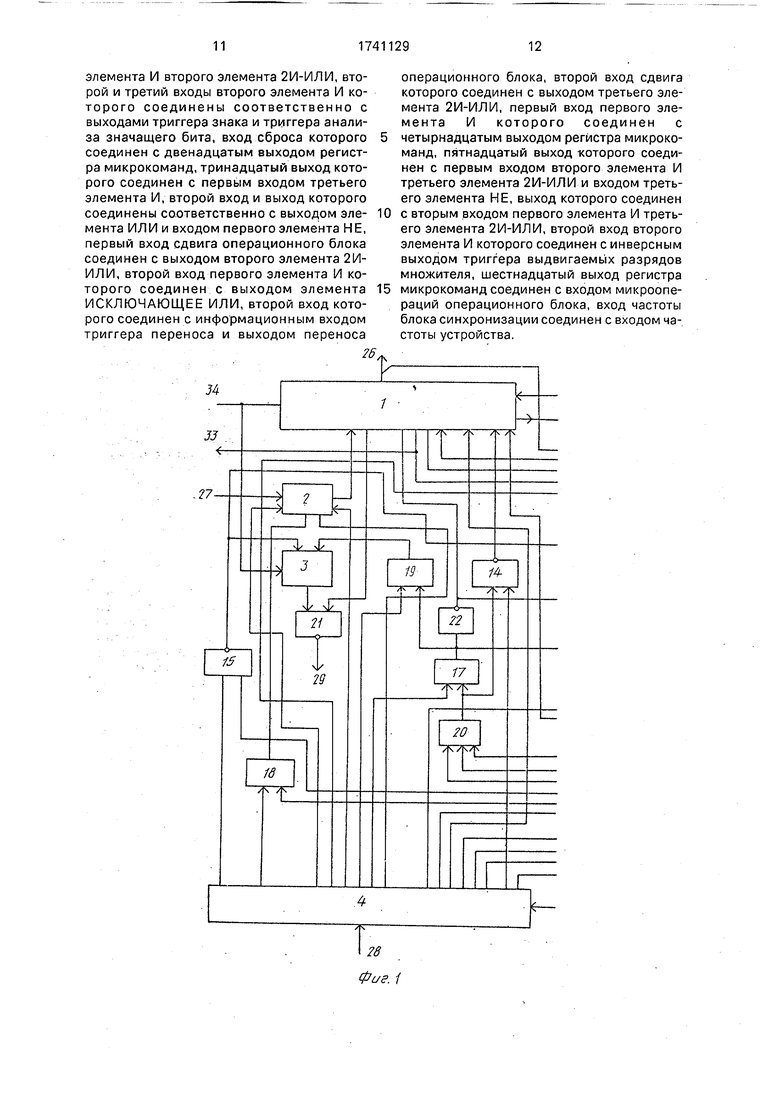

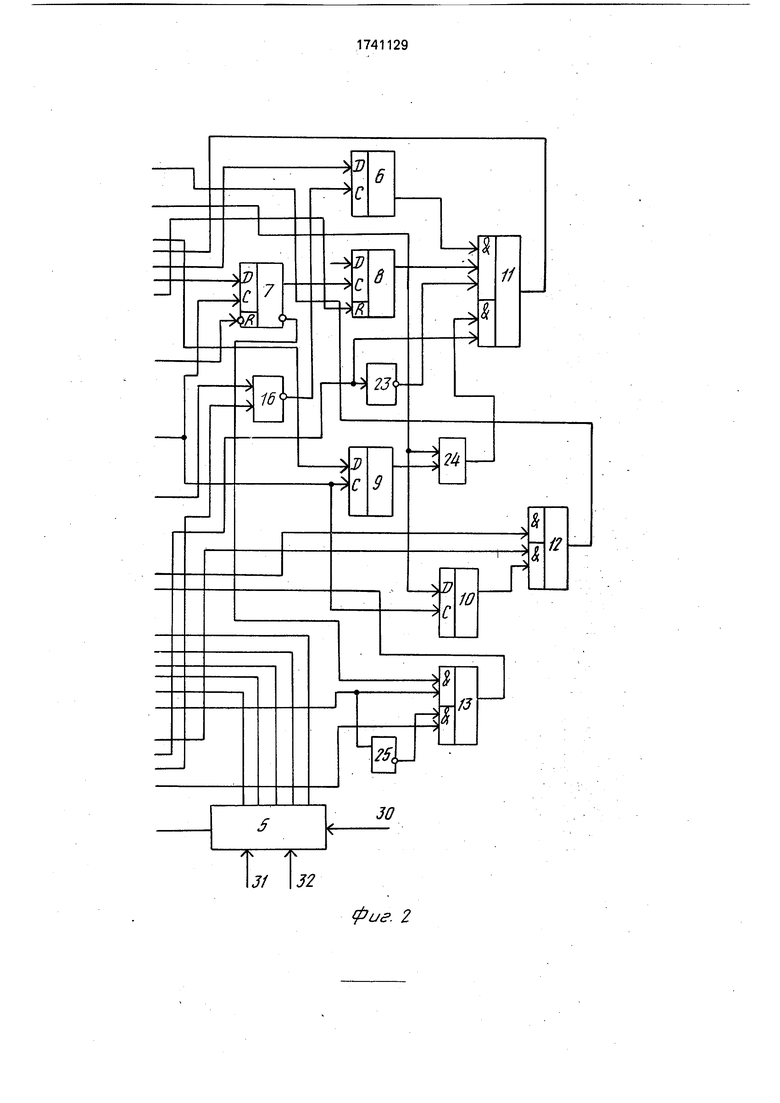

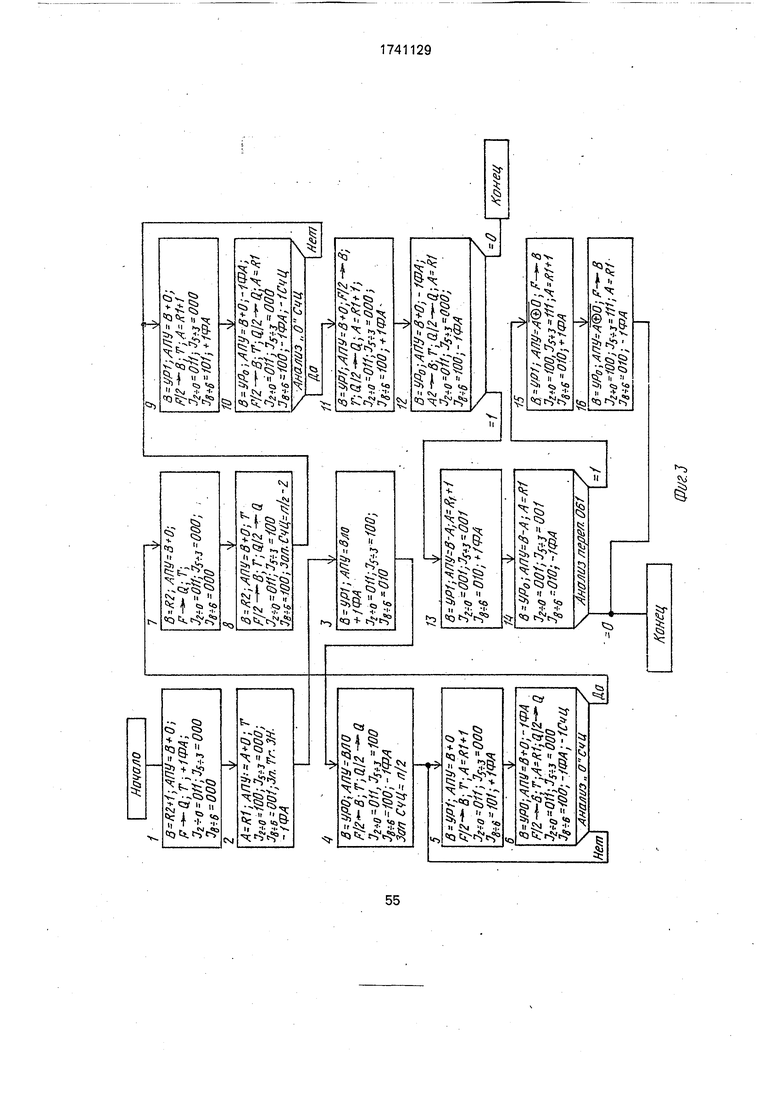

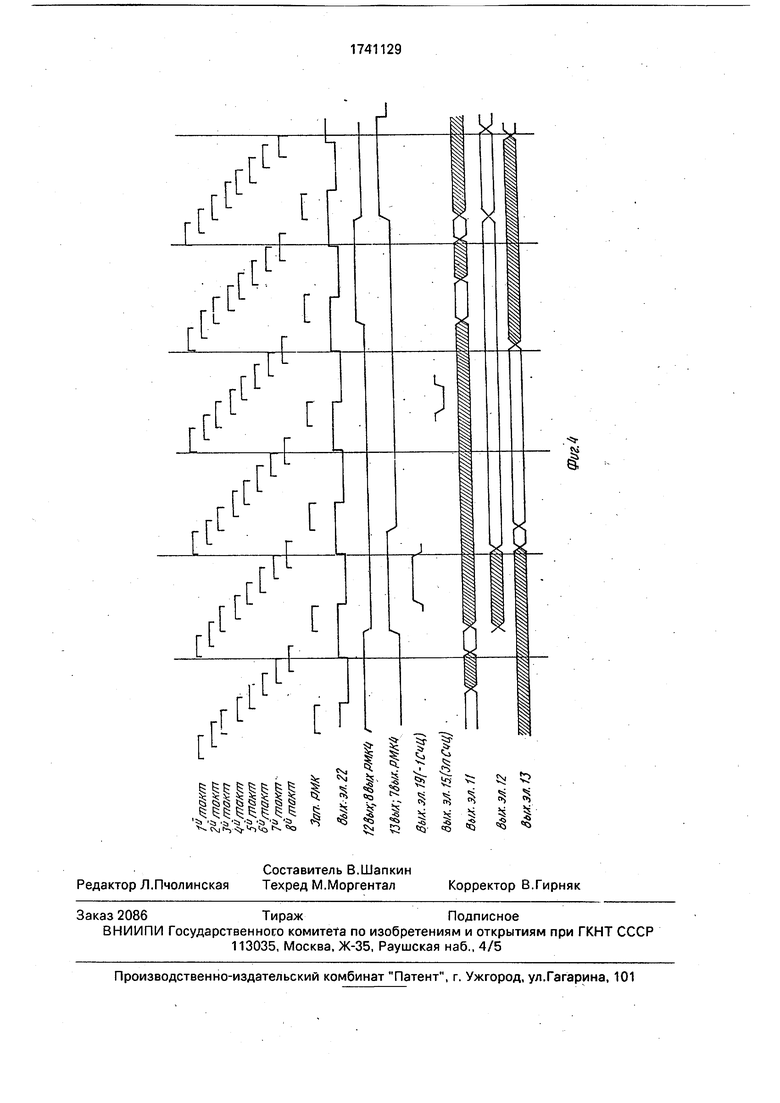

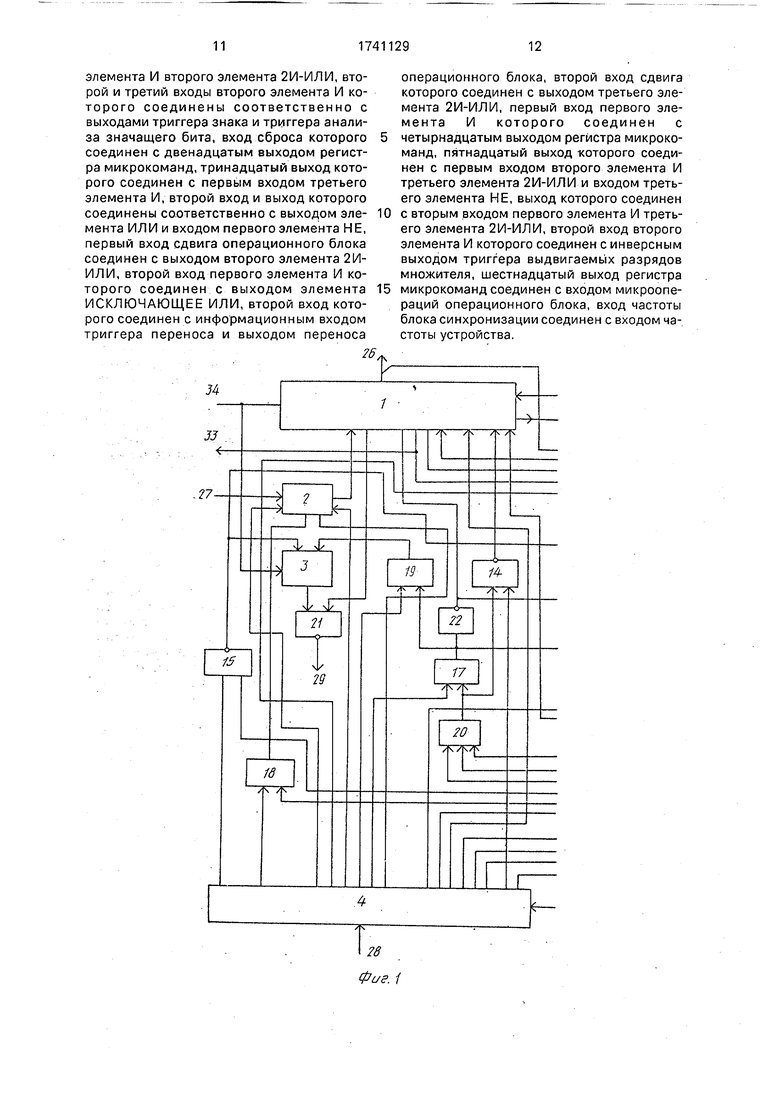

На фиг. 1 и 2 представлена функциональная схема устройства; на фиг. 3 - алгоритм работы устройства; на фиг. 4 - временная диаграмма циклической части умножения.

Устройство содержит операционный блок (ОБ) 1, формирователь 2 адреса, счетчик 3 циклов, регистр 4 микрокоманд (РМК), блок 5 синхронизации, триггер 6 знака, триггер 7 множителя, триггер 8 значащего бита, триггер 9 частичных произведений, триггер 10 переноса, второй 11, первый 12 и третий 13 элементы 2И-ИЛИ, второй 14, первый 15 и третий 16 элементы И-НЕ, третий 17, второй 18 и первый 19 элементы И, элемент ИЛИ 20, элемент ИЛ И-НЕ 21, первый 22 и второй 23 элементы НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 24 и третий элемент НЕ 25, информационные выходы 26 устройства, которые являются информационными выходами ОБ 1, вход 27 адреса устройства, который является информационным входом формирователя 2 адреса, входы 28 микрокоманд устройства, которые являются информационными входами регистра 4 микрокоманд, первый выход 29 условия ветвления устройства, который является выходом элемента И Л И-НЕ 21, вход 30 частоты устройства, который является входом частоты блока 5 синхронизации, вход 31 сброса устройства, который является входом сброса блока 5 синхронизации, вход 32 пуска устройства, который является входом пуска блокабсинхронизации второй выход33 ветвления устройства, который является выходом младшего разряда множителя ОБ 1, информационные входы 34 устройства, которые являются информационными входами ОБ 1 и счетчика 3 цикла. Первый выход блока 5 синхронизации соединен с синхров- ходом регистра 4 микрокоманд, первый выход которого соединен с первым входом первого элемента И-НЕ 15, второй вход которого соединен с вторым выходом блока 5 синхронизации, выходы с третьего по пятый которого соединены с соответствующими входами элемента ИЛИ 20, выход которого соединен с первым входом второго элемента И-НЕ 14, второй вход которого соединен с вторым выходом регистра 4 микрокоманд, а выход - с входом чтения ОБ 1, выход знака которого соединен с информационным входом триггера 6 знака, синхровход которого соединен с выходом третьего элемента И- НЕ 17, первый вход которого соединен с третьим выходом регистра 4 микрокоманд,

а второй вход - с входом первого элемента НЕ 22 и первым входом первого элемента И, второй вход которого соединен с четвертым выходом регистра 4 микрокоманд, а

выход - с входом -1 счетчика 3 циклов, вход записи которого соединен с выходом первого элемента И-НЕ 15 и входом сброса триггера 7 выдвигаемых разрядов множителя, прямой выход которого соединен с син0 хровходом триггера 8 анализа значащего бита, информационный вход которого соединен с входом логической единицы устройства, первый выход 29 условия ветвления которого соединен с выходом элемента

5 ИЛИ-НЕ21, первый вход которого соединен с выходом переполнения ОБ 1, вход синхронизации которого соединен с выходом первого элемента НЕ 22, шестой выход блока 5

0 синхронизации соединен с первым входом второго элемента И 18, второй вход которого соединен с пятым выходом регистра 4 микрокоманд, первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 24 соединен с выходом

5 триггера 9 частичных произведений, информационный вход которого соединен с выходом младшего разряда информационного выхода операционного блока 1, вход переноса которого соединен с выходом первого

0 элемента 2И-ИЛИ 12, первый вход которого соединен с шестым выходом регистра 4 микрокоманд, седьмой, восьмой и девятый выходы которого соединены с соответствующими входами -1, +1 и входом уста5 новки нулевого адреса формирователя 2 адреса, вход записи которого соединен с выходом второго элемента И 18, а информационный вход - с входом 27 адреса устройства, информационный вход 34 которого

0 соединен с информационным входом счетчика 3 циклов, выход которого соединен с вторым входом элемента ИЛ И-НЕ 21, выход формирователя 2 адреса соединен с адресным входом операционного блока 1, выход

5 младшего разряда множителя которого соединен с вторым выходом 33 условия ветвления устройства и информационным входом триггера 7 выдвигаемых разрядов множителя, синхровход которого соединен

0 с выходом первого элемента НЕ 22 и синх- ровходами триггера 9 частичных произведений и триггера 10 переноса, выход которого соединен с третьим входом первого элемента 2И-ИЛИ 12, второй вход которого соеди5 нен с десятым выходом регистра 4 микрокоманд, одиннадцатый выход которого соединен с первым входом второго элемента 2И-ИЛИ 11 и входом второго элемента НЕ 23, выход которого соединен с четвертым входом второго элемента 2И- ИЛИ 11, второй и третий входы которого

соединены соответственно с выходами триггера 6 знака и триггера 8 анализа значащего бита, вход сброса которого соединен с двенадцатым выходом регистра 4 микрокоманд, тринадцатый выход которого соединен с первым входом третьего элемента И 17, второй вход и выход которого соединены соответственно с выходом элемента ИЛИ 20 и входом первого элемента НЕ 22, первый вход сдвига ОБ 1 соединен с выходом второго элемента 2И-ИЛИ 11, пятый вход которого соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 24, второй вход которого соединен с информационным входом триггера 10 переноса и выходом переноса ОБ 1, второй вход сдвига которого соединен с выходом третьего элемента 2И- ИЛИ 13, первый вход которого соединен с четырнадцатым входом регистра 4 микрокоманд, пятнадцатый выход которого соединен с вторым входом третьего элемента 2И-ИЛИ 13 и входом третьего элемента НЕ 25, выход которого соединен с третьим входом третьего элемента 2И-ИЛИ 13, четвертый вход которого соединен с инверсным выходом триггера 7 выдвигаемых разрядов множителя, шестнадцатый выход регистра 4 микрокоманд соединен с входом микроопераций операционного блока 1,вход частоты блока синхронизации соединен с входом 30 частоты устройства.

Устройство работает следующим образом.

После подачи сигналов на входы сброса и пуска устройства блок 3 синхронизации формирует на выходах восемь тактов (см. фиг. 3). В каждом цикле выполняется микрокоманда, соответствующая содержимому блоков 1-16 (фиг. 2). Перед выполнением умножения двойной разрядности слова в регистры общего назначения (РОН) ОБ 1 заносятся: в РОН поля R2 - старшая часть множителя; в РОН поля Ra+1 - младшая часть множителя; в РОН поля RI - старшая часть множимого; в РОН поля Ri+1 - младшая часть множимого.

В первом цикле младшая часть множителя переписывается из РОН R2+1 в регистр сдвига ОБ 1. На входы управления ОБ 1 поступают соответствующие микрокоманды из РМК 4. На вход синхронизации ОБ 1 поступает сигнал (Т) с выхода первого элемента НЕ 22, во время которого и происходит выполнение микрокоманды.

Во втором цикле в триггер знака записывается знак множимого. В третьем цикле обнуляется регистр младшей части частичных произведений (универсальный регистр 1 (УР1 ОБ 1)).

В четвертом цикле обнуляется регистр старшей части и частичных произведений (УРо ОБ 1) и выполняется первый сдвиг младшей части множителя вправо.

Выдвинутый разряд множителя заносится в триггер множителя.-В счетчик 8 цикла записывается число циклов умножения множимого на младшую часть множителя и сбрасывается триггер 7 множителя. В этом

0 же цикле сбрасывается триггер 8 значащего бита.

В пятом цикле выполняется накопление частичных произведений в регистре младшей части частичных произведений (сложе5 ние содержимого УРч с содержимым регистра младшей части множимого, если младший разряд множителя равен 1 (триггер 7 множителя взведен), или слежение содержимого УР1 с нулем, если младший

0 разряд множителя равен О (триггер 7 множителя сброшен). В этом же цикле выполняется сдвиг содержимого УР-i вправо. Причем на вход старшего разряда УРч ОБ 1 при сдвиге поступает результат суммы по 2 сиг5 нала на выходе триггера 9 частичных произведений и сигнала на выходе Перенос ОБ 1.

В шестом цикле выполняется накопление частичных произведений в регистре

0 старшей части частичных произведений (УРо), сдвиг вправо регистра сдвига ОБ 1.

На вход старшего разряда УРо ОБ 1 при сдвиге поступает сигнал с выхода триггера знака или О, если первый значащий бит в

5 множителе еще не появился. На вход Перенос ОБ 1 при суммировании поступает сигнал с выхода триггера знака или О, если первый значащий бит в множителе еще не появился. На вход Перенос ОБ 1 при сум0 мировании поступает сигнал с выхода триггера 10 переноса. В шестом цикле выполняется вычитание единицы из счетчика 3 цикла и анализ О счетчика 3 цикла, После окончания циклической части умно5 жения в седьмом цикле из регистра старшей части множителя ОБ 1 в регистр сдвига ОБ 1 переписывается старшая часть множителя.

В восьмом цикле выполняется сдвиг

0 старшей части множителя вправо с записью младшего разряда в триггер 7 множителя. Содержимое регистра старшей части в дальнейшем не используется. В счетчик 3 циклов заносится число циклов умножения на стар5 шую часть множителя (п/2-2).

Девятый и десятый циклы аналогичны соответственно пятому и шестому циклам. В одиннадцатом и двенадцатом циклах выполняется умножение на последний значащий разряд множителя и анализ знака

множителя. Если знак равен О, то умножение заканчивается. В УРт ОБ 1 находится младшая часть результата умножения. В УРо ОБ 1 находится старшая часть результата умножения. Если знак множителя равен 1, то в тринадцатом и четырнадцатом блоках выполняется соответственно вычитание содержимого УРт и младшей части множимого и содержимого УРо и старшей части множимого.

В четырнадцатом цикле анализируется значение сигнала на выходе Переполнение ОБ 1. Если переполнение разрядной сетки не было, то умножение заканчивается. Если возникло переполнение разрядной сетки, то это значит, что множимое и множитель были равны -1 (1,000...0). Поэтому в пятнадцатом и шестнадцатом циклах выполняется инверсия младшей и старшей части содержимого регистра множимого с записью результата в УРч и УРо. Формула изобретения Устройство для умножения чисел, содержащее счетчик циклов, регистр микрокоманд, элемент ИЛИ, три элемента И-НЕ, три элемента И, три элемента НЕ, элемент ИЛИ- НЕ, первый и второй элементы 2И-ИЛИ, триггер знака, триггер выдвигаемых разрядов множителя, триггер анализа значащего бита, блок синхронизации и операционный блок, информационные входы и выходы которого соединены соответственно с инфор- мационными входами и выходами устройства, входы микрокоманд, пуска и сброса которого соединены соответственно с информационным входом регистра микрокоманд и входами пуска и сброса блока син- хронизации, первый выход которого соединен с синхровходом регистра микрокоманд, первый выход которого соединен с первым входом первого элемента И-НЕ, второй вход которого соединен с вторым выходом синхронизации, выходы с третьего по пятый которого соединен ы с соответствующими входами элемента ИЛИ, выход которого соединен с первым входом второго элемента И-НЕ, второй вход которого соединен с вторым выходом регистра микрокоманд, а выход - с входом чтения операционного блока, выход знака которого соединен с информационным входом триггера знака, синхровход которого соединен с выходом третьего элемента И-НЕ, первый вход которого соединен с третьим выходом регистра микрокоманд, а второй вход - с входом первого элемента НЕ и первым входом первого элемента И, второй вход которого соединен с четвертым выходом микрокоманд, а выход- с входом -1 счетчика циклов, вход записи которого соединен

с выходом первого элемента И-НЕ и входом сброса триггера выдвигаемых разрядов множителя, прямой выход которого соединен с синхровходом триггера анализа значащего бита, информационный вход которого соединен с входом логической единицы устройства, первый выход условия ветвления которого соединен с выходом элемента ИЛ И-НЕ, первый вход которого

0 соединен с выходом переполнения операционного блока, вход синхронизации которого соединен с выходом первого элемента НЕ, шестой выход блока синхронизации соединен с первым входом второго элемента

5 И, второй вход которого соединен с пятым выходом регистра микрокоманд, отличающееся тем, что, с целью расширения функциональных возможностей за счет умножения 2 n-разрядных чисел на п-разряд0 ном оборудовании, в него введены формирователь адреса, триггер переноса, триггер частичных произведений, третий элемент 2И-ИЛИ и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен

5 с выходом триггера частичных произведений, информационный вход которого соединен с выходом младшего разряда информационного выхода операционного блока, вход переноса которого соединен с

0 выходом элемента 2И-ИЛИ, первый вход первого элемента И которого соединен с шестым выходом регистра микрокоманд, седьмой, восьмой и девятый выходы которого соединены соответственно с входами 5 1, +1, и входом установки нулевого адреса формирователя адреса, вход записи которого соединен с выходом второго элемента И, а информационный вход- с входом адреса устройства, информационный вход

0 которого соединен с информационным входом счетчика циклов, выход которого соединен с вторым входом элемента ИЛИ-НЕ, выход формирователя адреса соединен с адресным входом операционного блока, вы5 ход младшего разряда множителя которого соединен с вторым выходом условия ветвления устройства и информационным входом триггера выдвигаемых разрядов множителя, синхровход которого соединен с выхо0 дом первого элемента НЕ и синхровходами триггера частичных произведений и триггера переноса, выход которого соединен с первым входом второго элемента И первого элемента 2И-ИЛИ, второй вход второго эле5 мента И которого соединен с десятым выходом регистра микрокоманд, одиннадцатый выход которого соединен с первым входом первого элемента И второго элемента 2И- ИЛИ и входом второго элемента НЕ, выход которого соединен с первым входом второго

элемента И второго элемента 2И-ИЛИ, второй и третий входы второго элемента И которого соединены соответственно с выходами триггера знака и триггера анализа значащего бита, вход сброса которого соединен с двенадцатым выходом регистра микрокоманд, тринадцатый выход которого соединен с первым входом третьего элемента И, второй вход и выход которого соединены соответственно с выходом элемента ИЛИ и входом первого элемента НЕ, первый вход сдвига операционного блока соединен с выходом второго элемента 2И- ИЛИ, второй вход первого элемента И которого соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с информационным входом триггера переноса и выходом переноса

2

М

операционного блока, второй вход сдвига которого соединен с выходом третьего элемента 2И-ИЛИ, первый вход первого элемента И которого соединен с

четырнадцатым выходом регистра микрокоманд, пятнадцатый выход которого соединен с первым входом второго элемента И третьего элемента 2И-ИЛИ и входом третьего элемента НЕ, выход которого соединен

с вторым входом первого элемента И третьего элемента 2И-ИЛИ, второй вход второго элемента И которого соединен с инверсным выходом триггера выдвигаемых разрядов множителя, шестнадцатый выход регистра

микрокоманд соединен с входом микроопераций операционного блока, вход частоты блока синхронизации соединен с входом частоты устройства.

31 32

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения чисел с фиксированной запятой | 1989 |

|

SU1758644A1 |

| Процессор для обработки массивов данных | 1982 |

|

SU1381532A1 |

| УСКОРЕННЫЙ УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2006 |

|

RU2322688C2 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Устройство для умножения | 1975 |

|

SU640292A1 |

| Микропроцессорное устройство для цифрового преобразования координат | 1982 |

|

SU1104523A1 |

| Устройство для сопряжения с микроЭВМ | 1986 |

|

SU1709322A1 |

| ОПЕРАЦИОННЫЙ БЛОК | 1993 |

|

RU2034330C1 |

| Устройство для умножения | 1984 |

|

SU1176325A1 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств процессоров. Цель изобретения - расширение функциональных возможностей за счет умножения 2п-разрядных чисел на п-разряд- ном оборудовании. Новым в устройстве для умножения чисел, содержащем операционный блок, счетчик циклов, регистр микрокоманд, блок синхронизации, триггер знака, триггер выдвигаемых разрядов множителя, триггер значащего бита, первый и второй элементы 2И-ИЛИ,.три элемента И-НЕ, три элемента И, элемент ИЛИ, элемент ИЛИ- НЕ, три элемента НЕ, является введение формирователя адреса, триггера частичных произведений, триггера переноса, третьего элемента 2И-ИЛИ и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с соответствующими связями. 4 ил.

фие. 2

| Устройство для умножения | 1985 |

|

SU1290301A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1558205, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-06-15—Публикация

1990-02-14—Подача