(54) КВАДРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое устройство для воспроизве-дЕНия фуНКций | 1979 |

|

SU809126A1 |

| Устройство для воспроизведения функции @ @ | 1982 |

|

SU1061137A1 |

| Устройство для умножения 12N-разрядных двоичных чисел | 1988 |

|

SU1589271A1 |

| Гибридный функциональный преобразователь | 1987 |

|

SU1464180A1 |

| Устройство для умножения | 1978 |

|

SU769540A1 |

| Интерполятор функций двух аргументов | 1984 |

|

SU1247893A1 |

| Устройство для вычисления синуса | 1986 |

|

SU1319025A1 |

| Устройство для вычисления функций синуса и косинуса | 1977 |

|

SU723583A1 |

| Конвейерное устройство для вычисления тригонометрических функций | 1984 |

|

SU1168931A1 |

| Устройство для цифровой фильтрации | 1985 |

|

SU1381541A1 |

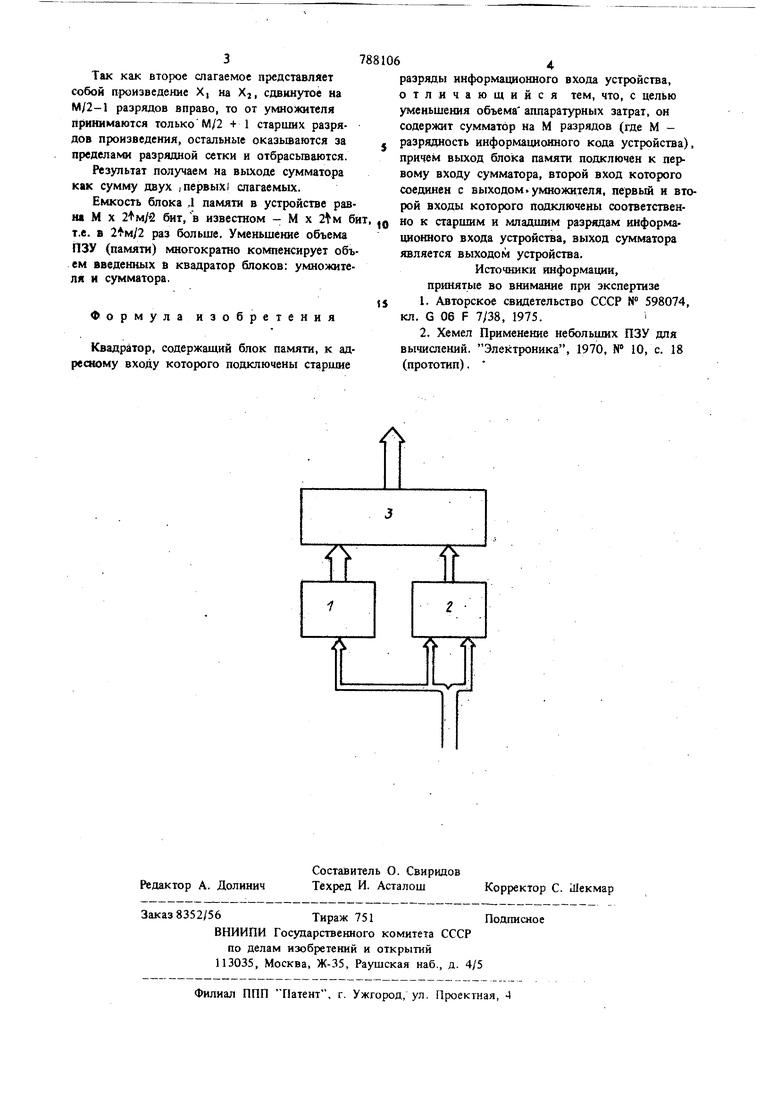

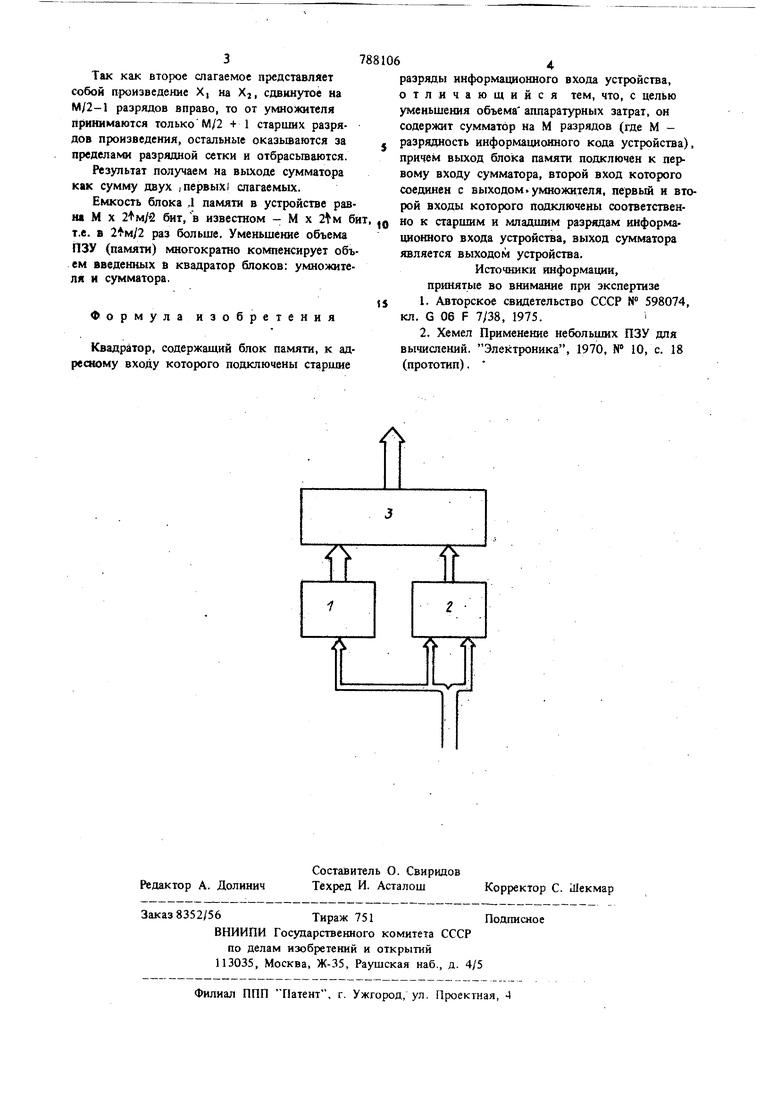

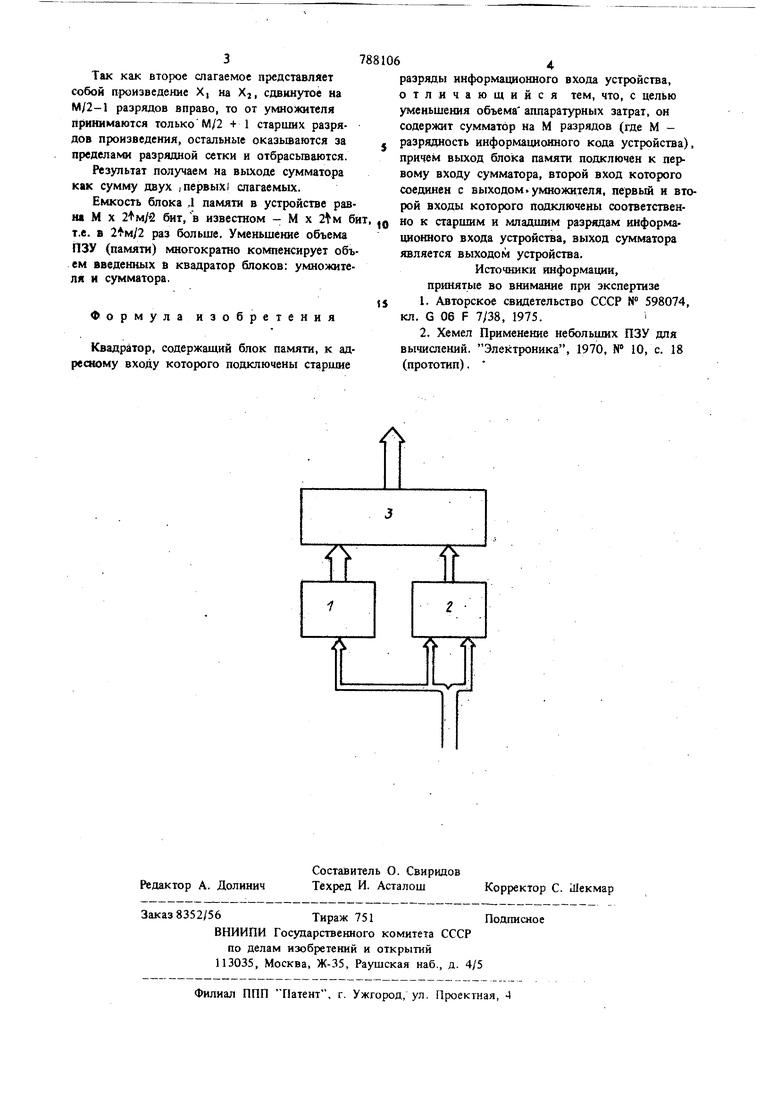

Изобретение относится к вычислительной технике и может использоваться в процессорах вычислительных систем. . Известен квадратор, содержащий регистр множимого, сдвигающий регистр множителя, накапливающий регистр частишых произведений, логические схемы управления 1. Недостатком известного устройства является низкое быстродействие. Наиболее близким по технической сущности к предложенному является квадратор, содержа щий блок памяти, к адресному входу которого подключены старшие разряды информационного входа устройства. (2). Недостатком устройства является значительный объем, оборудования. Цель изобретения - уменьшение объема аппаратуры. Поставленная цель достигается тем, что ква рато.р, содержащий блок памяти, к адресному входу которого подключены старщие разряды информационного входа устройства, дополнительно содержит сумматор на М разрядов (где М - разрядность информационного кода устройства), причем выход блока памяти подключен к первому входу сумматора, второй вход которюго соединен с выходом умножителя, первый и второй входы которого подключены соответственно к старщим и младщим разрядам информационного входа устройства, выход сумматора является выходом устройства. На чертеже представлена функциональная схема предлагаемого квадратора. Устройство Содержит блок 1 памяти, умножитель 2, сумматор 3. Квадратор работает следующим образом. Квадратор вырабатьгаает квадрат М-разрядного числа X 1, округленный до М разрядов. При представлении X в виде X X, + X,, где X, 1 и Xj 1 - числа, полученные соответственно из старщих и младщих разрядов исходного числа, имеем Х Xj-h ,Х, + 2- Х2. Первое слагаемое в этом выражении получаем с помощью блока памяти, второе - на умножителе, третье - не:учитьшаем, так как оно меньше цены младшего разряда. 3 Так как второе слагаемое представляет собой произведение X, на Xj, сдвинутое на М/2-1 разрядов вправо, то от умножителя при1тмаются только М/2 + 1 старишх разрядов произведения, остальные оказываются за пределами разрядной сетки и отбрасываются. Результат получаем на выходе сумматора как сумму двух /первых слагаемых. Емкость блока .1 памяти в устройстве равна М х бит,в известном - М х би т.е. в раз больше. Уменьшение объема ПЗУ (памяти) многократно компенсирует объем введенных & квадратор блоков: умножителя и сумматора. Формула изобретения Квадратор, содержащий блок памяти, к адресному входу которого подключены старшие разряды информационного входа устройства, отличающийся тем, что, с цепью уменьшения объема аппаратурных затрат, он содержит сумматор на М разрядов (где М разрядность информационного кода устройства), причем выход блока памяти подключен к первому входу сумматора, второй вход которого соединен с выходом .умножителя, первый и второй входы которого подключены соответственно к старшим и младшим разрядам информационного входа устройства, выход сумматора является выходом устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 598074, кл. G 06 F 7/38, 1975. 2.Хемел Применение небольших ПЗУ для вычислений. Электроника, 1970, № 10, с. 18 (прототип).

Авторы

Даты

1980-12-15—Публикация

1979-01-16—Подача