4:: О СП

О О5

тирования из блока 2 памяти тестов считываются слова. .Слово, определяющее направление включения двунаправленных выводов контролируемого блока, принимается в коммутатор 7; .слово, .определяющее количество тестовых слов до смены направления включения выво дов контролируемого блока, принимается в счетчик 5, тестовые слова принимаются в регистр 4 и через коммутатор 7 поступают на входы контролируемого блока- 1 1 . С выходов контролируе5060

мого блока 11

реакции через коммутатор 7 принимаются в регистр 6 реакций, с выходов которого записываются в блок 10 памяти реакций. Наличие в устройстве счетчика 5, элементов 8, 9, 12, 13, 15, триггера 14 и введение в последовательность тестовых слов пар управляющих слов позволяют изменять направление включения выводов контролируемого блока при каждом считывании из блока 2 памяти тестов пары управляющих слов. 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ТЕСТОВОГО КОНТРОЛЯ | 2014 |

|

RU2565474C1 |

| Устройство тестового контроля | 1989 |

|

SU1691842A1 |

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

| Генератор тестов | 1989 |

|

SU1661770A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1290333A1 |

| Устройство для контроля и диагностики логических блоков | 1985 |

|

SU1302284A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1456996A1 |

| Устройство для тестового контроля цифровых узлов | 1987 |

|

SU1425682A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1545222A1 |

Изобретение относится к вычислительной технике и может быть использовано в аппаратуре контроля и диагностирования-цифровых узлов. Цель изобретения - расширение .области применения за счет реализации возможности .генерации тестов для тестирования блоков, имеющих двунаправленные входы/выходы. Генер-атор содержит блок 2 памяти тестов для хранения теста, блок 10 памяти реакций для регистрации реакций контролируемого блока, регистр 4 для хранения тестовых ,слов, считанных из блока 2 памяти тестов, регистр 6 реакций для приема реакций, записываемых в блок 10 памяти реакций, коммутатор 7 для определения направления включения выводов контролируемого узла, счетчик 3 адреса для адресации блока 2 памяти тестов и блока 10 памяти реакций, элемент 1 задержки для форм и- рования сигнала выборки, счетчик 5 для отсчета тестовьпс слов между сменами направления включения выводов контролируемого блока, элемент НЕ 9, элементы И 8, 12, 13, триггер 14, элемент ИЛИ 15 для распределения счи- тываемых из блока 2 памяти тестов слов между регистром 4, коммутатором 7 и счетчиком 5. В- процессе тесо 9 (Л

.Изобретение относится к автоматике , вычислитедьнсй технике и может быть использовано для контроля и диагностики цифровых блоков.

Цель изобретения - расширение области применения за счет реализации возможности генерации тестов для тес- тировайия блоков, имеющих двунаправленные входы/выходы

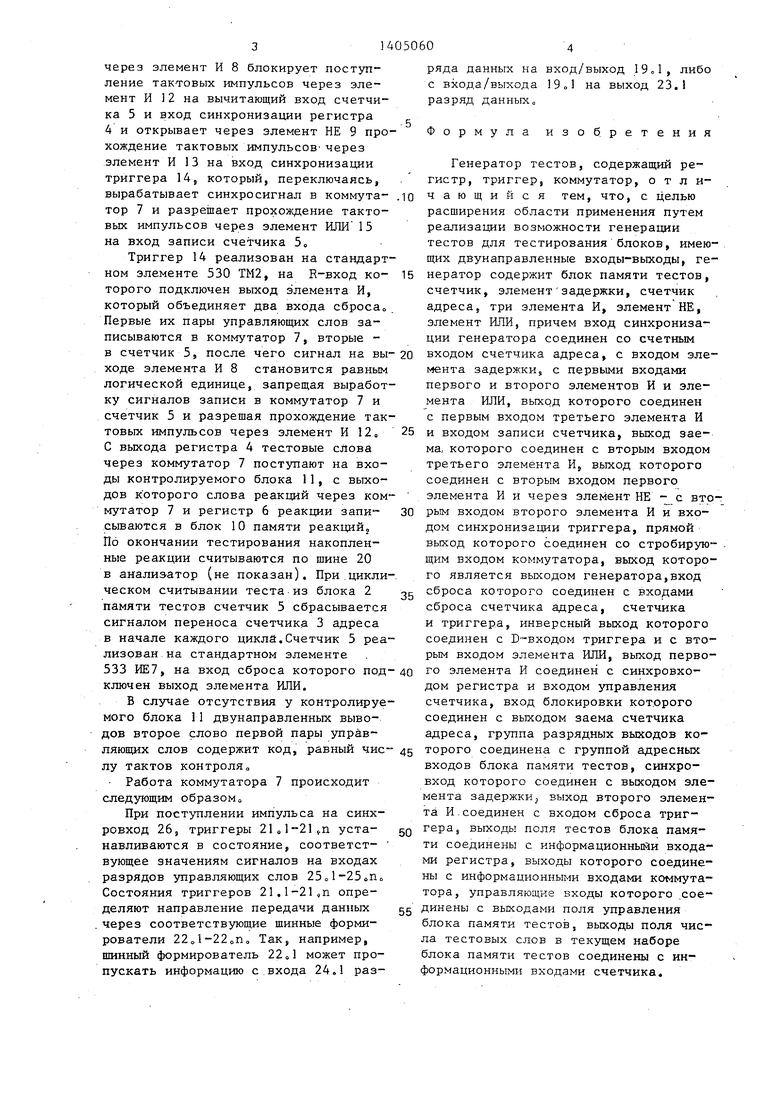

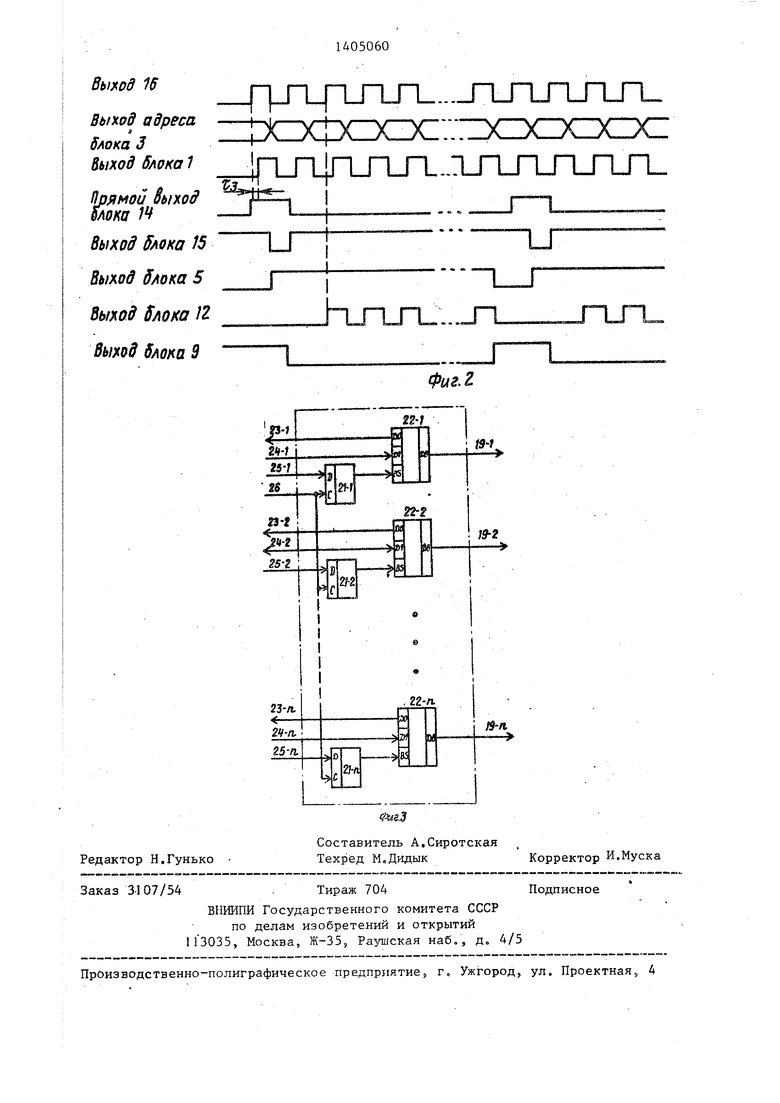

На фиг.1 показана структурная схема генератора; на фиг о 2 временная диаграмма; на фиг. 3 - коммутатор.

Генератор содержит элемент 1 за- .держки, блок 2 памяти тестов, счетчик 3 адреса, регистр 4, счетчик 5, регистр 6 реакций, коммутатор 7, элемент И 8, элемент НЕ 9j блок 10 памяти реакций, контролируемый блок 11, элементы И 12 и 13, триггер 14„ элемент ИЛИ 15, синхровход 16, щину 17 вэода тестов в блок памяти тестов, вход 18 сброса, выходную шину 19, информационный выход 20 (не показан) реакции контролируемого блока )1„

Коммутатор 7 (фиГоЗ) содержит триггеры 21о1-21оП5 шинные формирователи 22„1-22.п, выходы 23о1-23„п разрядов с данных, входы 24„1-24оП раз рядов данных, входы 25о1-25оП разрядов управляющих слов, синхровход 26 приема управляющих слов (п - число входов/выходов контролируемого бло ка) о .

Устройство работает следующим образом.

Контролируемый блок 1 1 имеет п выв о до в 5.каждый из которых может быть входным и выходным о Кроме того,

m выводов ( п) блока 1 1 Двунаправленные,, Для контроля блока 11 с помощью одного теста необходимо в процессе тестирования менять нап- равление включения выводов путем управления коммутатором 7.Это управ ление осуществляется с помощью управляющих слов, записанных наряду с тестовыми ,словами в блоке 2 памяти тес

0 тов. Последовательность слов, считываемых из блока 2 памяти тестов, начинается с двух управляющих слов Первое слово указывает входы и выходы блока 11J второе слово - количе5 ство тестовых слов,, которые будут считаны из блока 2 памяти тестов до смены направления включения выводов , m (до следующей пары управляющих слов) Считывание из блока 2 памяти тестов происходит непрерывно по синхросигналам шины 16,

В исходном состоянии счетчик 3 адреса, счетчик 5 и триггер 14 сброшены сигналом сброса, поступающим на вход 18 сброса.

По шине 17 в блок 2 памяти записан тест о При поступлении тактовых импульсов с входа 16 на счетный вход счетчика 3 адреса (счетчик

0 работает по заднему фронту тактовых импульсов) и на вход элемента 1 задержки (элемент задержки формирует сигнал выборки, задержанный относительно тактовых импульсов на время

5 т) из блока 2 памяти тестов считываются тестовые слова При считывании управляющих слов выход заема счетчика 5 равен логическому нулю и

0

5

через элемент И 8 блокирует поступление тактовых импульсов через элемент И 12 на вычитающий вход счетчика 5 и вход синхронизации регистра 4 и открывает через элемент НЕ 9 прохождение тактовых импульсов через элемент И 13 на вход синхронизации триггера 14, который, переключаясь, вырабатывает синхросигнал в коммутатор 7 и разрешает прохождение тактовых импульсов через элемент ИЛИ 15 на вход записи счетчика 5„

Триггер 14 реализован на стандартном элементе 530 ТМ2, на R-вход которого подключен выход элемента И, который объединяет два входа сброса. Первые их пары управляющих слов записываются в коммутатор 7, вторые - в счетчик 5, после чего сигнал на выходе элемента И 8 становится равным логической единице, запрещая выработку сигналов записи в коммутатор 7 и счетчик 5 и разрешая прохождение тактовых импульсов через элемент И 12. С выхода регистра 4 тестовые сЛова через коммутатор 7 поступают на входы контролируемого блока 11, с выходов к оторого слова реакций через коммутатор 7 и регистр 6 реакции записываются в блок 10 памяти реакций. По окончании тестирования накопленные реакции считываются по шине 20 в анализатор (не показан). При циклическом считывании теста.из блока 2 памяти тестов счетчик 5 сбрасывается сигналом переноса счетчика 3 адреса в начале каждого цикла.Счетчик 5 реализован на стандартном элементе 533 ИЕ7, на вход сброса которого подключей выход элемента ИЛИ,

В случае отсутствия у контролируемого блока 11 двунаправленных выводов второе слово первой пары управляющих слов содержит код, равный чис- лу тактов контроля Работа коммутатора 7 происходит следующим образомо

При поступлении импульса на синх- ровход 26, триггеры 21„1-215.п уста

навливаются в состояние, соответствующее значениям сигналов на входах разрядов управляющих слов 25о1-25(,По Состояния триггеров 21,1-21,п определяют направление передачи данных через соответствующие шинные формирователи 22Л-22оПо Так, например, шинный формирователь 22о 1 может пропускать информацию с входа 24,1 раз5060

ряда данных

с входа/выхода разряд данных

на вход/выход 19

19 о 1 на выход 23,1

1, либо

0

5

5

0 0

5

0

5

0

5

Формула изобретения

Генератор тестов, содержащий регистр, триггер, коммутатор, отличающийся тем, что, с целью расширения области применения путем реализации возможности генерации тестов для тестирования блоков, имеющих двунаправленные входы-выходы, генератор содержит блок памяти тестов, счетчик, элемент задержки, счетчик адреса, три элемента И, элемент НЕ, элемент ИЛИ, причем вход синхронизации генератора соединен со счетным входом счетчика адреса, с входом элемента задержки, с первыми входами первого и второго элементов И и элемента ИЛИ, выход которого соединен с первым входом третьего элемента И и входом записи счетчика, выход зае- ма, которого соединен с вторым входом третьего элемента И, выход которого соединен с вторым входом первого элемента И и через элемент НЕ - с вторым входом второго элемента И и входом синхронизации триггера, прямой выход которого соединен со стробирую- . щим входом коммутатора, вькод которого является выходом генератора,вход сброса которого соединен с входами сброса счетчика адреса, счетчика и триггера, инверсный выход которого соединен с Б-входом триггера и с вторым входом элемента ИЛИ, выход первого элемента И соединен с синхровхо- дом регистра и входом управления счетчика, вход блокировки которого соединен с выходом заема счетчика адреса, группа разрядных выходов которого соединена с группой адресных входов блока памяти тестов, синхро- вход которого соединен с выходом элемента задержкиJ выход второго элемента И.соединен с входом сброса триггера, выходы поля тестов блока памяти соединены с информационныйи входами регистра, выходы которого соединены с информационными входами коммутатора, управляющие входы которого .соединены с выходами поля управления блока памяти тестов, выходы поля числа тестовых слов в текущем наборе блока памяти тестов соединены с информационными входами счетчика.

.

-л1/- г -S/-У П |П П П

U

hLTTJ-u:

Фи,1

| Устройство для формирования тестов дискретных автоматов | 1975 |

|

SU642711A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-06-23—Публикация

1986-11-11—Подача