Изобретение относится к вычислительной технике и может быть использовано при тестировании цифровой аппаратуры.

Цель изобретения - упрощение генератора.

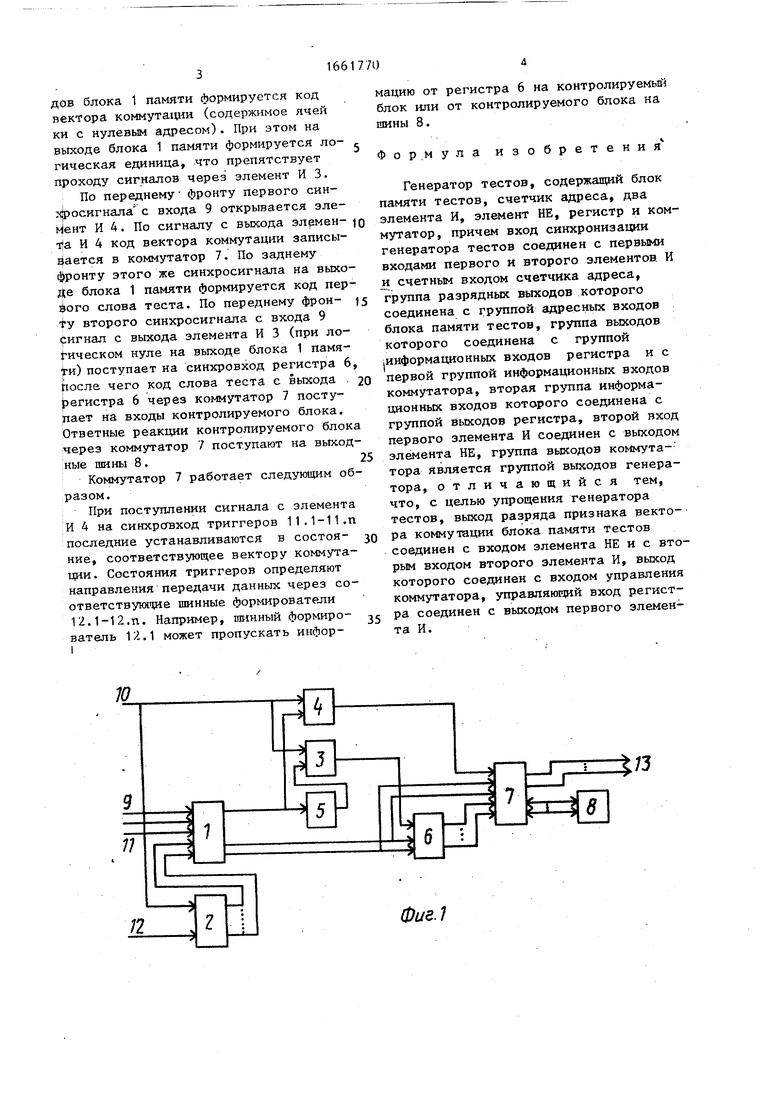

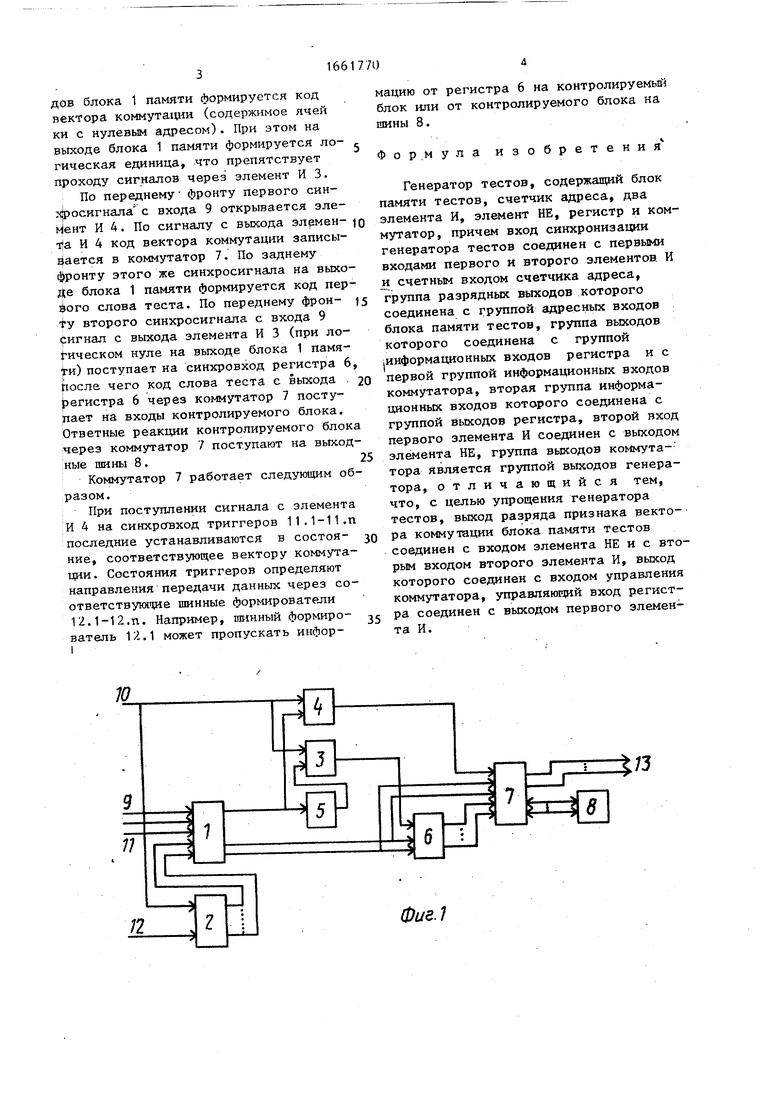

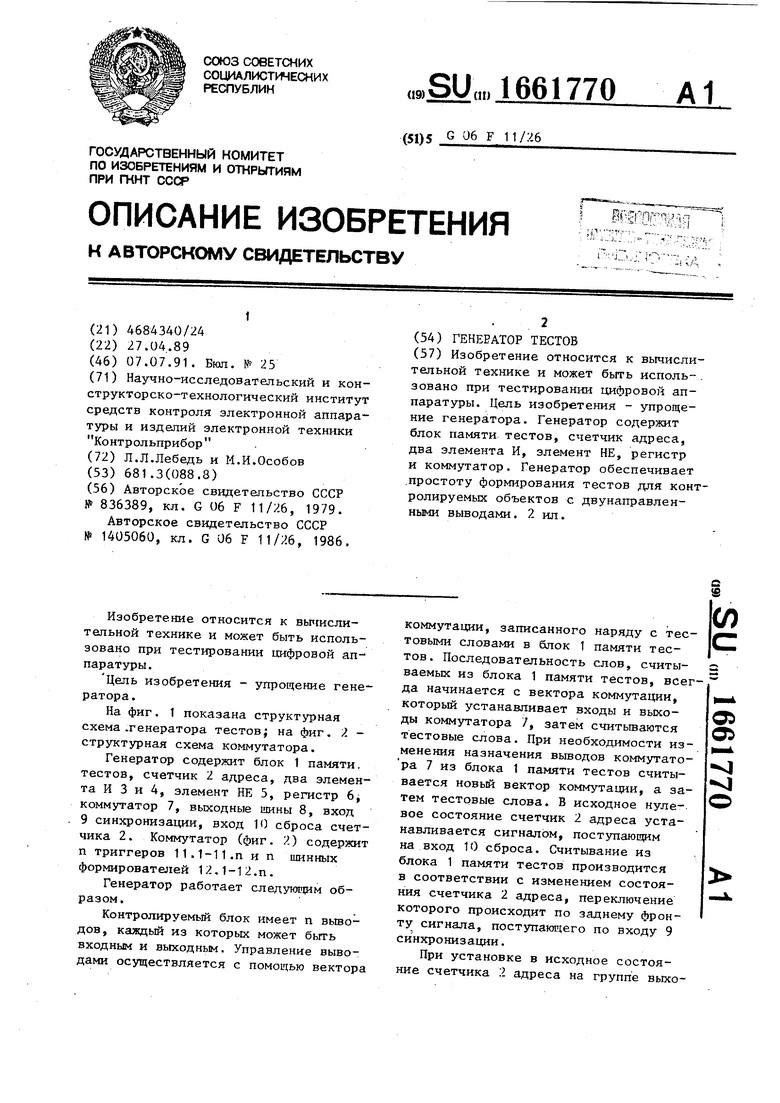

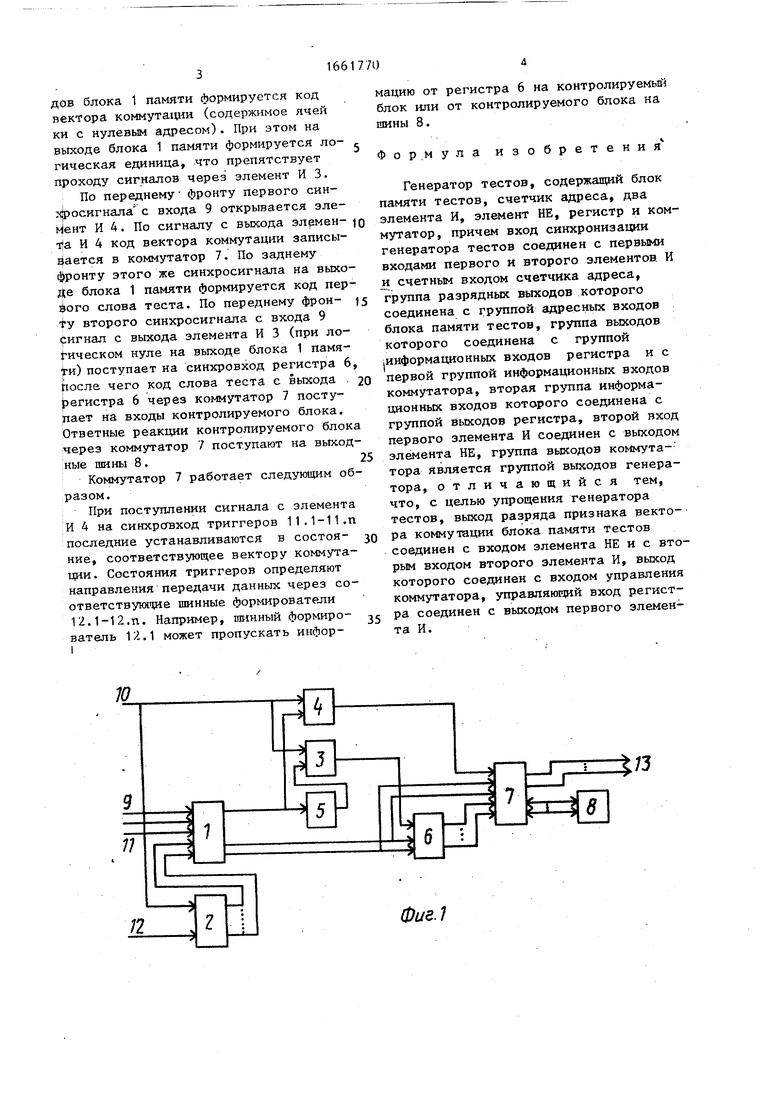

На фиг. 1 показана структурная схема .генератора тестов; на фиг. 2 - структурная схема коммутатора.

Генератор содержит блок 1 памяти, тестов, счетчик 2 адреса, два элемента И 3 и 4, элемент НЕ 5, регистр 6, коммутатор 7, выходные шины 8, вход 9 синхронизации, вход 10 сброса счетчика 2. Коммутатор (фиг. 2) содержит п триггеров 11.1-11.ri и п шинных формирователей 12.1-12.п.

Генератор работает следующим образом.

Контролируемый блок имеет п выводов, каждый из которых может быть входным и выходным. Управление выводами осуществляется с помощью вектора

коммутации, записанного наряду с тестовыми словами в блок 1 памяти тестов. Последовательность слов, считываемых из блока 1 памяти тестов, всегда начинается с вектора коммутации, который устанавливает входы и выходы коммутатора /, затем считываются тестовые слова. При необходимости изменения назначения выводов коммутатора 7 из блока 1 памяти тестов считывается новый вектор коммутации, а затем тестовые слова. В исходное нулевое состояние счетчик 2 адреса устанавливается сигналом, поступающим на вход 10 сброса. Считывание из блока 1 памяти тестов производится в соответствии с изменением состояния счетчика 2 адреса, переключение которого происходит по заднему фронту сигнала, поступающего по входу 9 синхронизации.

При установке в исходное состояние счетчика 2 адреса на группе выхо(Л

оэ

оэ

sj sj

дов блока 1 памяти формируется код вектора коммутации (содержимое ячей кй с нулевым адресом). При этом на выходе блока 1 памяти формируется ло- гическая единица, что препятствует проходу сигналов через элемент И 3.

По переднему фронту первого синхросигнала с входа 9 открывается эле- йент И 4. По сигналу с выхода элемен- JQ tfa И 4 код вектора коммутации записывается в коммутатор 7. По заднему фронту этого же синхросигнала на выходе блока 1 памяти формируется код первого слова теста. По переднему фрон- 15 ty второго синхросигнала с входа 9 сигнал с выхода элемента И 3 (при ло- ическом нуле на выходе блока 1 памяти) поступает на синхровход регистра 6, после, чего код слова теста с выхода 2 регистра 6 через коммутатор 7 поступает на входы контролируемого блока. Ответные реакции контролируемого блока через коммутатор 7 поступают на выходные шины 8.2

Коммутатор 7 работает следующим образом.

При поступлении сигнала с элемента И 4 на синхрсгвход триггеров 11.1-11.ti последние устанавливаются в состоя3

ние, соответствующее вектору коммутации. Состояния триггеров определяют направления передачи данных через соответствующие шинные формирователи 12.1-12.п. Например, шинный формир о- ватель 12.1 может пропускать инфор

5

0

5

мацию от регистра 6 на контролируемый блок или от контролируемого блока на шины 8.

Формула изобретения

Генератор тестов, содержащий блок памяти тестов, счетчик адреса, два элемента И, элемент НЕ, регистр и коммутатор, причем вход синхронизации генератора тестов соединен с первыми входами первого и второго элементов И и счетным входом счетчика адреса, группа разрядных выходов которого соединена с группой адресных входов блока памяти тестов, группа выходов которого соединена с группой .информационных входов регистра и с первой группой информационных входов коммутатора, вторая группа информационных входов которого соединена с группой выходов регистра, второй вход первого элемента И соединен с выходом элемента НЕ, группа выходов коммутатора является группой выходов генератора, отличающийся тем, что, с целью упрощения генератора тестов, выход разряда признака вектора коммутации блока памяти тестов соединен с входом элемента НЕ и с вторым входом второго элемента И, выход которого соединен с входом управления коммутатора, управляющий вход регистра соединен с выходом первого элемента И.

«Ъ

И

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

| Устройство для тестового контроля цифровых блоков | 1985 |

|

SU1312577A1 |

| Генератор тестов | 1986 |

|

SU1405060A1 |

| Устройство тестового контроля цифровых блоков | 1985 |

|

SU1315982A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1988 |

|

SU1667075A1 |

| Устройство для поиска дефектов дискретных блоков | 1990 |

|

SU1714610A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1989 |

|

SU1700557A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1986 |

|

SU1376087A1 |

Изобретение относится к вычислительной технике и может быть использовано при тестировании цифровой аппаратуры. Цель изобретения - упрощение генератора. Генератор содержит блок памяти тестов, счетчик адреса, два элемента И, элемент НЕ, регистр и коммутатор. Генератор обеспечивает простоту формирования тестов для контролируемых объектов с двунаправленными выводами. 2 ил.

Фиг. Z ,

| Герметичный центробежный электро-HACOC | 1979 |

|

SU836389A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Генератор тестов | 1986 |

|

SU1405060A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-07-07—Публикация

1989-04-27—Подача