Изобретение относится к цифровой вычислительной технике, в частности к устройствам для проверки узлов цифровых вычислительных машин, а также микропроцессоров.

Цель изобретения - расширение области применения за счет обеспечения возможности контроля процессорных элементов, а также повышение достоверности контроля за счет выявления ситуаций короткое замыкание и обрыв.

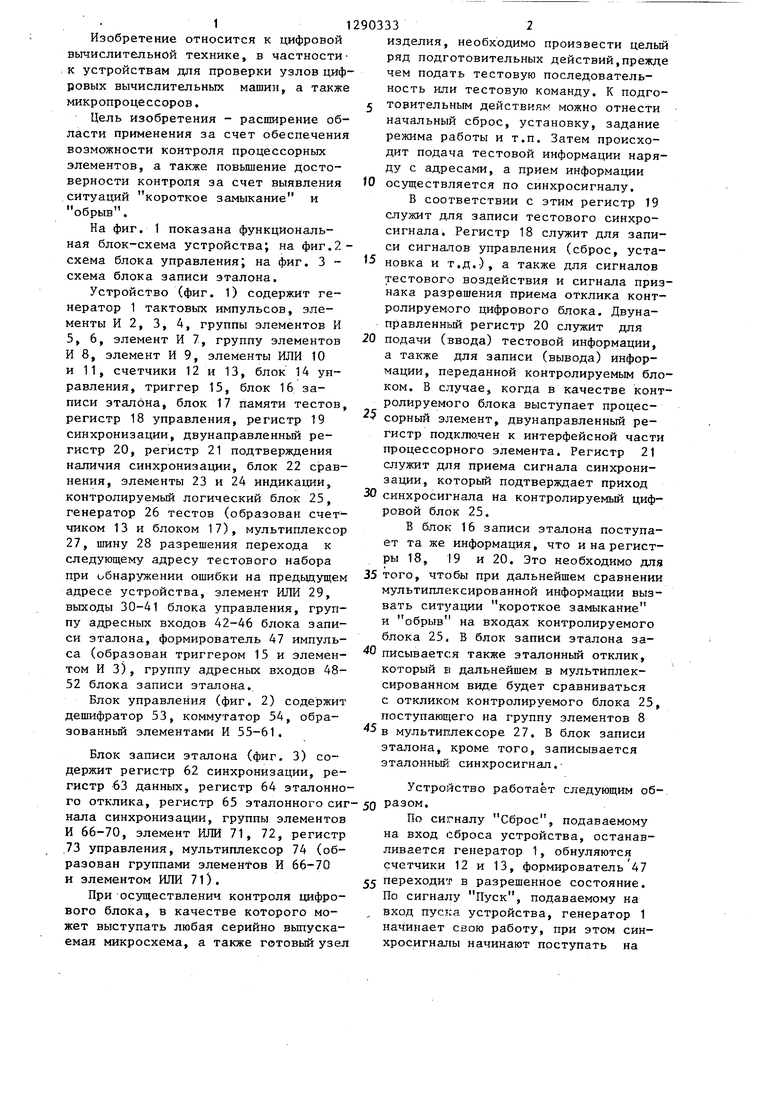

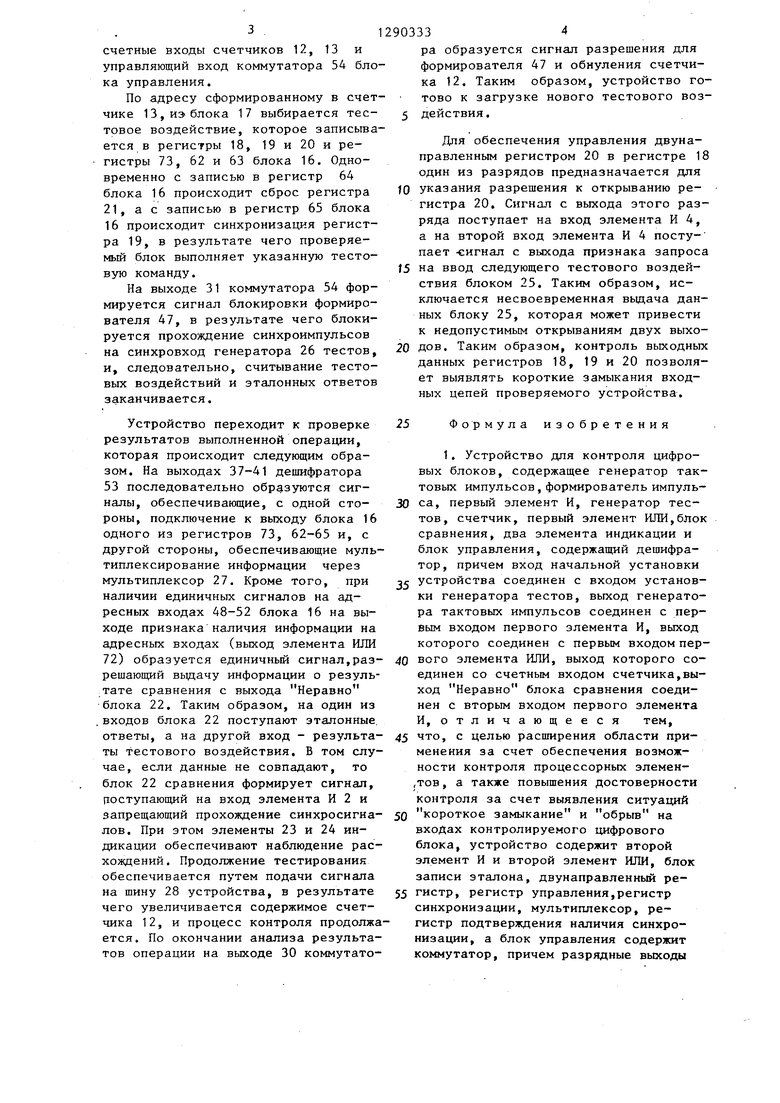

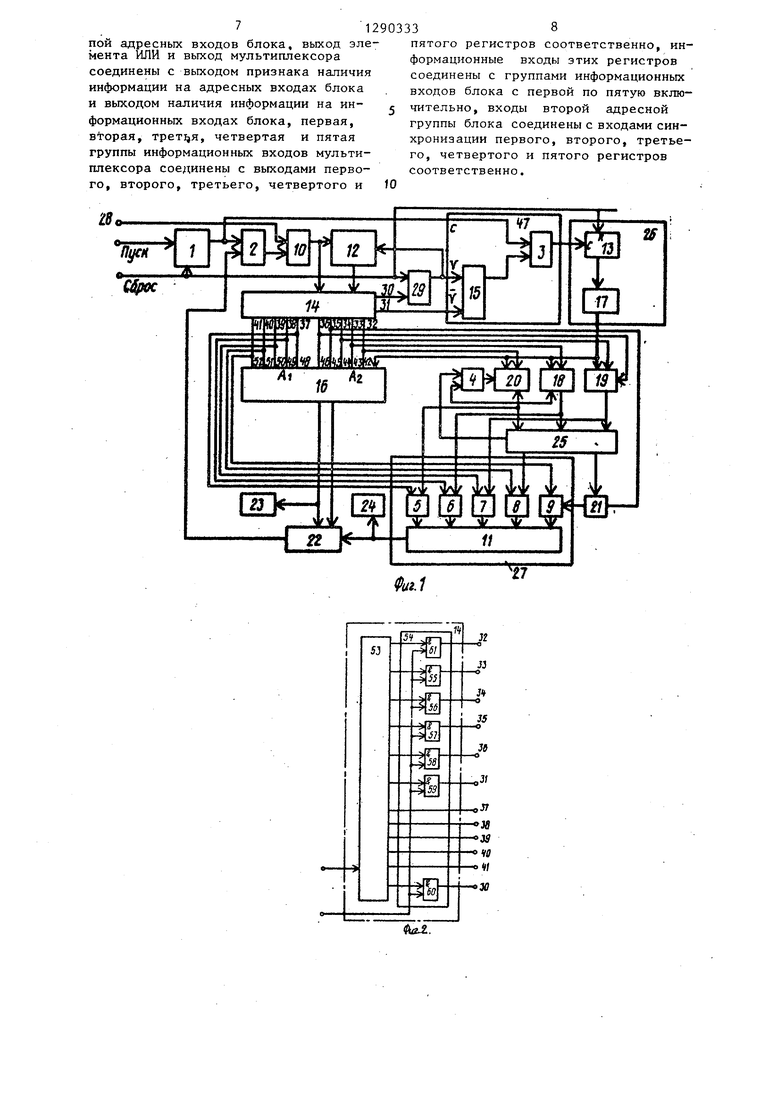

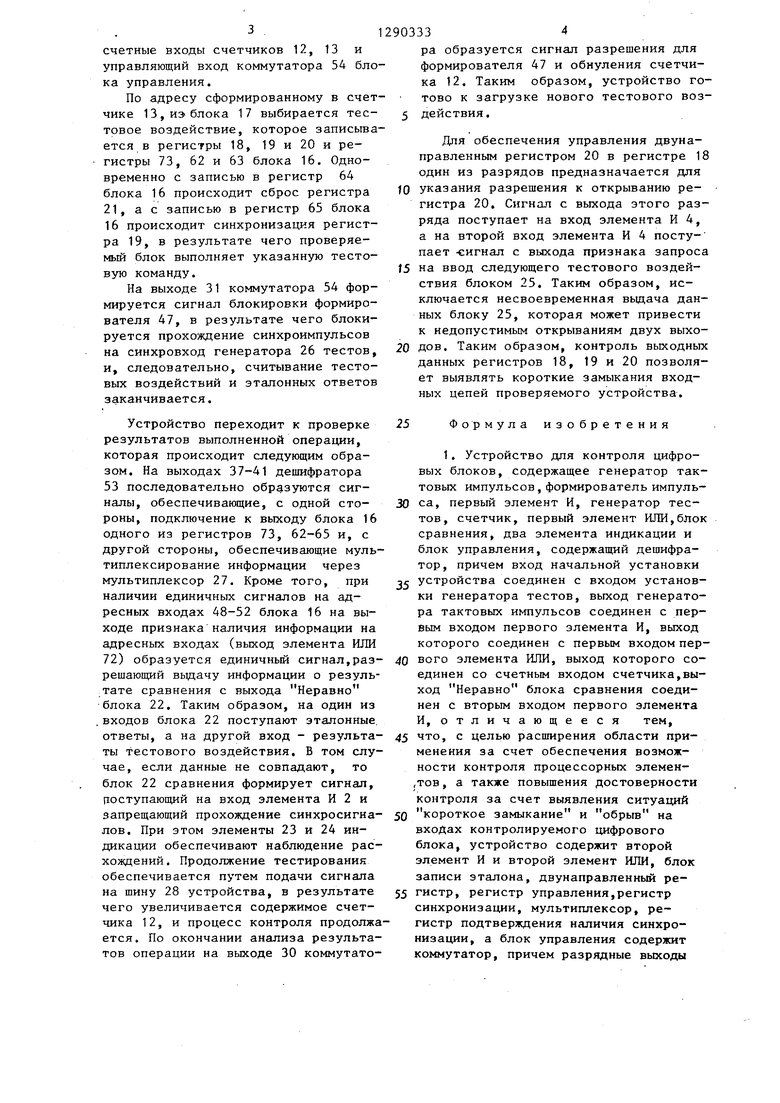

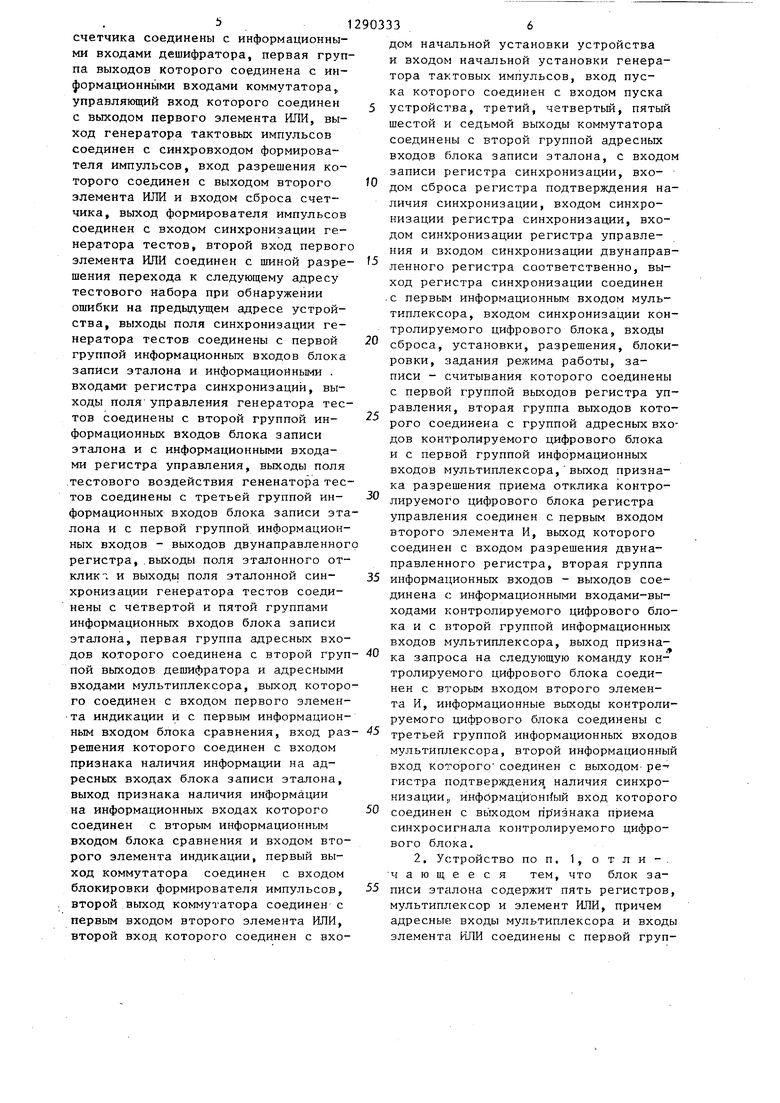

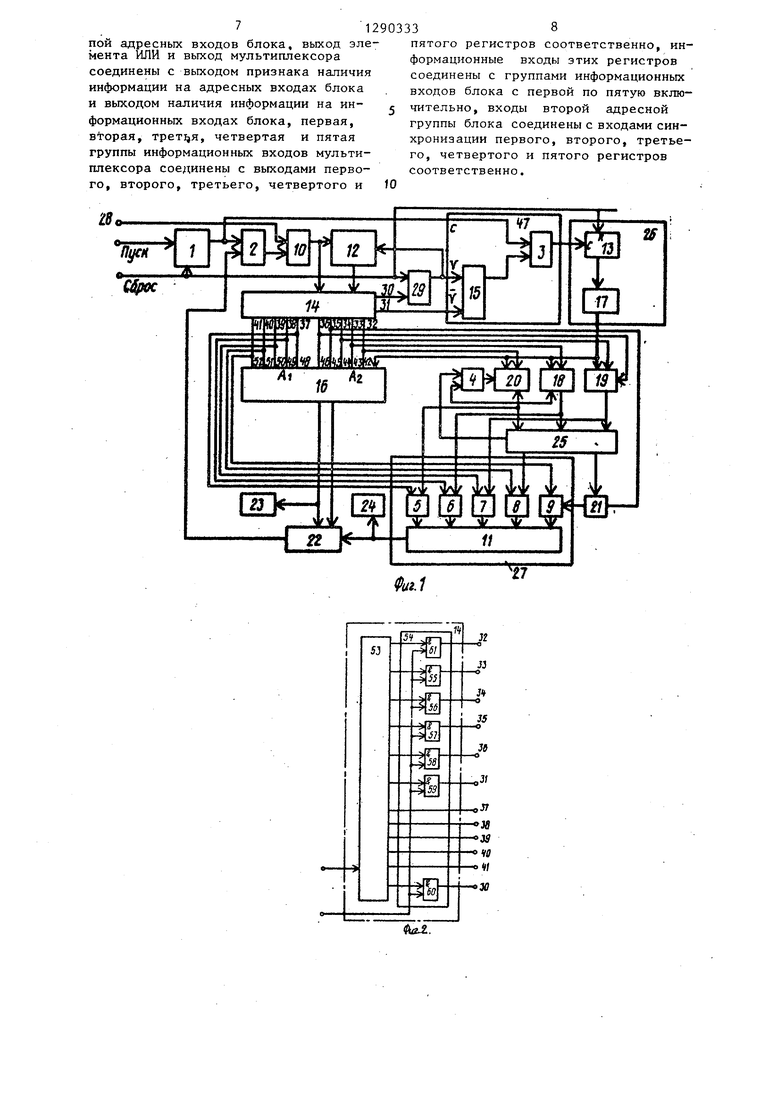

На фиг. 1 показана функциональная блок-схема устройства; на фиг.2- схема блока управленияJ на фиг. 3 - схема блока записи эталона.

Устройство (фиг. 1) содержит генератор 1 тактовых импульсов, элементы И 2, 3, 4, группы элементов И 5, 6, элемент И 7, группу элементов И 8, элемент И 9, элементы ИЛИ 10 и 11, счетчики 12 и 13, блок 14 управления, триггер 15, блок 16 записи эталона, блок 17 памяти тестов, регистр 18 управления, регистр 19 синхронизации, двунаправленный регистр 20, регистр 21 подтверждения наличия синхронизации, блок 22 сравнения, элементы 23 и 24 индикации, контролируемый логический блок 25, генератор 26 тестов (образован счетчиком 13 и блоком 17), мультиплексор 27, шину 28 разрешения перехода к следующему адресу тестового набора при обнаружении ошибки на предыдущем адресе устройства, элемент ИЛИ 29, выходы 30-41 блока управления, группу адресных входов 42-46 блока запи35 того, чтобы при дальнейшем сравнен мультиплексированной информации вы вать ситуации короткое замыкание и обрыв на входах контролируемог блока 25, Б блок записи эталона за

си эталона, формирователь 47 импульса (образован триггером 15 и элемен- Описывается также эталонный отклик.

том ИЗ), группу адресных входов 48- 52 блока записи эталона.

Блок управления (фиг. 2) содержит дешифратор 53, коммутатор 54, обра- зованньш элементами И 55-61.

Блок записи эталона (фиг. 3) содержит регистр 62 синхронизации, регистр 63 данных, регистр 64 эталонного отклика, регистр 65 эталонного си нала синхронизации, группы элементов И 66-70, элемент ИЛИ 71, 72, регистр .73 управления, мультиплексор 74 (образован группами элементов И 66-70 и элементом ИЛИ 71).

При осуществлении контроля цифрового блока, в качестве которого может выступать любая серийно вьшуска- емая микросхема, а также готовьй узе

изделия, необходимо произвести целый ряд подготовительных действий,прежде чем подать тестовую последовательность или тестовую команду. К подготовительным действиям можно отнести начальный сброс, установку, задание режима работы и т.п. Затем происходит подача тестовой информации наряду с адресами, а прием информации осуществляется по синхросигналу.

В соответствии с этим регистр 19 служит для записи тестового синхросигнала Регистр 18 служит для записи сигна.пов управления (сброс, установка и т.д.), а также для сигналов тестового воздействия и сигнала признака разрешения приема отклика контролируемого цифрового блока. Двунаправленный регистр 20 служит для

подачи (ввода) тестовой информации, а также для записи (вывода) информации, переданной контролируемым блоком. В случае, когда в качестве контролируемого блока выступает процессорный элемент, двунаправленный регистр подклю.чен к интерфейсной части процессорного элемента. Регистр 21 служит для приема сигнала синхронизации, который подтверждает приход

синхросигнала на контролируемый цифровой блок 25.

В блок 16 записи эталона поступает та же информация, что и на регистры 18, 19 и 20. Это необходимо для

того, чтобы при дальнейшем сравнении мультиплексированной информации вызвать ситуации короткое замыкание и обрыв на входах контролируемого блока 25, Б блок записи эталона записывается также эталонный отклик.

50 рззом.

который 1 дальнейшем в мультиплексированном виде будет сравниваться с откликом контролируемого блока 25, поступающего на группу элементов 8 в мультиплексоре 27. В блок записи эталона, кроме того, записывается

рззом.

эталонный: синхросигнал.Устройство работает следующим об50 рззом.

По сигналу Сброс, подаваемому на вход сброса устройства, останавливается генератор t, обнуляются счетчики 12 и 13, формирователь 47 lj переходит в разрешенное состояние. По сигналу Пуск, подаваемому на вход пуска устройства, генератор 1 начинает свою работу, при этом син- хросигнадгы начинают поступать на

счетные входы счетчиков 12, 13 и управляющий вход коммутатора 54 блока управления.

По адресу сформированному в счетчике 13,иэ блока 17 выбирается тестовое воздействие, которое записьта- ется в регистры 18, 19 и 20 и регистры 73, 62 и 63 блока 16. Одновременно с записью в регистр 64 блока 16 происходит сброс регистра 21, а с записью в регистр 65 блока 16 происходит синхронизация регистра 19, в результате чего проверяемый блок выполняет указанную тестовую команду.

На выходе 31 коммутатора 54 формируется сигнал блокировки формирователя 47, в результате чего блокируется прохождение синхроимпульсов на синхровход генератора 26 тестов, и, следовательно, считывание тестовых воздействий и эталонных ответов заканчивается.

Устройство переходит к проверке результатов выполненной операции, которая происходит следующим образом. На выходах 37-41 дешифратора 53 последовательно образуются сигналы, обеспечиваЕощие, с одной стороны, подключение к выходу блока 16 одного из регистров 73, 62-65 и, с другой стороны, обеспечивающие мультиплексирование информации через мультиплексор 27. Кроме того, при наличии единичных сигналов на адресных входах 48-52 блока 16 на выходе признака наличия информации на адресных входах (выход элемента ИЛИ 72) образуется единичный сигнал,разешающий выдачу информации о результате сравнения с выхода Неравно блока 22. Таким образом, на один из входов блока 22 поступают эталонные, ответы, а на другой вход - результаты тестового воздействия, В том случае, если данные не совпадают, то блок 22 сравнения формирует сигнал, юступающий на вход элемента И 2 и запрещающий прохождение синхросигнаов. При этом элементы 23 и 24 иникации обеспечивают наблюдение расождений. Продолжение тестирования беспечивается путем подачи сигнала на шину 28 устройства, в результате его увеличивается содержимое счетчика 12, и процесс контроля продолжается. По окончании анализа результаов операции на выходе 30 коммутато903334

ра образуется сигнал разрешения для формирователя 47 и обнуления счетчика 12. Таким образом, устройство готово к загрузке нового тестового воз- 5 действия.

Для обеспечения управления двунаправленным регистром 20 в регистре 18 один из разрядов предназначается для

fO указания разрешения к открыванию регистра 20. Сигнал с выхода этого разряда поступает на вход элемента И 4, а на второй вход элемента И 4 поступает -сигнал с выхода признака запроса

15 на ввод следующего тестового воздействия блоком 25. Таким образом, исключается несвоевременная выдача данных блоку 25, которая может привести к недопустимым открываниям двух выхо20 дов. Таким образом, контроль выходных данных регистров 18, 19 и 20 позволяет выявлять короткие замыкания входных цепей проверяемого устройства.

25

Формула изобретения

1. Устройство для контроля цифровых блоков, содержащее генератор тактовых импульсов, формирователь импульса, первый элемент И, генератор тестов, счетчик, первый элемент ИЛИ,блок сравнения, два элемента индикации и блок управления, содержащий дешифратор, причем вход начальной установки

устройства соединен с входом установки генератора тестов, выход генератора тактовых импульсов соединен с первым входом первого элемента И, выход которого соединен с первым входом первого элемента ИЛИ, выход которого соединен со счетным входом счетчика,выход Неравно блока сравнения соединен с вторым входом первого элемента И, отличающееся тем,

что, с целью расширения области применения за счет обеспечения возможности контроля процессорных элемен- тов, а также повышения достоверности контроля за счет выявления ситуаций

короткое замыкание и обрыв на входах контролируемого цифрового блока, устройство содержит второй элемент И и второй элемент ИЛИ, блок записи эталона, двунаправленный регистр, регистр управления,регистр синхронизации, мультиплексор, регистр подтверждения наличия синхронизации, а блок управления содержит коммутатор, причем разрядные выходы

счетчика соединены с информационными входами дешифратора, первая группа выходов которого соединена с информационными входами коммутатораJ управляющий вход которого соединен с выходом первого элемента ИЛИ, выход генератора тактовых импульсов соединен с синхровходом формирователя импульсов, вход разрешения которого соединен с выходом второго элемента ИЛИ и входом сброса счетчика, выход формирователя импульсов соединен с входом синхронизации генератора тестов, второй вход первог элемента ИЛИ соединен с шиной разре шения перехода к следующему адресу тестового набора при обнаружении ошибки на предыдущем адресе устройства, выходы поля синхронизации генератора тестов соединены с первой группой информационных входов блока записи эталона и информационными . входамк регистра синхронизации, выходы ПОЛЯ управления генератора тестов соединены с второй группой ин- формационных входов блока записи эталона и с информационными входами регистра управления, выходы поля .тестового воздействия гененатора тестов соединены с третьей группой ин- формационных входов блока записи эталона и с первой группой информационных входов - выходов двунаправленног регистра,,выходы поля эталонного отклик и выходы поля эталонной син- хронизации генератора тестов соединены с четвертой и пятой группами информационных входов блока записи эталона, первая группа адресных входов которого соединена с второй труп пой выходов дешифратора и адресными входами мультиплексора, выход которого соединен с входом первого злемен- та индикации и с первым информационным входом блока сравнения, вход раз решения которого соединен с входом признака наличия информации на адресных входах блока записи эталона, выход признака наличия информации на информационных входах которого соединен с вторым информационным входом блока сравнения и входом второго элемента индикации, первый выход коммутатора соединен с входом блокировки формирователя импульсов, второй выход коммутатора соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с входом начгшьной установки устройства и входом начальной установки генератора тактовых импульсов, вход пуска которого соединен с входом пуска устройства, третий, четвертьш, пятый шестой и седьмой выходы коммутатора соединены с второй группой адресных входов блока записи эталона, с входом записи регистра синхронизации, входом сброса регистра подтверждения наличия синхронизации, входом синхронизации регистра синхронизации, входом синхронизации регистра управления и входом синхронизации двунаправленного регистра соответственно, выход регистра синхронизации соединен . с первым информационным входом мультиплексора, входом синхронизации контролируемого цифрового блока, входы сброса, установки, разрешения, блокировки, задания режима работы, записи - считывания которого соединены с первой группой выходов регистра управления, вторая группа выходов которого соединена с группой адресных входов контролируемого цифрового блока и с первой группой информационных входов мультиплексора, выход признака разрешения приема отклика контролируемого цифрового блока регистра управления соединен с первым входом второго элемента И, вьпсод которого соединен с входом разрешения двунаправленного регистра, вторая группа информационных входов - выходов соединена с информационными входами-выходами :онтролируемого цифрового блока и с второй группой информационных входов мультиплексора, выход признака запроса на следующую команду контролируемого цифрового блока соединен с вторым входом второго элемента И, информационные выходы контролируемого цифрового блока соединены с третьей группой информационных входов мультиплексора, второй информационный вход которого соединен с выходом- регистра подтверждения наличия синхронизации,, информационный вход которого соединен с вьЪсодом признака приема синхросигнала контролируемого цифрового блока,

2, Устройство по п. 1, о т л и - . чающееся тем, что блок записи эталона содержит пять регистров, мультиплексор и элемент ИЛИ, причем адресные; входы мультиплексора и входы элемента ИЛИ соединены с первой груп71

пой адресных входов блока, выход эле мента ИЛИ и выход мультиплексора

соединены с выходом признака наличия информации на адресных входах блока и выходом наличия информации на информационных входах блока, первая, выгорая, трет1,я, четвертая и пятая группы информационных входов мультиплексора соединены с выходами первого, второго, третьего, четвертого и

2903338

пятого регистров соответственно, информационные входы этих регистров соединены с группами информационных входов блока с первой по пятую включительно, входы второй адресной группы блока соединены с входами синхронизации первого, второго, третьего, четвертого и пятого регистров соответственно.

18,

jK

иг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1988 |

|

SU1661768A1 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1259270A1 |

| Устройство для контроля больших интегральных схем | 1986 |

|

SU1363212A1 |

| Сигнатурный анализатор для контроля цифровых блоков | 1984 |

|

SU1309026A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство тестового контроля цифровых блоков | 1985 |

|

SU1315982A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для контроля микропроцессоров. Цель изобретения - расширение области применения за счет обеспечения возможности контроля процессорных элементов, а также повьш1ение достоверности контроля. Устройство содержит генератор тактовых импульсов, генератор .тестов, блок записи эталона, мультиплексор, регистры входных воздействий, блок сравнения, элемент индикации. В устройстве предусмотрен контроль короткого замыкания на входных контактах контролируемого блока. Перед сравнением выходные данные мультиплексируют. Аналогично в блоке записи эталона эталонная реакция предварительно подвергается мультиплексированию. 1 з.п. ф-лы, 3 ил. (Л СО со со

| Устройство для контроля микросхем | 1977 |

|

SU648981A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1005061A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-15—Публикация

1985-04-20—Подача