(Л

05

ОО

Изобретение относится к системам контроля и может быть использовано для контроля цифровых нерекурсивных фильтров.

Цель изобретения - расширение функциональных возможностей нутем обеспечения контроля цифровых нерекурсивных фильтров с последовательным накоплением выходных отсчетов.

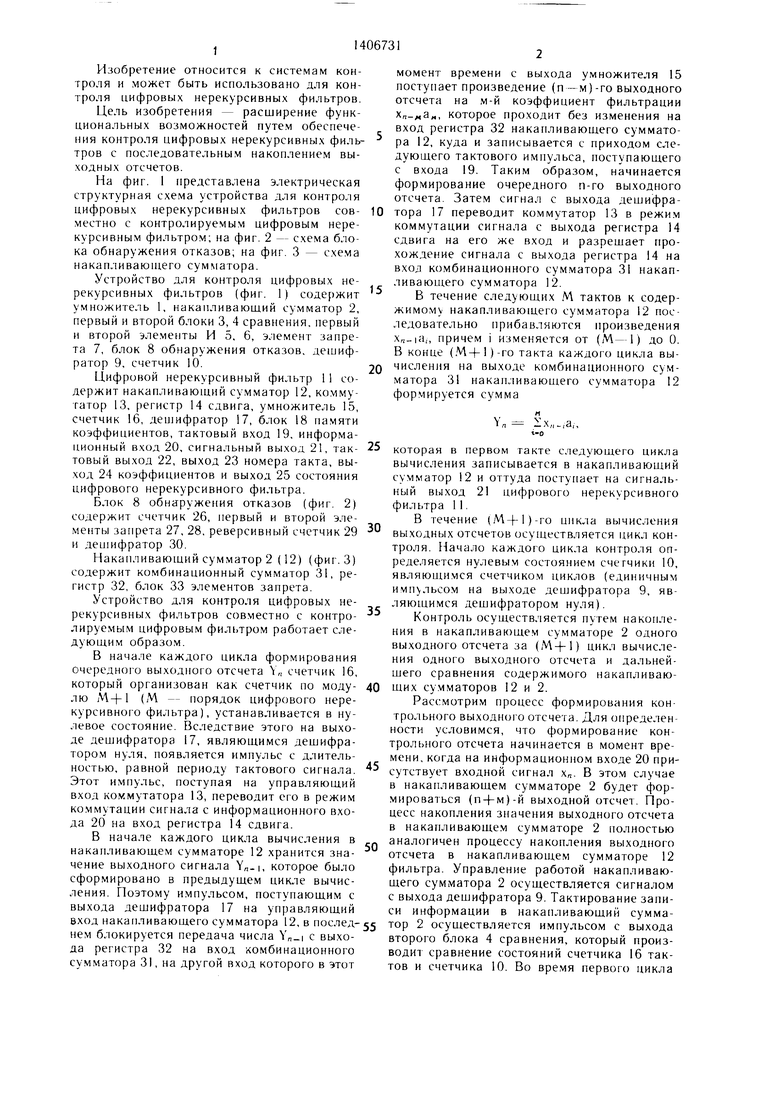

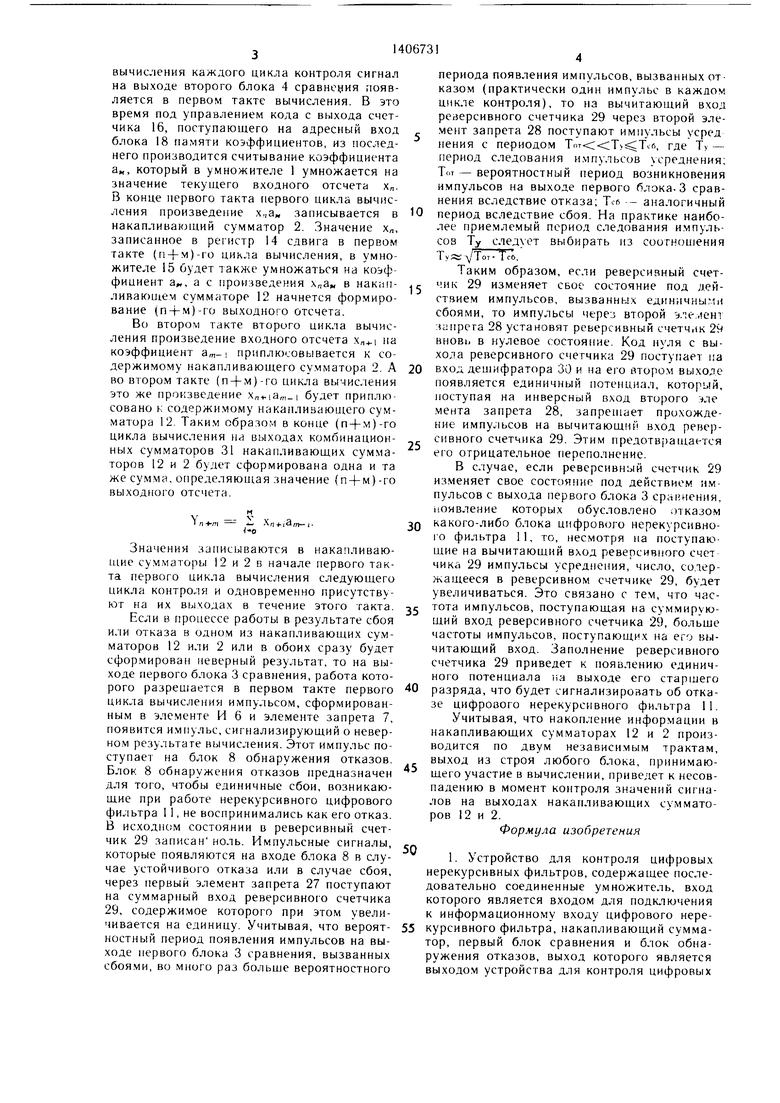

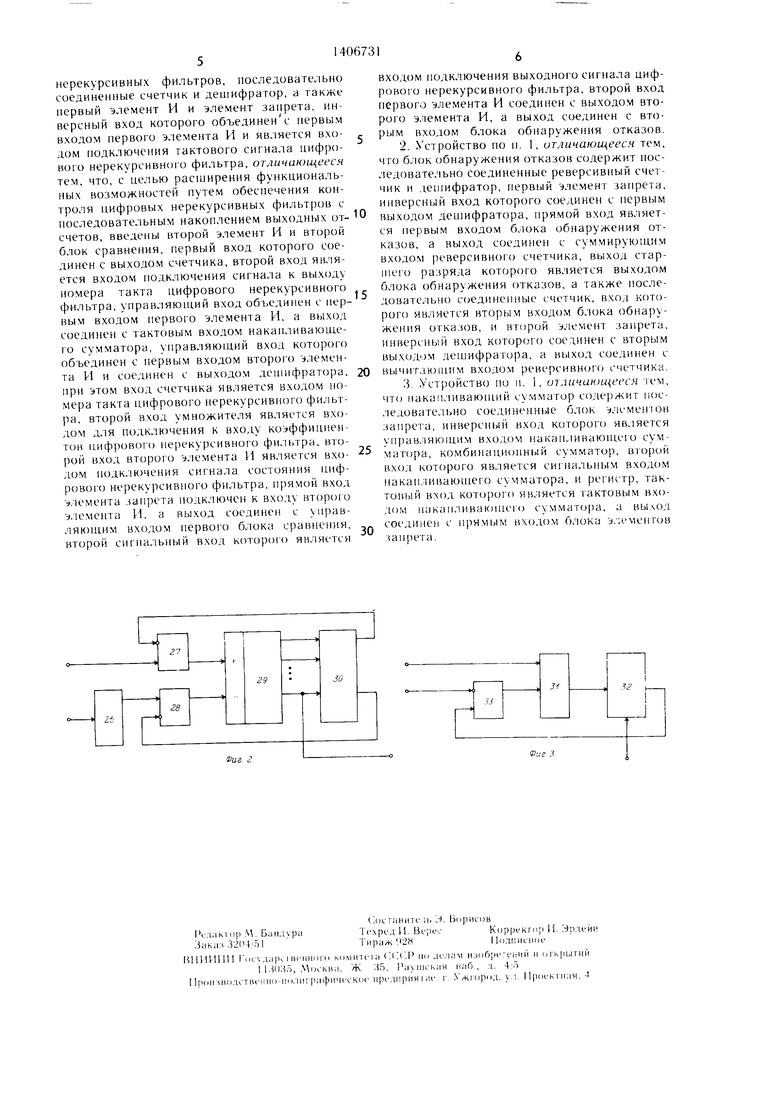

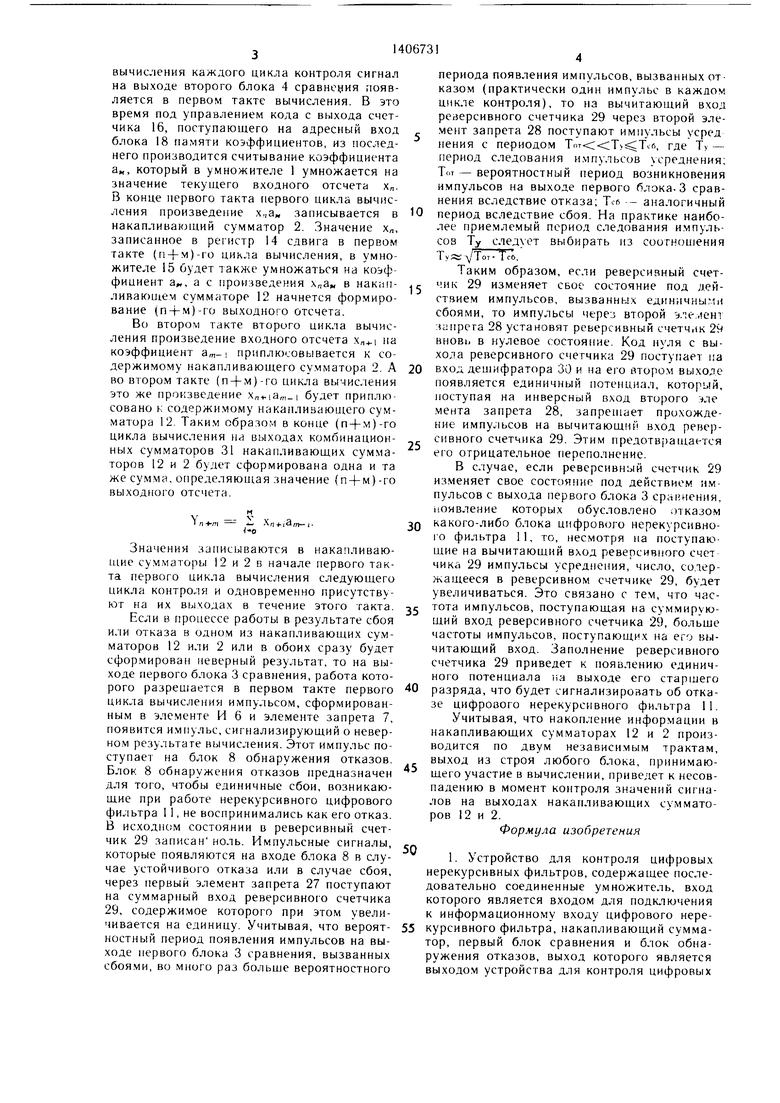

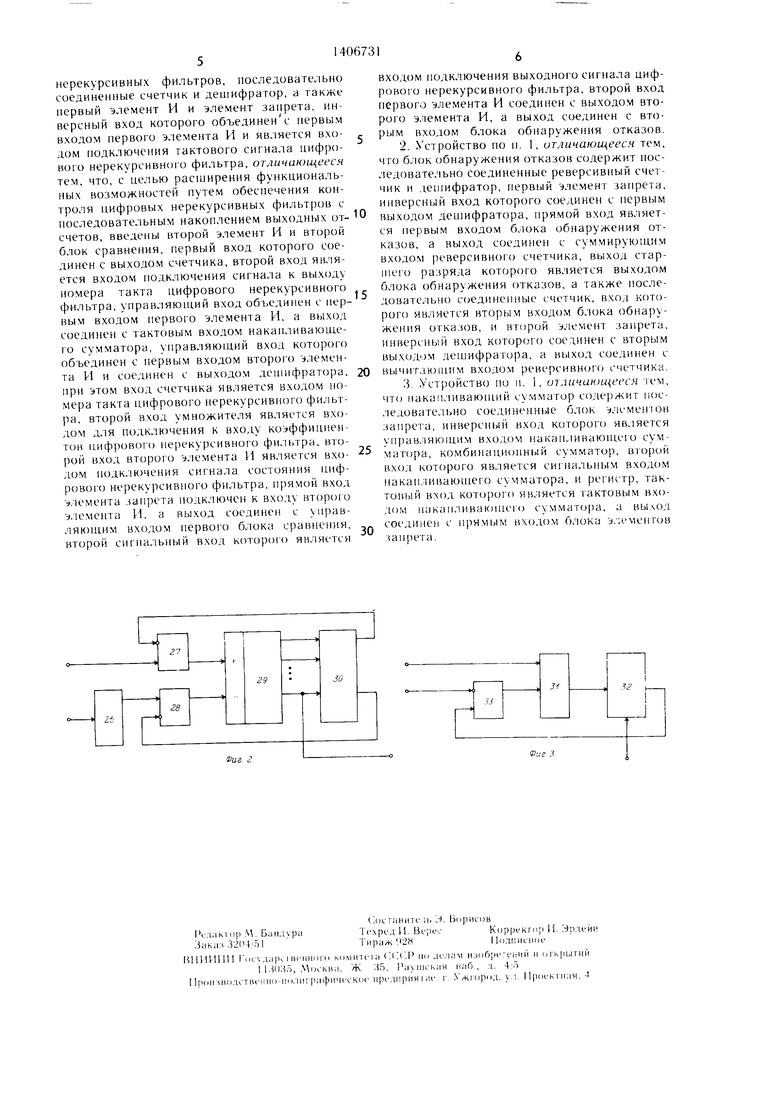

На фиг. 1 представлена электрическая структурная схема устройства для контроля цифровых нерекурсивных фильтров совместно с контролируемым цифровым нерекурсивным фильтром; на фиг. 2 - схема блока обнаружения отказов; на фиг. 3 - схема накапливающего сумматора.

Устройство для контроля цифровых нерекурсивных фильтров (фиг. 1) содержит умножитель 1, накапливающий сумматор 2, первый и второй блоки 3, 4 сравнения, первый и второй эле.менты И 5. 6, элемент запрета 7, блок 8 обнаружения отказов, дешифратор 9. счетчик 10.

Цифровой нерекурсивный фильтр 11 содержит накапливающий сумматор 12, коммутатор 13. регистр 14 сдвига, умножитель 15, счетчик 16, дешифратор 17, блок 18 памяти коэффициентов, тактовый вход 19. информационный вход 20, сигнальный выход 21, тактовый выход 22, выход 23 номера такта, выход 24 коэффициентов и выход 25 состояния цифрового нерекурсивного фильтра.

Блок 8 обнаружения отказов (фиг. 2) содержит счетчик 26, первый и второй элементы запрета 27. 28. реверсивный счетчик 29 и дешифратор 30.

Накапливающий сумматор 2 (12) (фиг. 3) содержит комбинационный сумматор 31, регистр 32, блок 33 элементов запрета.

Устройство для контроля цифровых нерекурсивных фильтров совместно с контро- лируемьЕМ цифровым фильтром работает следующим образом.

В начале каждого цикла формирования очередного выходного отсчета У„ счетчик 16, который организован как счетчик по модулю M+l (М - порядок цифрового нерекурсивного фильтра), устанавливается в нулевое состояние. Вследствие этого на выходе дешифратора 17, являющимся дешифратором нуля, появляется импульс с длительностью, равной периоду тактового сигнала. Этот импульс, поступая на управляющий вход коммутатора 13, переводит его в режим коммутации сигнала с информационного входа 20 на вход регистра 14 сдвига.

В начале каждого цикла вычисления в накагитивающем сумматоре 12 хранится значение выходного сигнала , которое было сформировано в предыдущем цикле вычисления. Ноэтому импульсом, поступающим с выхода дешифратора 17 на управляющий вход накапливающего сумматора 12, в последнем блокируется передача числа с выхода регистра 32 на вход комбинационного сумматора 31, на другой вход которого в этот

0

5

0

5

5

0

5

0

5

0

момент времени с выхода умножителя 15 поступает произведение (п-м)-го выходного отсчета на м-й коэффициент фильтрации , которое проходит без изменения на вход регистра 32 накапливающего сумматора 12, куда и записывается с приходом следующего тактового импульса, поступающего с входа 19. Таким образом, начинается формирование очередного п-го выходного отсчета. Затем сигнал с выхода дешифратора 17 переводит коммутатор 13 в режи.м коммутации сигнала с выхода регистра 14 сдвига на его же вход и разрешает прохождение сигнала с выхода регистра 14 на вход комбинационного сумматора 31 накапливающего сумматора 12.

В течение следующих М тактов к содержимому накапливающего сумматора 12 последовательно фибавляются произведения x,,ia,, причем i изменяется от (М-1) до 0. В конце (M-(-l)-ro такта каждого цикла вычисления на выходе комбинационного сумматора 31 накапливающего сумматора 12 формируется сумма

н

п Хх„.,а,.

t-O

которая в первом такте следующего цик.па вычисления записывается в накапливающий сумматор 12 и оттуда поступает на сигнальный выход 21 цифрового нерекурсивного фильтра 11.

В течение (M-(--l)-ro цикла вычисления выходных отсчетов осуществляется цикл контроля. Начало каждого цикла контроля определяется нулевы.м состоянием счегчики 10, являющи.мся счетчиком циклов (единичным им11 льсом на выходе дешифратора 9, являющимся дешифратором нуля).

Контроль осуществляется путем накопления в накапливающе.м сумматоре 2 одного выходного отсчета за (М-|-1) цикл вычисления одного выходного отсчета и дальнейшего сравнения содержимого накапливающих сумматоров 12 и 2.

Рассмотрим процесс формирования контрольного выходного отсчета. Для определенности условимся, что формирование контрольного отсчета начинается в момент времени, когда на информационном входе 20 присутствует входной сигнал х,,. В этом случае в накапливающем сумматоре 2 будет формироваться (п + м)-й выходной отсче. Процесс накопления значения выходного отсчета в накапливающем сумматоре 2 полностью аналогичен процессу накопления выходного отсчета в накапливающем сумматоре 12 фильтра. Управление работой накапливающего сумматора 2 осуществляется сигналом с выхода дещифратора 9. Тактирование записи информации в накапливающий сумматор 2 осуществляется импульсом с выхода второго блока 4 сравнения, который производит сравнение состояний счетчика 16 тактов и счетчика 10. Во время первого цикла

вычисления каждого цикла контроля сигнал на выходе второго блока 4 сравнс1;1ия появляется в первом такте вычисления. В это время под управлением кода с выхода счетчика 16, поступающего на адресный вход блока 18 памяти коэффициентов, из последнего производится считывание коэффициента а„, который в умножителе 1 умножается на значение текущего входного отсчета Хп. В конце первого такта первого цикла вычисления произведение x,,a« записывается в накапливающий сумматор 2. Значение х„, записанное в регистр 14 сдвига в первом такте (п + м)-го цикла вычисления, в умножителе 15 будет также умножаться на коэффициент а„, а с произведения х„а« в накип- ливающем сумматоре 12 начнется формирование (п + м)-го выходного отсчета.

Во втором такте второго цикла вычисления произведение входного отсчета х„ на коэффициент am- приплюсовывается к содержимому накапливающего сумматора 2. А во втором такте (п-|-м)-го цикла вычисления это же произведение .iam-i будет приплюсовано к содержимому накапливающего сумматора 12. Таким образом в конце (п-)--м)-го цикла вычисления на выходах комбинационных сумматоров 31 накапливающих сумматоров 12 и 2 будет сформирована одна и та же сумма, определяющая значение (п + м)-го выходного отсчета.

м VV ,,

п-t-i т i

-0

Значения записываются в накапливаю- 1цие сумматоры 12 и 2 в начале первого такта первого цикла вычисления следующего цикла контроля и одновременно присутствуют на их выходах в течение этого такта.

Если в процессе работы в результате сбоя или отказа в одном из накапливающих сумматоров 12 или 2 или в обоих сразу будет сформирован неверный результат, то на выходе первого блока 3 сравнения, работа которого разрешается в первом такте первого цикла вычисления импульсом, сформированным в элементе И 6 и элементе запрета 7, появится импульс, сигнализирующий о невер- но.м результате вычисления. Этот импульс поступает на блок 8 обнаружения отказов. Блок 8 обнаружения отказов предназначен для того, чтобы единичные сбои, возникающие при работе нерекурсивного цифрового фильтра 11, не воспринимались как его отказ. В исходном состоянии в реверсивный счетчик 29 записан ноль. Импульсные сигналы, которые появляются на входе блока 8 в случае устойчивого отказа или в случае сбоя, через первый элемент запрета 27 поступают на суммарный вход реверсивного счетчика 29, содержимое которого при этом увеличивается на единицу. Учитывая, что вероятностный период появления импульсов на выходе первого блока 3 сравнения, вызванных сбоями, во много раз больше вероятностного

0

5

0

5

0

5

0

5

0

5

периода появления импульсов, вызванных отказом (практически один импульс в каждом цикле контроля), то на вычитающий вход реверсивного счетчика 29 через второй элемент запрета 28 поступают импульсы усред нения с периодом TnT«Tv Ti6, где Ту - период следования импульсов усреднения; Тот - вероятностный период возникновения импульсов на выходе первого блока-3 сравнения вследствие отказа; Ten - аналогичный период вследствие сбоя. На практике наиболее приемлемый период следования импульсов Ту следует выбирать из соотношения

Тот- Тсб.

Таким образом, если реверсивный счетчик 29 изменяет свое состояние под действием импульсов, вызванных единичными сбоями, то импульсы через второй э.- .е/иент запрега 28 установят реверсивный счетчик 29 вновь в нулевое состояЕ1ие. Код нуля с выхода реверсивного счетчика 29 поступает iia вход дешифратора 30 и на его втором выходе появляется единичный потенциал, который, поступая на инверсный вход второго эле мента запрета 28, запрещает прохождение импульсов на вычитающий вход реверсивного счетчика 29. Этим предотв)ащается его отрицательное переполнение.

В случае, если реверсивный счетчик 29 изменяет свое состояние под действием импульсов с выхода первого блока 3 сравнения, появление которых обусловлено отказом какого-либо блока цифрового нерекурсивного фильтра 11, то, несмотря на поступающие на вычитающий вход реверсивного счет чика 29 импульсы ycpeд leния, число, co.iep- жащееся в реверсивном счетчике 29, будет увеличиваться. Это связано с тем, что частота импульсов, поступающая на суммирующий вход реверсивного счетчика 29, больше частоты импульсов, поступающих на его вычитающий вход. Заполнение реверсивного счетчика 29 приведет к появлению единичного потенциала lia выходе его старшего разряда, что будет сигнализировать об отказе цифрового нерекурсивного фильтра 11.

Учитывая, что накоп.тение информации в накапливающих сумматорах 12 и 2 производится по двум независимым трактам, выход из строя любого блока, принимающего участие в вычислении, приведет к несовпадению в момент контроля значений сигналов на выходах накапливающих сумматоров 12 и 2.

Формула изобретения

1. Устройство для контроля цифровых нерекурсивных фильтров, содержащее последовательно соединенные умножитель, вход которого является входом для подключения к информационному входу цифрового нерекурсивного фильтра, накапливающий сумматор, первый блок сравнения и блок обнаружения отказов, выход которого является выходом устройства для контроля цифровых

нерекурсивных фильтров, последовательно соединенные счетчик и дешифратор, а также первый элемент И и элемент запрета, инверсный вход которого объединен с первым входом первого элемента И и является вхо- дом подключения тактового сигнала цифрового нерекурсивного фильтра, отличающееся тем, что, с целью расширения функциональных возможностей путем обеспечения контроля цифровых нерекурсивных фильтров с последовательным накоплением выходных отсчетов, введены второй элемент И и второй блок сравнения, первый вход которого соединен с выходом счетчика, второй вход является входом подключения сигнала к выходу номера такта цифрового нерекурсивного фильтра, управ:1яюпхий вход об1 единен с нер- вым входом первого элемента И, а выход соединен с тактовым входом наканливающе- го сумматора, управляющий вход которого объединен с первым входом второго элемента И и соединен с выходом дешифратора, при этом вх(Х 1, счетчика является входом номера такта цифрового перекурсивного фильтра, второй вход умножителя является входом для подключения к входу коэффициен- T(jB цифрового перекурсивного фил1)тра, второй вход второго элемента И является входом подключения сигнала состояния циф- poBoi o нерекурсивного фильтра, прямой вход элемента запрета подключен к входу второю э.лемепта И, а выход соединен с управляющим входом первого блока сравнения, второй сигнальный вход которого является

5

0

5

0

входом подключения выходного сигнала цифрового нерекурсивного фильтра, второй вход первого элемента И соединен с выходом второго элемента И, а выход соединен с вторым входом блока обнаружения отказов.

2. cтpoйcтвo по п. 1, отличающееся тем, что блок обнаружения отказов содержит последовательно соединенные реверсивный счетчик и дешифратор, первый элемент запрета, инверсный вход которого соединен с первым выходом дешифратора, прямой вход является первым входом блока обнаружения отказов, а выход соединен с суммирующим входом реверсивного счетчика, выход старшего разряда которого является выходом блока обнаружения отказов, а также последовательно соединенные счетчик, вход которого является вторым входом блока обпару- жения отказсзв, и второй элемент запрета, инверсный вход KOTopoi o соединен с вторым выходом дешифрагора, а выход соединен с вычитающим входом реверсивного счетчика.

3.Устройство по п. 1, отличающееся тем, что накапливающий сумматор содержит пос- ледовательпо соединенные блок элементов запрета, инверсный вход которого является управляющим входом накапливаюп1его сумматора, комбинационный сумматор, вто)ой вход которого является сигналь}1ым входом накапливаюнхего сумматора, и регистр, тактовый вход которого является тактовым входом накап:1ивак)|пег(. сумматора, а вы.од соединен с пря.мым входо.м бл(жа элемептов зац)ета.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых нерекурсивных фильтров | 1986 |

|

SU1343556A1 |

| Цифровой нерекурсивный фильтр | 1987 |

|

SU1483608A1 |

| Цифровой нерекурсивный фильтр | 1985 |

|

SU1352622A1 |

| Цифровой нерекурсивный фильтр | 1986 |

|

SU1332519A1 |

| Цифровой нерекурсивный фильтр нечетного порядка | 1985 |

|

SU1314445A1 |

| Специализированный процессор для цифровой фильтрации | 1989 |

|

SU1631558A1 |

| Цифровой нерекурсивный фильтр | 1974 |

|

SU516043A1 |

| Цифровой фильтр | 1983 |

|

SU1145346A1 |

| Устройство для обработки радиосигналов | 1980 |

|

SU955083A1 |

| Нерекурсивный цифровой фильтр | 1983 |

|

SU1322421A1 |

Изобретение относится к системам контроля. Цель изобретения - расширение функциональных возможностей. Устр-во содержит умножитель 1, накапливающий сумматор 2, блоки сравнения 3 и 4. Ц 5 и б, эл-т запрета 7, блок обн. 1ружения 8 отказов, дешифратор 9, счетчик 1(1 и цифровой не)екурсивный фильтр 11. Цель досгиг легся путем обеспечения контроля ццфровы.х нерекурсивных фильтров с последовательным н. ;- коиление.м выходны.х отсчетов с помощью введенных И 6 и блока сравнения 4. Устр-во но п.п. 2 и 3 ф-лы отличается В1Л- нолнением блока обнаружения 8 отказов и накапливающего сумматора 2. Даны их H.I. 2 3. Н. ф-лы, 3 ил.

Физ

| Устройство для контроля цифровых нерекурсивных фильтров | 1986 |

|

SU1343556A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-06-30—Публикация

1986-11-12—Подача