1 1

Изобретение относится к цифровой обработке сигналов и может быть использовано для фильтрации электрических сигналов в связи, системах авторегулирования, измерительных приборах ,

Цель изобретения - уменьшение задержки между соответственными входными и выходными отсчетами фильтруемого сигнала.

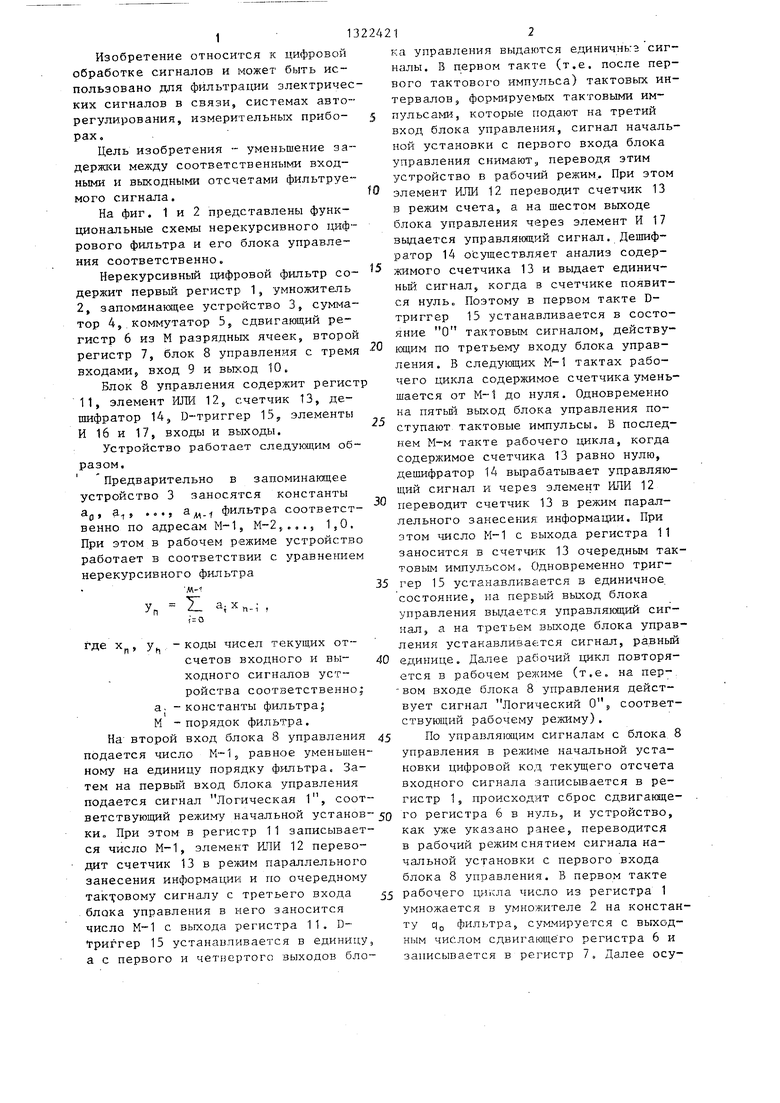

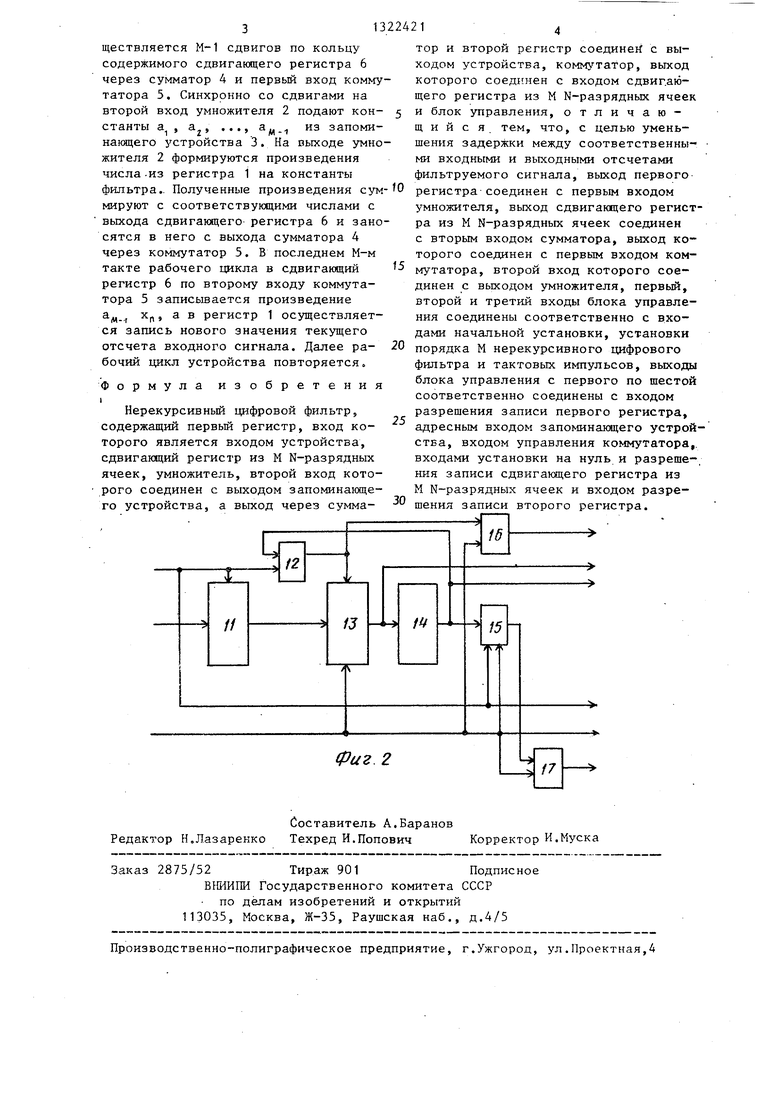

На фиг. 1 и 2 представлены функциональные схемы нерекурсивного цифрового фильтра и его блока управления соответственно.

Нерекурсивный цифровой фильтр содержит первый регистр 1, умножитель 2, запомииакщее устройство 3, сумматор 4,,коммутатор 5, сдвигающий регистр 6 из М разрядных ячеек, второй регистр 7, блок 8 управления с тремя входамиJ вход 9 и вькод 10.

Блок 8 управления содержит регист 11, элемент ИЛИ 12, счетчик 13, дешифратор 14 J D-триггер 15,, элементы И 16 и 17, входы и выходы.

Устройство работает следующим образом.

Предварительно в запоминающее устройство 3 заносятся константы Яд, а , ..., а. фильтра соответственно по адресам М-1, М-2,..., 1,0. При этом в рабочем режиме устройство работает в соответствии с уравнением нерекурсивного фильтра

М-1

УП И а;Х„., , i-o

X

п

- коды чисел текущих отсчетов входного и выходного сигналов устройства соответственно

-константы фильтра;

-порядок фильтра.

На второй вход блока 8 управления подается число М-1, равное уменьшенному на единицу порядку . Затем на первьш вход блока управления подается сигнал Логическая 1, соответствующий режину начальной уставов-50 го регистра 6 в нуль, и устройство.

ки„ Лри этом в регистр 11 записывается число М-1, элемент 12 переводит счетчик 13 в режим паргшлельного занесения информации и по очередному так овому сигналу с третьего входа блока управления в него заносится число М-1 с выхода регистра 11. D- 1; риггер 15 устанавливается в единицу, а с первого и четвертого выходов блокак уже указано ранее, переводится в рабочий режим снятием сигнала начальной установки с первого входа блока 8 управления. В первом такте 55 рабочего цикла число из регистра 1 умножается в умножителе 2 на констан ту q фильтра, суммируется с выходным числом сдвигающе го регистра 6 и записывается в регистр 7. Далее осу

5

0

5

0

5

0

5

ка управления выдаются единичны сигналы. В первом такте (т.е. после первого тактового импульса) тактовых интервалов, формируемых тактовыми импульсами, которые подают на третий вход блока управления, сигнал начальной установки с первого входа блока управления снимают., переводя этим устройство в рабочий режим. При этом элемент ИЛИ 12 переводит счетчик 13 в режим счета, а на шестом выходе блока управления через элемент И 17 вьщается управляющий сигнал. Дешифратор 14 осуществляет анализ содержимого счетчика 13 и выдает единич- ньй сигнал, когда в счетчике появится нуль о Поэтому в первом такте D- триггер 15 устанавливается в состояние О тактовым сигналом, действу- кщим по третьему входу блока управления. В следующих М-1 тактах рабочего цикла содержимое счетчика уменьшается от М-1 до нуля. Одновременно на пятьй выход блока управления поступают тактовые импульсы. В последнем М-м такте рабочего цикла, когда содержимое счетчика 13 равно нулю, дешифратор 1А вырабатывает управляющий сигнал и через элемент ИЛИ 12 переводит счетчик 13 в режим параллельного занесения информации. При этом число М-1 с выхода регистра 11 заносится в счетчик 13 очередным тактовым импульсом. Одновременно триггер 15 устанавлр1вается в единичное состояние, на первый выход блока управления выдается управлякяций сигнал, а на третьем выходе блока управления устанавливается сигнал, равный единице. Да,пее рабочий цикл повторяется в рабочем режиме (т.е. на пер-, вом входе блока 8 управления действует сигнал Логический О, соответствующий рабочему режиму).

По управляющим сигналам с блока 8 управления в режиме начальной установки цифровой код текущего отсчета входного сигнала записывается в регистр 15 происход:ят сброс сдвиганяце-

как уже указано ранее, переводится в рабочий режим снятием сигнала начальной установки с первого входа блока 8 управления. В первом такте рабочего цикла число из регистра 1 умножается в умножителе 2 на константу q фильтра, суммируется с выходным числом сдвигающе го регистра 6 и записывается в регистр 7. Далее осуществляется М-1 сдвигов по кольцу содержимого сдвигающего регистра 6 через сумматор 4 и первый вход коммутатора 5. Синхронно со сдвигами на второй вход умножителя 2 подают кон- станты а , а, ,.., а из запоми- накицего устройства 3. На выходе умножителя 2 формируются произведения числа -из регистра 1 на константы фильтра.. Полученные произведения сум мируют с соответствующими числами с выхода сдвигакхцего регистра 6 и заносятся в него с выхода сумматора 4 через коммутатор 5. В последнем М-м такте рабочего цикла в сдвигающий регистр 6 по второму входу коммутатора 5 записьшается произведение M-f п регистр 1 осуществляется запись нового значения текущего отсчета входного сигнала. Далее рабочий цикл устройства повторяется.

Формула изобретения I

Нерекурсивный цифровой фильтр, содержащий первьй регистр, вход которого является входом устройства, сдвигающий регистр из М N-разрядных ячеек, умножитель, второй вход которого соединен с выходом запоминаняце- го устройства, а выход через сумма

О 5

0

5

0

тор и второй регистр соединен с выходом устройства, коммутатор, выход которого соединен с входом сдвигающего регистра из М N-разрядных ячеек и блок управления, отличающий с я тем, что, с целью уменьшения задержки между соответственными входными и выходными отсчетами фильтруемого сигнала, выход первого регистра соединен с первьм входом умножителя, выход сдвигакщего регистра из М N-разрядных ячеек соединен с вторым входом сумматора, выход которого соединен с первым входом коммутатора, второй вход которого соединен с выходом умножителя, первый, второй и третий входы блока управления соединены соответственно с входами начальной установки, установки порядка М нерекурсивного цифрового фильтра и тактовых импульсов, выходы блока управления с первого по щестой соответственно соединены с входом разрешения записи первого регистра, адресным входом запоминающего устройства, входом управления коммутатора,, входами установки на нуль и разреше-. ния записи сдвигающего регистра из М Н разрядных ячеек и входом разрешения записи второго регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых нерекурсивных фильтров | 1986 |

|

SU1406731A1 |

| Цифровой нерекурсивный фильтр | 1988 |

|

SU1566472A1 |

| Нерекурсивный цифровой фильтр | 1984 |

|

SU1171995A1 |

| Цифровой нерекурсивный фильтр нечетного порядка | 1985 |

|

SU1314445A1 |

| Специализированный процессор для цифровой фильтрации | 1989 |

|

SU1631558A1 |

| Цифровой формирователь спектра | 1984 |

|

SU1171804A1 |

| Цифровой нерекурсивный фильтр | 1985 |

|

SU1352622A1 |

| Нерекурсивный цифровой фильтр-дециматор | 1989 |

|

SU1698953A2 |

| Цифровой нерекурсивный фильтр | 1986 |

|

SU1332519A1 |

| Цифровой рекурсивный фильтр | 1988 |

|

SU1578720A1 |

Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах Т управления и измерения для построения устройств цифровой фильтрации. Целью изобретения является уменьшение задержки между соответственными входными и выходными отсчетами фильтруемого сигнала. Нерекурсивный цифровой фильтр содержит первый и второй регистры 1, 7, умножитель 2, запоминающее устройство 3, коммутатор 5, сдвигающий регистр 6, сумматор 4 и блок 8 управления. Цикл работы устройства состоит из п тактов. В каждом такте выполняются одно умножение и одно сложение. Значение выходной переменной вычисляется в конце первого такта. 2 ил. / со to ю кэ D 5 / /ч7Г

//

13

-

/

фиг. 2

Составитель А.Баранов Редактор Н.Лазаренко Техред И.Попович Корректор И.Муска

Заказ 2875/52 Тираж 901Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

| Устройство для деления | 1976 |

|

SU612246A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Рабинер Л., Гоулд Б | |||

| Теория и применение цифровой обработки сигналов.- М.: Мир, 1978, с.598, фиг | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1987-07-07—Публикация

1983-08-12—Подача