Изобретение относится к устройствам контроля цифровых систем обработки сигналов и может быть использовано для контроля сбоев в работе цифровых нерекурсивных фильтров.

Цель изобретения - повышение качества контроля путем обнаружения многократных сбоев.

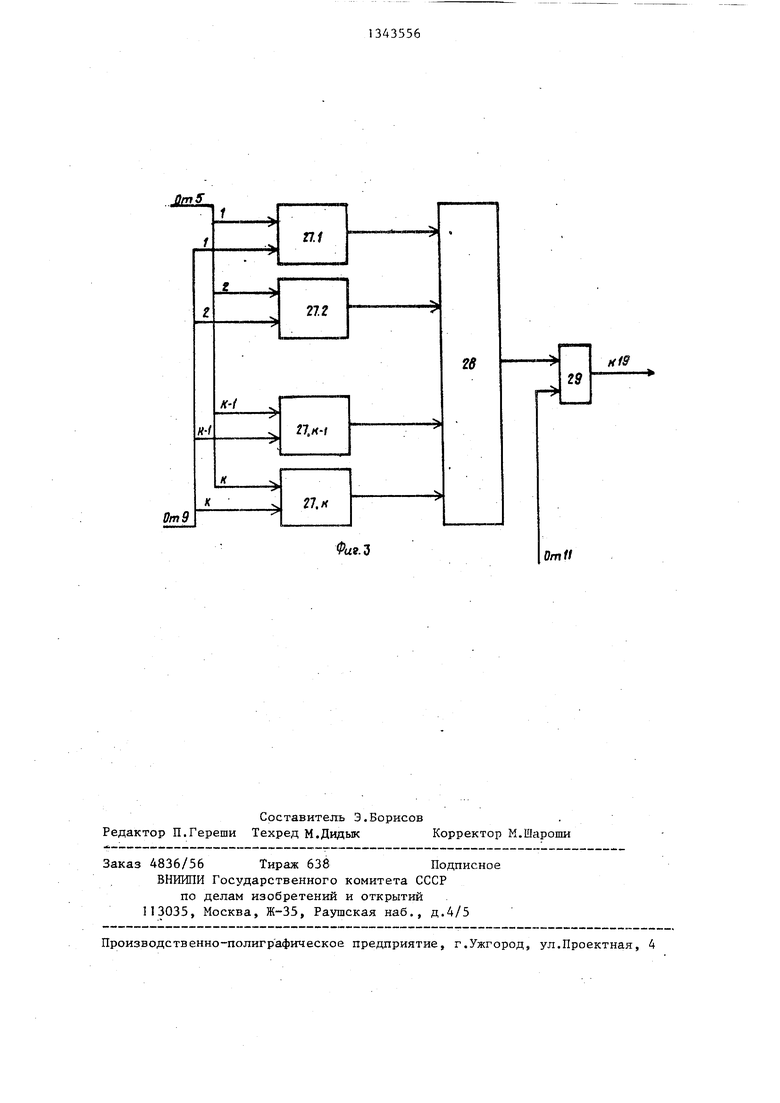

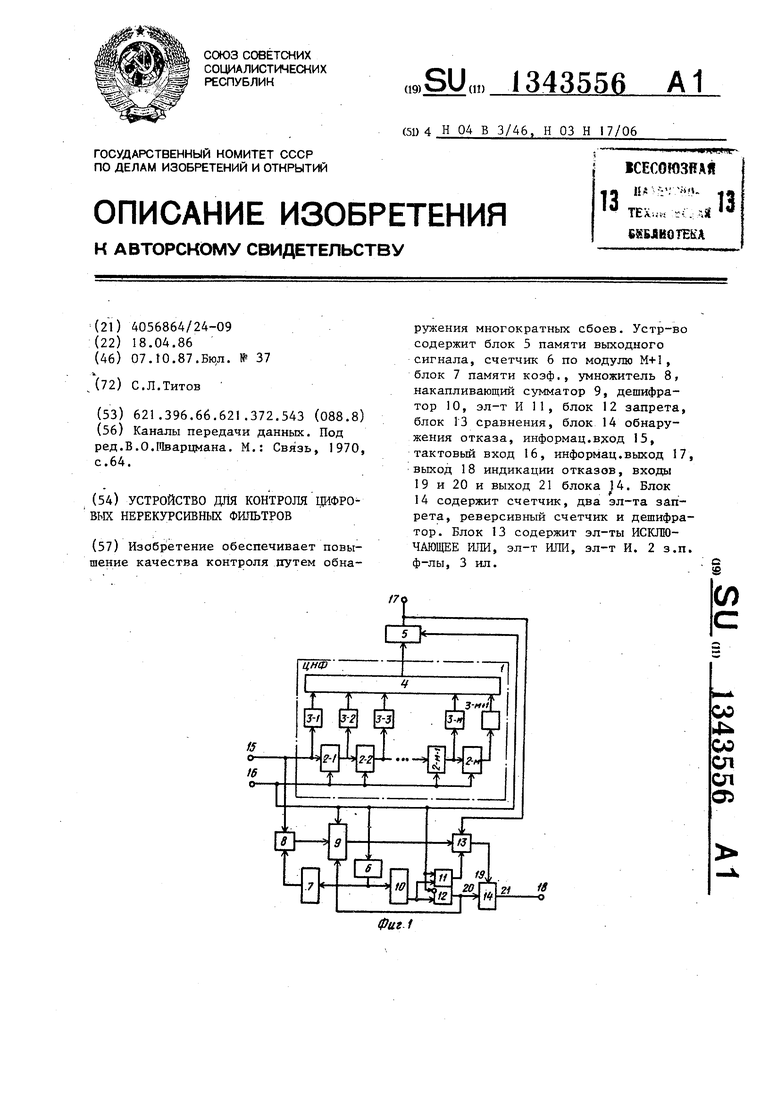

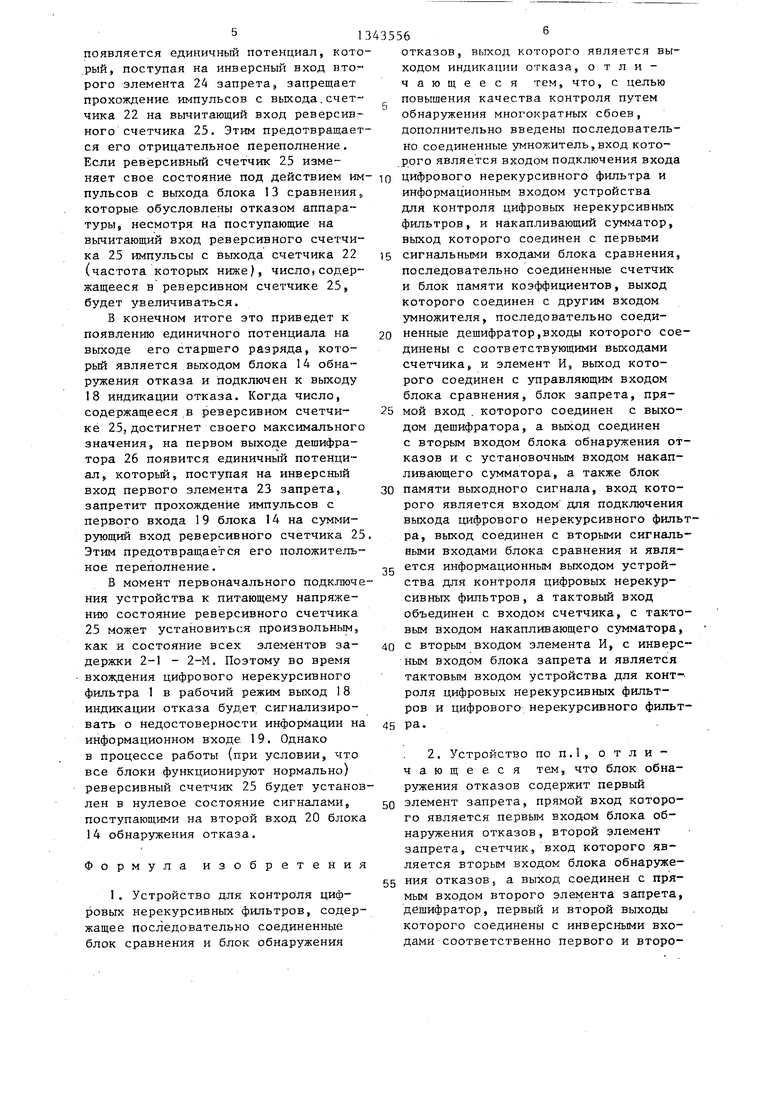

На фиг.I представлена электрическая структурная схема устройства для контроля цифровых нерекурсивных фильтров совместно с контролируемым цифровым нерекурсивным фильтром; на фиг,2 - схема блока обнаружения отказа; на фиг.3 - схема блока сравнения.

Устройство содержит цифровой нерекурсивный фильтр J состоящий из элементов 2-1-2-М задержки, умножителей 3-1-3-М+1 и сумматора 4, блок 5 памяти выходного сигнала, счетчик 6 по модулю М+1, блок 7 памяти коэффициентов, умножитель 8, накапливающий сумматор 9, дещифра- тор 10, -элемент И I1„ блок 12 запрета, блок 13 сравнения, блок 14 обнаружения отказа, информационный 15 и тактовый 16 входы, информационный выход 17, выход 18 индикации отказов, первый 19 и второй 20 входы и выход 21 блока 14 обнаружения отказа

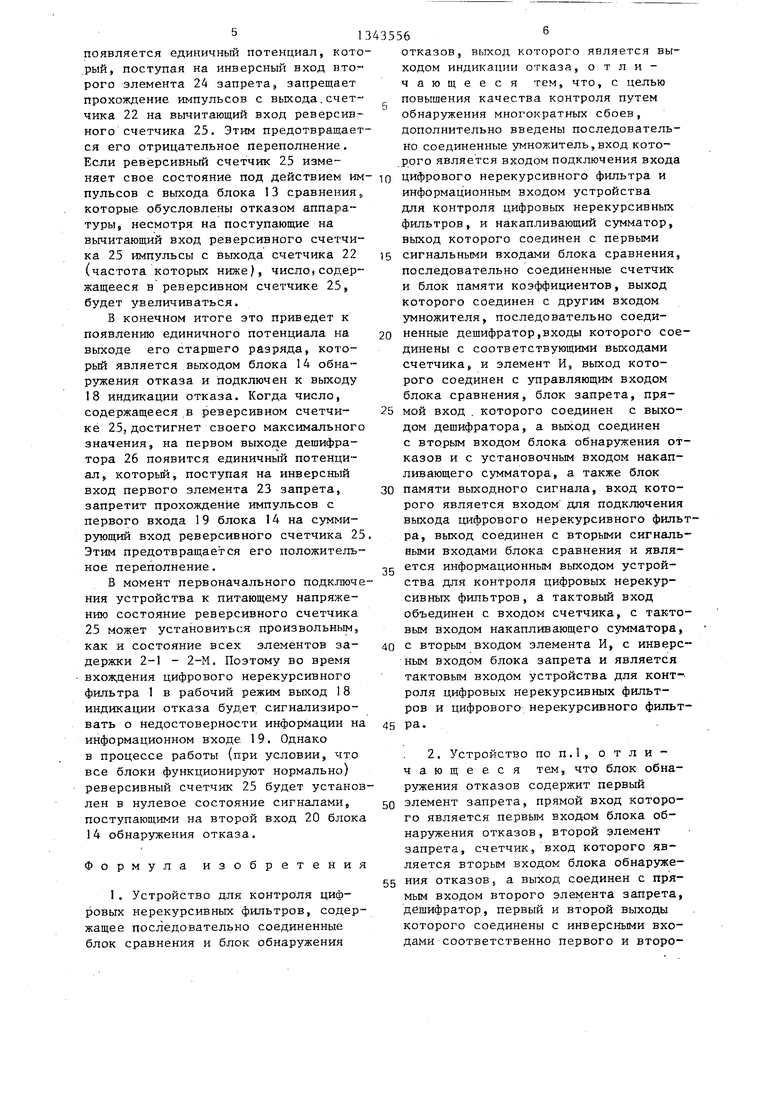

Блок. 14 обнаружения отказа содер- жит счетчик 22, первый 23 и второй 24 элементы запрета, реверсивньш счетчик 25 и дещифратор 26.

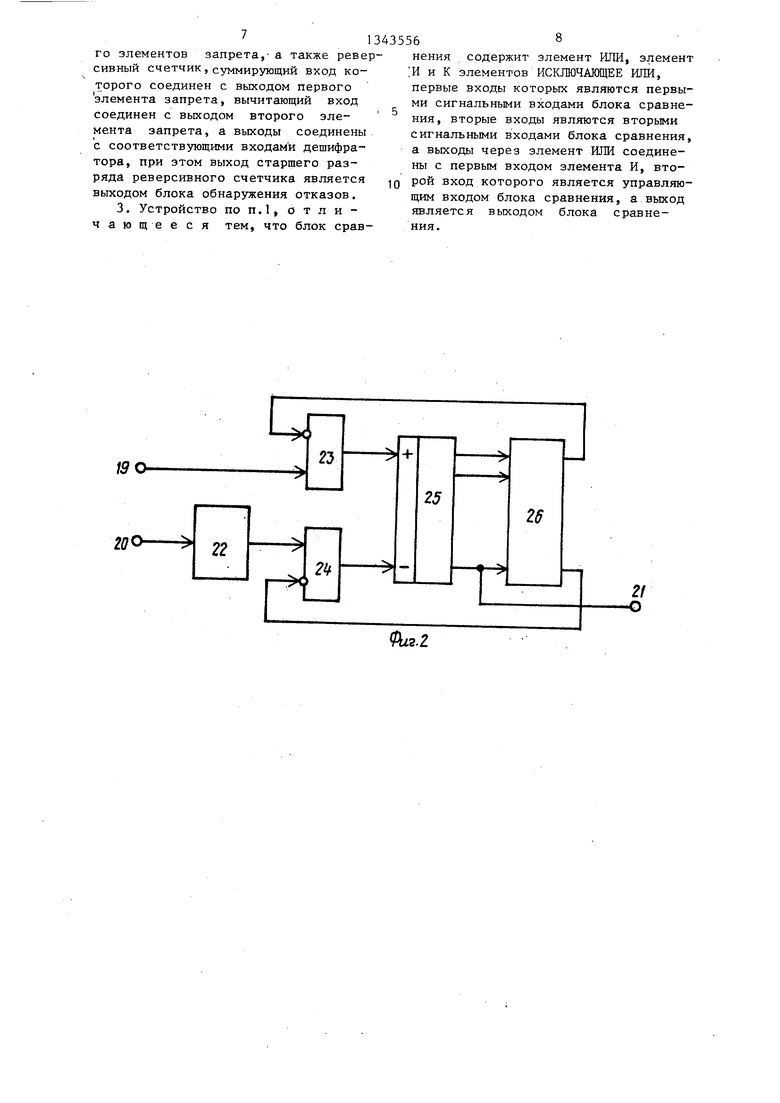

Блок 13 сравнения содержит элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 27-1-27-К, элементы ИЛИ 28 и И 29.

Устройство для контроля цифровых нерекурсивных фильтров работает следующим образом.

В начале каждого такта вычисления под действием переднего фронта сигнала, поступающего с тактового входа 16 на тактовые входы элементов 2-1 и 2-м задержки, в последних производится перезапись информации. При зтом из элемента задержки 2-М информация выводится, а на информационный вход 15 поступает значение новог входного сигнала отсчета.

В умножителях 3-1 - З-М+1 производится умножение отсчетов входного сигнала на коэффициенты фильтрации, которые храняться в .множителях 3-1 З-М+1. Сумматор 4 производит суммирование произведений X j,; а -. В конце каждого п-го такта на выходе

сумматора 4 формируется счета м

I X,

ходного отсчета м

в начале каждого следующего такта значение выходного отсчета с выхода сумматора 4 перезаписывается в блок 5 памяти, где хранится весь следующий такт, поступая при этом на информационный выход 17 фильтра.

Один раз за М+1 тактов вычисления, когда счетчик 6 по модулю М+1 устанавливается в нулевое состояние,

а на информационный вход 15 устройства поступает п-й отсчет входного сигнала, начинается первый такт цикла контроля аппаратуры, причем каждый .цикл контроля длится М+1 тактов вычисления, в течение которых в накапливающем сум -1аторе 9 вычисляется значение п+М-го выходного отсчета.

В первом такте цикла контроля на

выходе дешифратора 10 генерируется сигнал логической единицы. Этот сигнал, поступающий на прямой вход блока 12 запрета, совместно с готри- цательным сигналом, поступающим с

тактового входа 16 в конце первого такта цикла контроля на инверсный вход блока 12 запрета, приводит к образованию импульса на его выходе. Этот импульс, поступая на вход установки накапливающего сумматора 9, производит его обнуление. Одновременно с этим очередной п-й отсчет входного сигнала поступает на пер- вьй вход умножителя 8, на второй

вход которого поступает коэффициент фильтрации а с выхода блока 7 памяти коэффициента.

В течение всего цикла контроля номер коэффициента, считьшаемого из

блока 7 памяти коэффициентов, определяется кодом числа (номером такта контроля), поступающего на вход блока 7 памяти коэффициентов с выхода счетчика 6 по модулю М+1, при- .

чем i-му состояншо счетчика 6 соответствует M-i-й коэффициент фильтрации. В конце первого такта цикла контроля значение произведения Х- а„ под действием переднего фрон

М

та сигнала, поступающего на тактовый вход накапливающего сумматора 9, записывается в него.

В течение последующих М тактов вычисления входные отсчеты X,j,j(i

31

f,М).поступающие на информационный вход 15, умножаются в умножителе 8 на соответствующие коэффициенты фильтрации. Вычисленные произведения накапливаются в накапливающем сумматоре 9, в котором в начаЛе первого такта следующего цикла вычисления будет сформировано значение п п+М-го выходного отсчета мо

h+M f- 04,- M-i f- ,- i

1-0 iW

к этому моменту времени такое же значение выходного отсчета (при условии отсутствия отказов или сбоя) будет находиться в блоке 5.

В начале первого такта каждого цикла вычисления (во время присутствия единичного потенциала на тактовом входе 16 устройства и втором входе элемента И П) импульсом, поступающим с выхода элемента И 11, разрешается работа блока 13 сравнения . Если в накапливающем сумматоре 9 и блоке 5 находятся одинаковые значения выходных сигналов, что возможно в случае безотказной рабдты, выход блока 13 сравнения не изменяется, т.е. остается в состоянии логического нуля. При возникновении отказа или сбоя, что приводит к различным значениям сигнала в блоке 5 и накапливающем сумматоре 9, на выходе блока 13 сравнения появится положительный импульс, который регистрируется блоком 14 обнаружения отказа.В конце первого такта каждого цикла контроля импульс с выхода блока 12 запрета производит обнуление накапливающего сумматора 9 и процесс контроля повторяется.

Блок 14 обнаружения отказа предназначен для того, чтобы единичные сбои не воспринимались как отказ оборудования, поскольку единичные. сбои не вызывают существенного искажения выходного сигнала, что связа rio с усредняющими (фильтрующими) особенностями контролируемого цифро ваго нерекурсивного фильтра.

Например, единичные сбои в элементах 2-1 - 2-м задержки цифрового нерекурсивного фильтра 1 приводят лишь к кратковременному (длительностью не более М выходных отсчетов) искажению выходной информации фильтра. Абсолютная величина искажения при этом не превьшает значения

я 9 -Р макг

г де я.с - значение мак

симально большого коэффициента фильтрации, Р - вес искаженного разряда. Работа блока 14 обнаружения отказа основана на том, что вероятностный период появления импульсов, вызванных отказом оборудования (практически один импульс на цикл контроля) на выходе блока 13 сравнения в много раз меньше, чем вероятностный период появления импульсов, вызванных единичными сбоями аппаратуры. Вследствие этого блок 14 обнаружения отказа выполняет функцию сравнения частоты следования импульсов с выхода блока 13 сравнения с некоторой частотой 1/Ту, выбираемой из .

соотношения

Т.,

« Т

сб

где

Тр - вероятностный период возникновения импульсов на выходе блока 13 сравнения вследствие отказа аппаратуры, Tgif - аналогичный период вследствие единичных сбоев.

Наиболее приемлемый период следования импульсов условия

Т., Y

От

0

5

0

5

0

5

Сигнал с необходимым периодом следования вырабатывается счетчиком 22 блока 14 обнаружения отказа, коэффициент пересчета которого выбирается из условия понижения частоты следования импульсов с выхода блока 12 запрета (один раз за цикл контроля) до частоты 1/Т.

В исходном состоянии в реверсивный счетчик 25 блока 14 обнаружения отказа записано число ноль. Импульсные сигналы, появляющиеся на первом входе 19 блока в случае устойчивого отказа или в случае сбоя, через первый элемент 23 запрета поступают на суммирующий вход реверсивного счетчика 25, содержимое которого при этом увеличивается на единицу. Если реверсивный счетчик 25 изменяет свое состояние под действием импульсов, вызванных единичными сбоями, импульсы с выхода счетчика 22 через элемент 24 запрета поступают на вычитающий вход реверсивного счетчика 25 и устанавливают его в нулевое состояние.

Код ноля с выхода реверсивного счетчика 25 поступает на вход дешифратора 26 и на его втором выходе

1

появляется единичный потенциал, кото рый, поступая на инверсный вход второго элемента 24 запрета, запрещает прохождение импульсов с выхода.счетчика 22 на вычитающий вход реверсивного счетчика 25. Этим предотвращает ся его отрицательное переполнение. Если реверсивный счетчик 25 изменяет свое состояние под действием им пульсов с выхода блока 13 сравнения„ которые обусловлены отказом аппаратуры, несмотря на поступающие на вычитающий вход реверсивного счетчика 25 импульсы с выхода счетчика 22 (частота которых ниже), число,содержащееся в реверсивном счетчике 25, будет увеличиваться.

В конечном итоге это приведет к появлению единичного потенциала на выходе его старшего разряда, который является выходом блока 14 обнаружения отказа и подключен к вьгходу 18 индикации отказа. Когда число, содержащееся в реверсивном счетчике 25, достигнет своего максимального значения, на первом выходе дешифратора 26 появится единичный потенциал, которьй, поступая на инверсный вход первого элемента 23 запрета, запретит прохождение импульсов с первого входа 19 блока 1А на суммирующий вход реверсивного счетчика 25 Этим предотвращается его положительное переполнение.

В момент первоначального подключения устройства к питающему напряжению состояние реверсивного счетчика 25 может установиться произвольньм, как и состояние всех элементов задержки 2-1 - 2-м. Поэтому во время вхож,цения цифрового нерекурсивного фильтра 1 в рабочий режим выход 18 индикации отказа будет сигнализировать о недостоверности информации на информационном входе 19. Однако в процессе работы (при условии, что все блоки функционируют нормально) реверсивный счетчик 25 будет установлен в нулевое состояние сигналами, поступающими на второй вход 20 блока 14 обнаружения отказа.

Формула изобретения

1. Устройство для контроля цифровых нерекурсивных фильтров, содержащее последовательно соединенныег блок сравнения и блок обнаружения

43556

отказов, выход которого является выходом индикации отказа, отличающееся тем, что, с целью повышения качества контроля путем обнаружения многократных сбоев, дополнительно введены последовательно соединенные умножитель,вход которого является входом подключения входа то цифрового нерекурсивного фильтра и информационным входом устройства для контроля цифровых нерекурсивных фильтров, и накапливающий сумматор, выход которого соединен с первыми

15 сигнальными входами блока сравнения, последовательно соединенные счетчик и блок памяти коэффициентов, выход которого соединен с другим входом умножителя, последовательно соеди20 ненные дешифратор,входы которого соединены с соответствующими выходами счетчика, и элемент И, выход которого соединен с управляющим входом блока сравнения, блок запрета, пря25 мой вход . которого соединен с выходом дешифратора, а выход соединен с вторым входом блока обнаружения отказов и с установочным входом накапливающего сумматора, а также блок

30 памяти выходного сигнала, вход которого является входом для подключения выхода цифрового нерекурсивного фильтра, выход соединен с вторыми сигнальными входами блока сравнения и явля2g ется информационным выходом устройства для контроля цифровых нерекурсивных фильтров, а тактовый вход объединен с входом счетчика, с тактовым входом накапливающего сумматора,

40 с вторым входом элемента И, с инверсным входом блока запрета и является тактовым входом устройства для конт-- роля цифровых нерекурсивных фильтров и цифрового нерекурсивного фильт45 ра,

2. Устройство по п.1, о т л и - чающееся тем, что блок обнаружения отказов содержит первый

50 элемент запрета, прямой вход которого является первым входом блока обнаружения отказов, второй элемент запрета, счетчик, вход которого является вторым входом блока обнаруже55 ния отказов, а выход соединен с прямым входом второго элемента запрета, дешифратор, первый и второй выходы которого соединены с инверсными входами соответственно первого и Бторого элементов запрета,- а также реверсивный счетчик,суммирующий вход которого соединен с выходом первого элемента запрета, вычитающий вход соединен с выходом второго элемента запрета, а выходы соединены с соответствующими входами дешифратора, при этом выход старшего разряда реверсивного счетчика является выходом блока обнаружения отказов. 3. Устройство по п.1, отличающееся тем, что блок срав3556

10

нения содержит элемент ИЛИ, элемент ;И и К элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первые входы которых являются первыми сигнальными входами блока сравнения, вторые входы являются вторыми сигнальными входами блока сравнения, а выходы через элемент ИЛИ соединены с первым входом элемента И, второй вход которого является управляющим входом блока сравнения, а выход является выходом блока сравнения.

«Рие.З

От И

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых нерекурсивных фильтров | 1986 |

|

SU1406731A1 |

| Цифровой нерекурсивный фильтр | 1987 |

|

SU1483608A1 |

| Устройство для обработки радиосигналов | 1980 |

|

SU955083A1 |

| Цифровой нерекурсивный фильтр | 1986 |

|

SU1332519A1 |

| Цифровой нерекурсивный фильтр | 1985 |

|

SU1352622A1 |

| Нерекурсивный цифровой фильтр | 1983 |

|

SU1322421A1 |

| Цифровой нерекурсивный фильтр нечетного порядка | 1985 |

|

SU1314445A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1988 |

|

SU1589383A1 |

| Специализированный процессор для цифровой фильтрации | 1989 |

|

SU1631558A1 |

| Цифровой фильтр | 1983 |

|

SU1145346A1 |

Изобретение обеспечивает повышение качества контроля путем обнаружения многократных сбоев. Устр-во содержит блок 5 памяти выходного сигнала, счетчик 6 по модулю М+1, блок 7 памяти коэф., умножитель 8 накапливающий сумматор 9, дешифратор 10, эл-т И 11, блок 12 запрета, блок 13 сравнения, блок 14 обнаружения отказа, информац.вход 15, тактовый вход 16, информац.выход 17, выход 18 индикации отказов, входы 19 и 20 и выход 21 блока 14. Блок 14 содержит счетчик, два эл-та запрета, реверсивный счетчик и дешифратор . Блок 13 содержит эл-ты ИСКЛЮЧАЮЩЕЕ ИЛИ, эл-т ИЛИ, эл-т И. 2 з,п. ф-лы, 3 ил. СЛ

Авторы

Даты

1987-10-07—Публикация

1986-04-18—Подача