Ё Е

TtT

Cm

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1987 |

|

SU1437982A1 |

| Устройство для извлечения квадратного корня | 1986 |

|

SU1388856A1 |

| Логарифмический преобразователь | 1986 |

|

SU1381498A1 |

| Умножитель частоты следования импульсов | 1977 |

|

SU705657A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1988 |

|

SU1587624A1 |

| Измерительный двухфазный генератор | 1987 |

|

SU1442931A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Цифровой фильтр | 1986 |

|

SU1387174A1 |

| Вычислительное устройство | 1978 |

|

SU742930A1 |

| Устройство для управления перемоточным станком | 1982 |

|

SU1087594A1 |

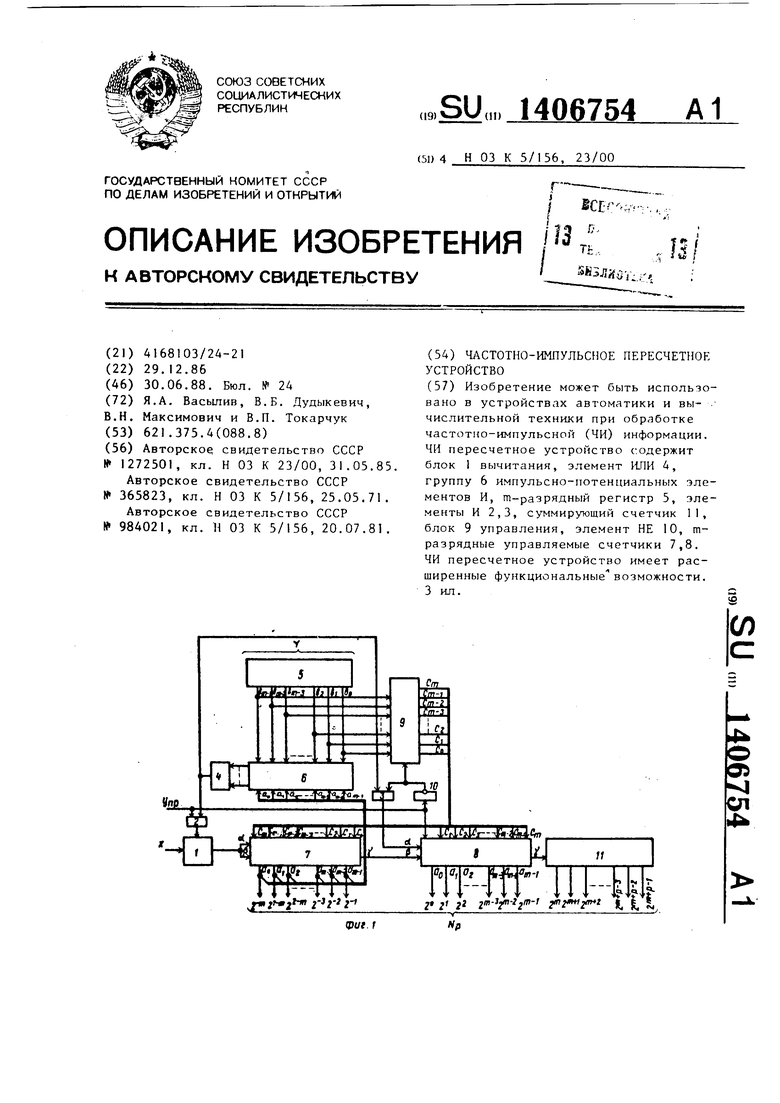

Изобретение может быть использовано в устройствах автоматики и вычислительной техники лри обработке частотно-импульсной (ЧИ) информации. ЧИ пересчетное устройство с .одержит блок 1 вычитания, элемент ИЛИ 4, группу 6 импульсно-потенциальных элементов И, т-разрядный регистр 5, элементы И 2,3, суммирующий счетчик II, блок 9 управления, элемент НЕ 10, га- разрядные управляемые счетчики 7,8. ЧИ пересчетное устройство имеет расширенные функциональные возможности. 3 ил. (О

9по

Ta.fa.

h

iC.fr..luJti.,-4fAif.

IPlllIt

фиг. r

Ifl

1

ICfJCjJ/ r- Slfin iJ

О Od

СЛ

4i

11

тнгг ттрж

2 г г im-Jf -f2 - H I. S,

Wfl

1

Изобретение относится к импульсно технике и может быть использовано в устройствах автоматики и вычислительной техники при обработке частотно-импульсной информации.

Цель изобретения - расширение функциональных возможностей путем обеспечения дополнительно возможност выполнения операции умножения.

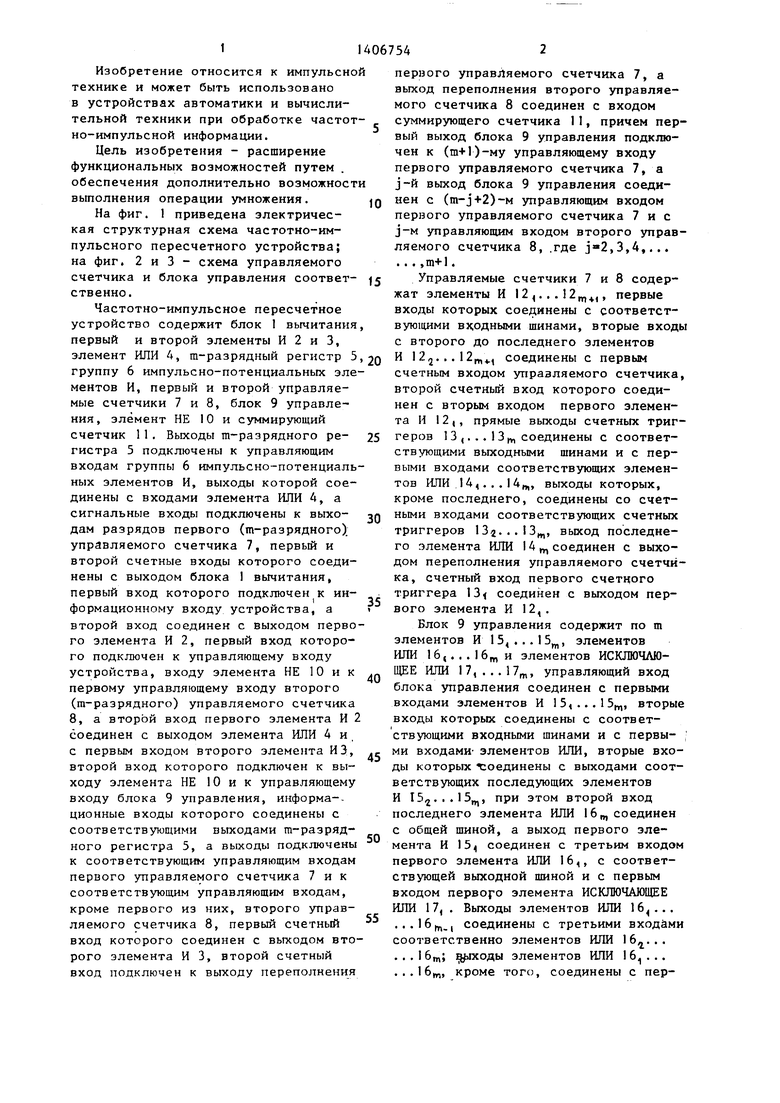

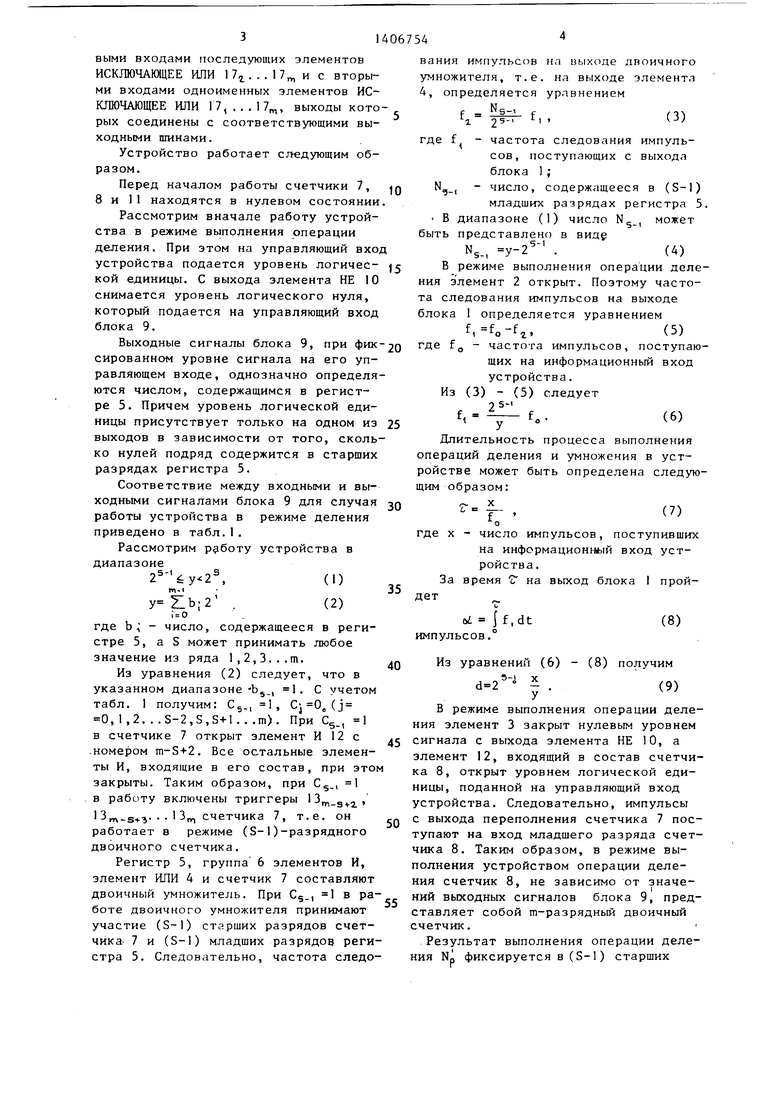

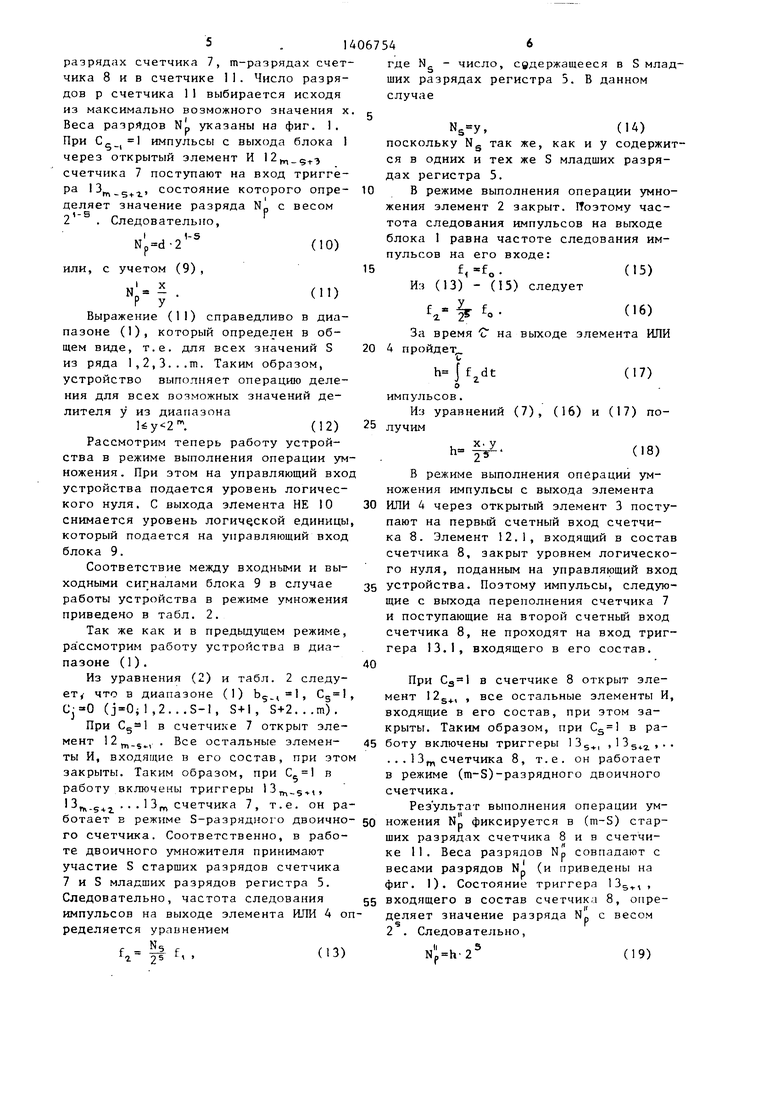

На фиг. 1 приведена электрическая структурная схема частотно-импульсного пересчетного устройства; на фиг. 2 и 3 - схема управляемого счетчика и блока управления соответственно.

Частотно-импульсное пересчетное устройство содержит блок 1 вычитания первый и второй элементы И 2 и 3, элемент ИЛИ 4, т-разрядный регистр З группу 6 импульсно-потенциальных элементов И, первый и второй управляемые счетчики 7 и 8, блок 9 управления, элемент НЕ 10 и суммирующий счетчик 11. Выходы т-разрядного регистра 5 подключены к управляющим входам группы 6 импульсно-потенциальных элементов И, выходы которой соединены с входами элемента ИЛИ 4, а сигнальные входы подключены к выходам разрядов первого (т-разрядного) управляемого счетчика 7, первый и второй счетные входы которого соединены с выходом блока 1 вычитания, первый вход которого подключен к информационному входу устройства, а второй вход соединен с выходом первого элемента И 2, первый вход которого подключен к управляющему входу устройства, входу элемента НЕ 10 и к первому управляющему входу второго (га-разрядного) управляемого счетчика 8, а второй вход первого элемента И соединен с выходом элемента ИЛИ 4 и с первым входом второго элемента ИЗ, второй вход которого подключен к выходу элемента НЕ 10 и к управляющему входу блока 9 управления, информа-- ционные входы которого соединены с соответствующими выходами т-разрядного регистра 5, а выходы подключены к соответствующим управляющим входам первого управляемого счетчика 7 и к соответствующим управляющим входам, кроме первого из них, второго управляемого счетчика 8, первый счетный вход которого соединен с выходом второго элемента И 3, второй счетный вход подключен к выходу переполнения

0

5

5

п

0

5

0

5

0

5

первого управляемого счетчика 7, а выход переполнения второго управляемого счетчика 8 соединен с входом суммирующего счетчика 11, причем первый выход блока 9 управления подключен к (т+1)-му управляющему входу первого управляемого счетчика 7, а jй выход блока 9 управления соединен с (m-j+2)-M управляющим входом первого управляемого счетчика 7 и с JM управляющим входом второго управляемого счетчика 8, .где ,3,4,... ...,m+l.

Управляемые счетчики 7 и 8 содержат элементы И 12 ,...12,, первые входы которых соединены с соответст- вуюнщми входными щинами, вторые входы с второго до последнего элементов И 122... 12„., соединены с первым счетным входом управляемого счетчика, второй счетный вход которого соединен с вторым входом первого элемента И 12,, прямые выходы счетных триггеров 13 ,...13 соединены с соответствующими выходными щинами и с первыми входами соответствующих элементов ИЛИ 14...I4, выходы которых, кроме последнего, соединены со счетными входами соответствующих счетных триггеров 13...13, выход последнего элемента ИЛИ 14 соединен с выходом переполнения управляемого счетчика, счетный вход первого счетного триггера 13 соединен с выходом первого элемента И 12,.

Блок 9 управления содержит по m элементов И 15,...15, элементов ИЛИ 16,...16„ и элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 17,...17, управляющий вход блока управления соединен с первыми входами элементов И 15,...15, вторые входы которых соединены с соответствующими входными шинами и с первы- ми входами- элементов ИЛИ, вторые входы которых Соединены с выходами соответствующих последующих элементов И 15...5, при этом второй вход последнего элемента ИЛИ 16 соединен с общей щиной, а выход первого элемента И 5 соединен с третьим входом первого элемента ИЛИ 16,, с соответствующей выходной щиной и с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 17, . Выходы элементов ИЛИ 16... ...16., соединены с третьими входами соответственно элементов ИЛИ 16... ... 1 6nv; 13 аходы элементов ИЛИ 16 ... ...16, кроме того, соединены с первыми входами последующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 17 . . . I7 и с вторыми входами одноименных элементов ИСКЛЮЧАЮЩЕЕ ИЛИ Г7,..,17„, выходы которых соединены с соответствующими выходными шинами.

Устройство работает следующим образом.

Перед началом работы счетчики 7, 8 и 11 находятся в нулевом состоянии

Рассмотрим вначале работу устройства в режиме выполнения рлерации деления. При этом на управляющий вхо устройства подается уровень логичес- кой единицы. С выхода элемента НЕ 10 снимается уровень логического нуля, который подается на управляющий вход блока 9.

Выходные сигналы блока 9, при фик сированном уровне сигнала на его управляющем входе, однозначно определяются числом, содержащимся в регистре 5. Причем уровень логической единицы присутствует только на одном из выходов в зависимости от того, сколько нулей подряд содержится в старших разрядах регистра 5.

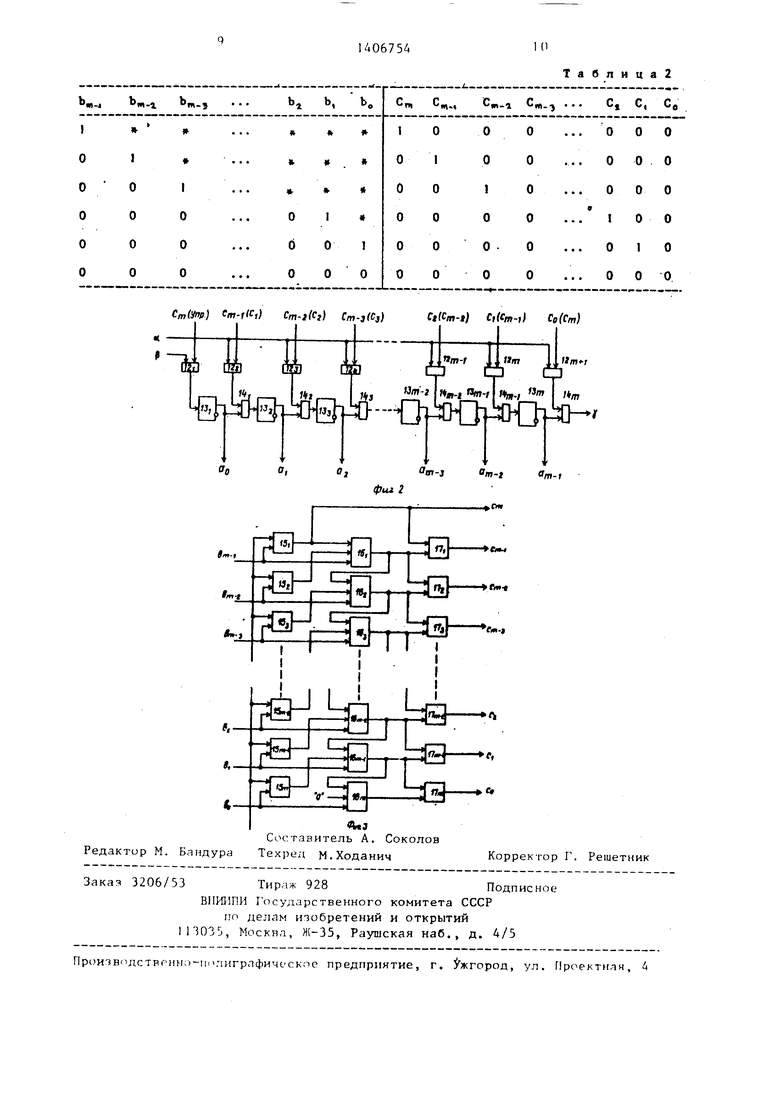

Соответствие между входными и выходными сигналами блока 9 для случая работы устройства в режиме деления приведено в табл.I,

Рассмотрим работу устройства в диапазоне

(1)

(2)

y Z:b;2 ,

где b - число, содержащееся в регистре 5, а S может принимать любое значение из ряда 1,2,3...т.

Из уравнения (2) следует, что в указанном диапазоне -Ь,, 1. С учетом табл. 1 получим: Cj., , ,(j 0, 1 ,2. ..S-2,S,S+1...m). При C., 1 в счетчике 7 открыт элемент И 12 с .номером m-S+2. Все остальные элементы И, входящие в его состав, при это закрыты. Таким образом, при С., 1 в работу включены триггеры . 13„V-s+г- 3,г, счетчика 7, т.е. он работает в режиме (S-1)-разрядного двоичного счетчика.

Регистр 5, группа 6 элементов И, элемент ИЛИ 4 и счетчик 7 составляют двоичный умножитель. При Сд., в работе двоичного умножителя принимают участие (S-1) старших разрядов счетчика. 7 и (S-1) младших разрядов регистра 5. Следовательно, частота следо

вания импульс(1в на выходе двоичного умножителя, т.е. на выходе элемента 4, определяется урлвнением

f NS f 4

(3)

где f - частота следования импульсов, поступающих с выхода блока 1; N - число, содержащееся в (S-1)

младших разрядах регистра 5. В диапазоне (1) число N, может быть представлено в виде

N

S-I

у-2

5-1

(4)

В режиме выполнения операции деления элемент 2 открыт. Поэтому частота следования импульсов на выходе блока 1 определяется уравнением

f,fo-f.

(5)

где fg - частота импульсов, поступающих на информационный вход устройства.

Из (3) - (5) следует 2S-

f, fo.(6)

Длительность процесса выполнения операций деления и умножения в устройстве может быть определена следующим образом:

f- ,(7)

о где X - число импульсов, поступивших

на информационный вход устройства.

За время С на выход блока I пройдет

L

ui jf.dt импульсов.

(8)

г

5

(9)

Из уравнений (6) - (8) получим ,9-i X

У

В режиме выполнения операции деления элемент 3 закрыт нулевым уровнем сигнала с выхода элемента НЕ 10, а элемент 12, входящий в состав счетчика 8, открыт уровнем логической единицы, поданной на управляющий вход устройства. Следовательно, импульсы с выхода переполнения счетчика 7 поступают на вход младшего разряда счетчика 8. Таким образом, в режиме выполнения устройством операции деления счетчик 8, не зависимо от значений выходных сигналов блока 9, представляет собой т-разрядный двоичный счетчик.

Результат выполнения операции деления NP фиксируется в (S-1) старщих

Рз 3,.г

деляет значение разряда N. с

I 1-5

или, с учетом (9) ,

.1 X

Ы„ - .

Р У

Выражение (1) справедливо в диапазоне (1), который определен в общем виде, т.е. для всех значений S из ряда 1,2,3...т. Таким образом, устройство выполняет операцию деления для всех возможных значений делителя у из диапазона

.(12)

Рассмотрим теперь работу устройства в режиме выполнения операции умножения. При этом на управляющий вхо устройства подается уровень логического нуля. С выхода элемента НЕ 10 снимается уровень логической единицы который подается на управляющий вход блока 9.

Соответствие между входными и выходными сигналами блока 9 в случае работы устройства в режиме умножения приведено в табл. 2.

Так же как и в предыдущем режиме, ра ссмотрим работу устройства в диапазоне (1) .

Из уравнения (2) и табл. 2 следует что в диапазоне (1) b

S-

1, С5 1,

(,2...S-I, S+I, S+2...m).

При

мент 12

m-s«-i

в счетчике 7 открыт эле- . Все остальные элеменПри в счетчике 8 открыт элемент I2s, , все остальные элементы И входящие в его состав, при этом закрыты. Таким образом, при С в ра

45 боту включены триггеры 135, ,,

ты И, ВХОДЯЩИЙ в его состав, при этом ... 13, счетчика 8, т.е. он работает

п в режиме (т-5)-разрядного двоичного

закрыты. Таким образом, при С,1 в

работу включены триггеры 13. 13„, счетчика 7

3 тп-S-kl

Т.е. он работает в режиме S-разрядного двоично- 50 ножения Np фиксируется в го счетчика. Соответственно, в работе двоичного умножителя принимают участие S старщих разрядов счетчика 7 и S младших разрядов регистра 5. Следовательно, частота следования импульсов на выходе элемента ределяется уравнением

п в режиме (т-5)-разрядного двоичного

счетчика.

Результат выполнения операции ум(m-S) старщих разрядах счетчика нив счетчике 11. Веса разрядов Np совпадают с

I , г

весами разрядов

N (и приведены на

фиг. 1). Состояние триггера 13д,, 55 входящего в состав счетчика 8, опре- ИЛИ 4 оп- деляет значение разряда N- с весом

Следовательно,

f Ь г 2

f,

(13)

4

где N - число, содержащееся в S младших разрядах регистра 5. В данном случае

,(IA)

поскольку Ng так же, как и у содержится в одних и тех же S младших разрядах регистра 5.

В режиме выполнения операции умножения элемент 2 закрыт. ГТоэтому частота следования импульсов на выходе блока 1 равна частоте следования импульсов на его входе:

f, fo.(15)

Из (13) - (15) следует

f

(16)

За время С на выходе элемента ИЛИ

20 4 пройдет

h J

(17)

(18)

импульсов.

Из уравнений (7), (16) и (17) получим

U У

h у/в режиме выполнения операции умножения импульсы с выхода элемента ИЛИ 4 через открытый элемент 3 поступают на первьм счетный вход счетчика 8. Элемент 12.1, входящий в состав счетчика 8, закрыт уровнем логического нуля, поданным на управляющий вход

устройства. Поэтому импульсы, следующие с выхода переполнения счетчика 7 и поступающие на второй счетньй вход счетчика 8, не проходят на вход триггера 13.1, входящего в его состав.

При в счетчике 8 открыт элемент I2s, , все остальные элементы И, входящие в его состав, при этом закрыты. Таким образом, при С в работу включены триггеры 135, ,,..

... 13, счетчика 8, т.е. он работает

ножения Np фиксируется в

п в режиме (т-5)-разрядного двоичного

счетчика.

Результат выполнения операции ум(m-S) старщих разрядах счетчика нив счетчике 11. Веса разрядов Np совпадают с

I , г

весами разрядов

N (и приведены на

ния Np фиксируется в

Следовательно,

(19)

с учетом .11

7 (18),

.y.

(20)

Выражение (20) так же, как и выражение (11) справедливо для всех возможных значений числа у из диапазо- зона (12).

Формула изобретения

Частотно-импульсное пересчетное устройство, содержащее блок вычитания, первый вход которого подключен к информационному входу устройства, элемент ИЛИ, входы которого соединены с выходами группы импульсно-потен- циальных элементов И, управляющие

входы которой подключены к соответст- 20 элемента И, второй счетный вход подвующим выходам т-разрядного регистра, два элемента И и суммирующий счетчик, отличающееся тем, что, с целью расширения функциональных возможностей, в него введены блок управления, элемент НЕ и два т- разрядиых управляемых счетчика, выходы разрядов первого из которых соединены с сигнальными входами группы импульсно- потенциальных элементов И, а первый и второй счетные входы подключены к выходу блока вычитания, второй вход которого соединен с выходом первого элеbg,b,,b«...Ъп - значения разрядов числа, содержашегося в регистре 5; С««С|,Ci...Cm -. значения выходных сигналов блока 9; t - бе раличное «(начение разряда.

067548

мента И, первый вход которого подключен к управляющему входу устройства, входу элемента НЕ и к первому управляющему входу второго управляемого счетчика, второй вход первого элемента И соединен с выходом элемента ИЛИ и с первым входом второго элемента И, второй вход которого подключен к вы- 1Q ходу элемента НЕ и к управляющему входу блока управления, информационные входы которого соединены с выходами т-раэрядного регистра, а выходы подключены к соответствующим управляю- 15 щим входам первого управляемого счетчика и к соответствующим управляющим входам, кроме первого, второго управляемого счетчика, первый счетньй вход которого соединен с выходом второго

ключен к выходу переполнения первого управляемого счетчика, а выход переполнения второго управляемого счетчика соединен с входом суммирующего

счетчика, причем первый выход блока управления подключен к (т+О-му уп- равляющему входу первого управляемого счётчика, а j-й выход блока управления соединен с ()-M управляющим

входом первого управляемого счетчика и с J-M управляющим входом второго управляемого счетчика, где ,3,4, . ..,m+1.

Таблица

ТаОлица2

| Делитель частоты следования импульсов | 1985 |

|

SU1272501A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| ДИСКРЕТНЫЙ УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ | 0 |

|

SU365823A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для деления | 1981 |

|

SU984021A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-06-30—Публикация

1986-12-29—Подача