00

ел

со

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1985 |

|

SU1311022A1 |

| Система управления вибростендом | 1984 |

|

SU1275396A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1988 |

|

SU1594699A1 |

| Цифровая система управления | 1986 |

|

SU1439531A1 |

| Устройство для измерения фазовых сдвигов | 1984 |

|

SU1226341A1 |

| Цифровой перестраиваемый полосовой фильтр | 1982 |

|

SU1166274A1 |

| Устройство для диагностики и прогнозирования отказов | 1989 |

|

SU1629898A1 |

| Программно-управляемый цифровой фильтр | 1987 |

|

SU1513475A1 |

| Вычислительное устройство | 1984 |

|

SU1280611A1 |

| Способ взвешивания движущихся объектов | 1990 |

|

SU1800269A1 |

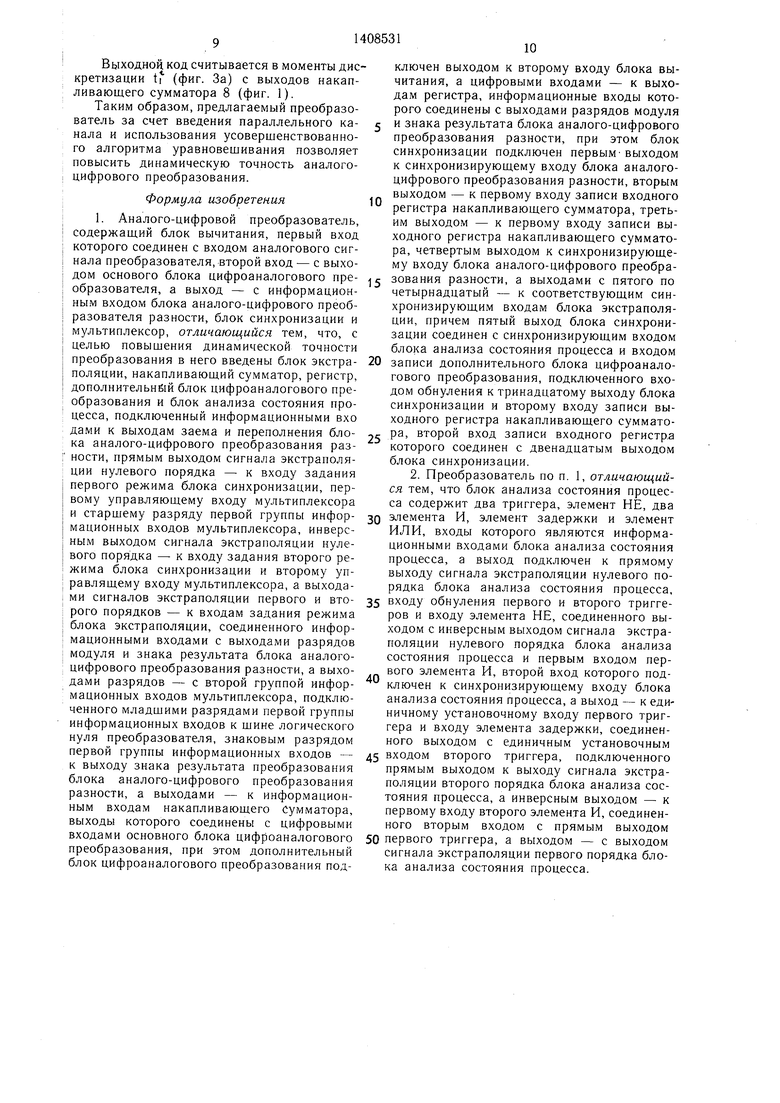

Изобретение относится к автоматике и вычислительной технике. Целью изобретения является повышение динамической точности преобразования. Аналого-цифровой преобразователь содержит блок 1 вычитания, блок 2 аналого-цифрового преобразования разности, два цифроаналоговых преобразователя 3 и 9, блок 4 анализа состояния процесса, блок 5 синхронизации, блок 6 экстраполяции, мультиплексор 7, накапливающий сумматор 8 и регистр 10. Принцип действия преобразователя основан на уравновешивании выходного сигнала с использованием четырех режимов работы: равномерно ступенчатая отработка, следящий, экстраполяция первого или второго порядка. Выбор режима осуществляется блоком 4 анализа состояния процесса в зависимости от значения кода разности блока 2. Использование параллельного канала и миогорежимного характера уравновешивания позволяет повысить динамическую точность аналого-цифрового преобразования. 1 3. п. ф-лы, 8 ил. (Л

//г/

Изобретение относится к автоматике и вычислительной технике и может быть ис- ггользорзаио для нолучения количественной информации о быстропротекаклцнх нроцес- сах.

Целью изобретения является иовьииение динамической точности нреобразования.

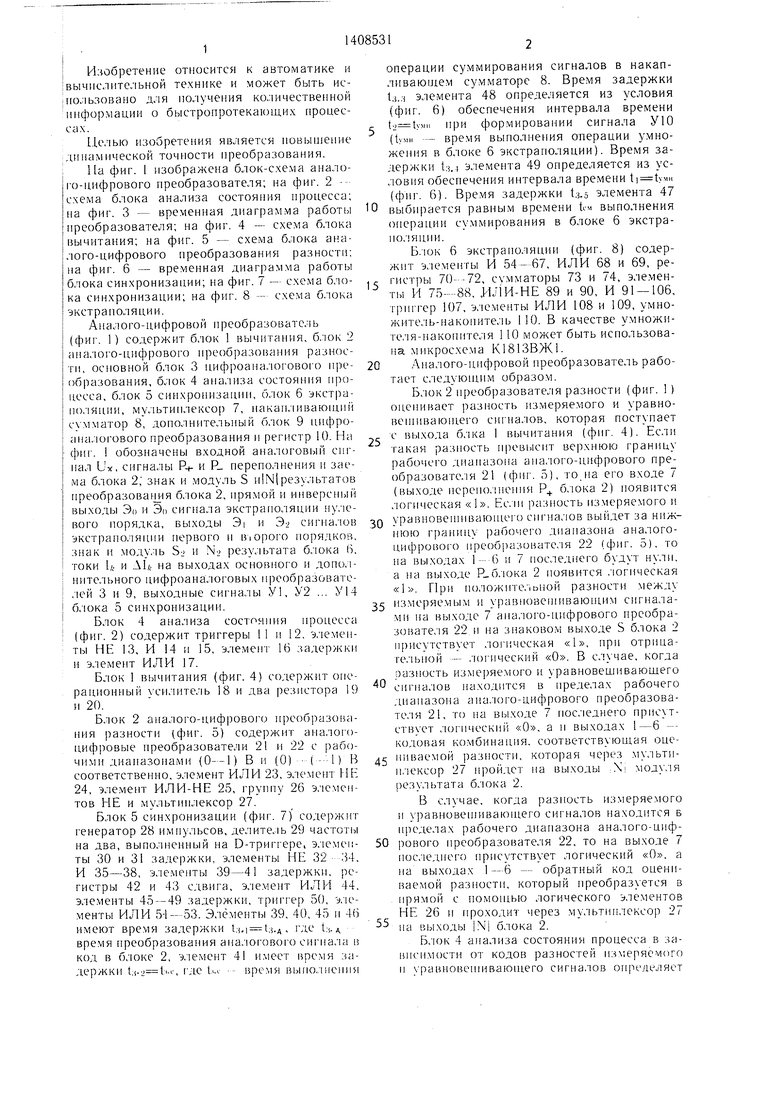

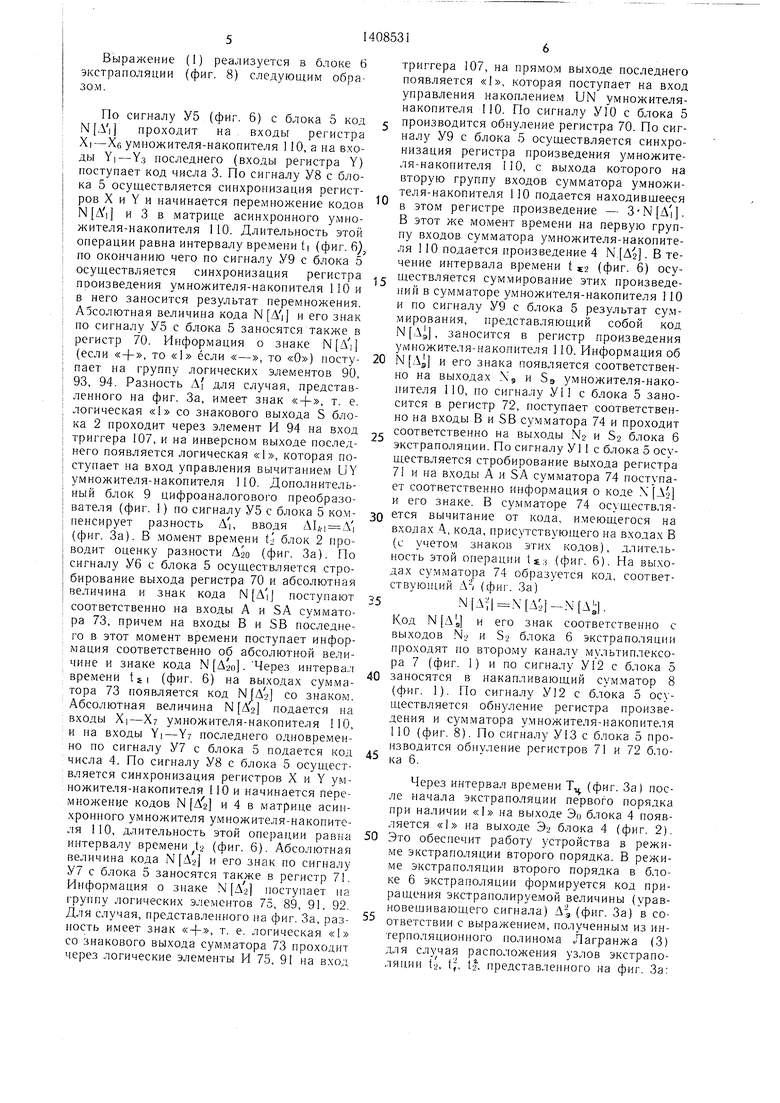

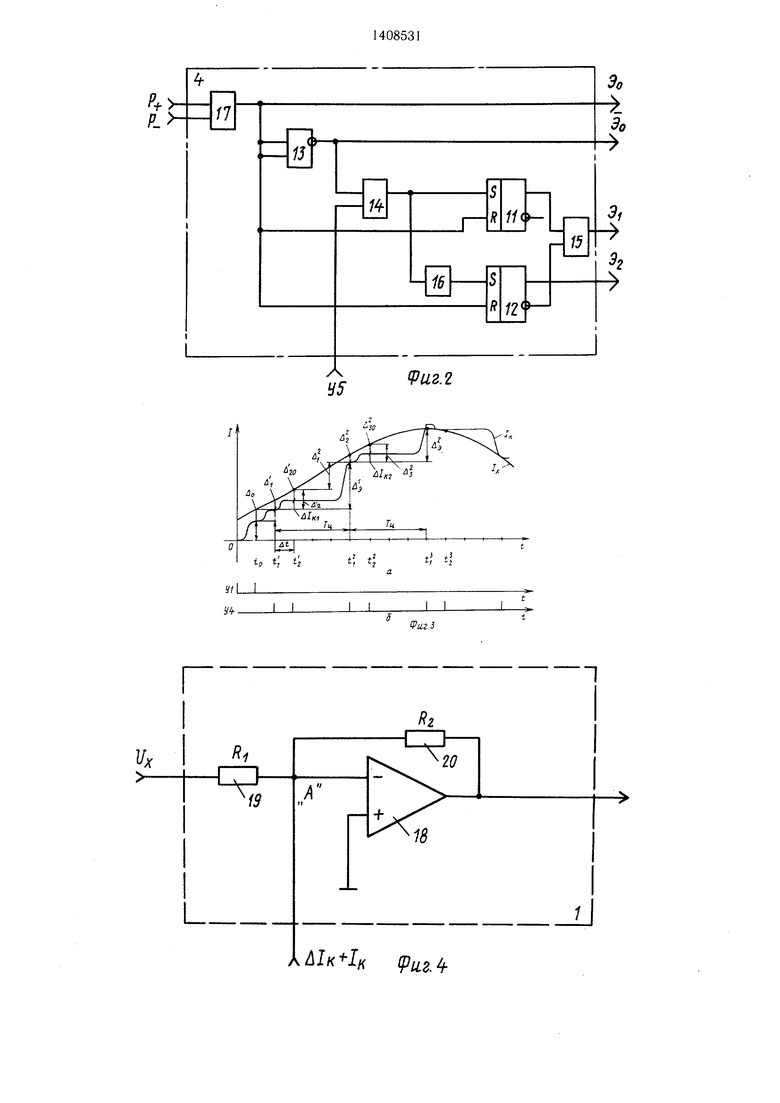

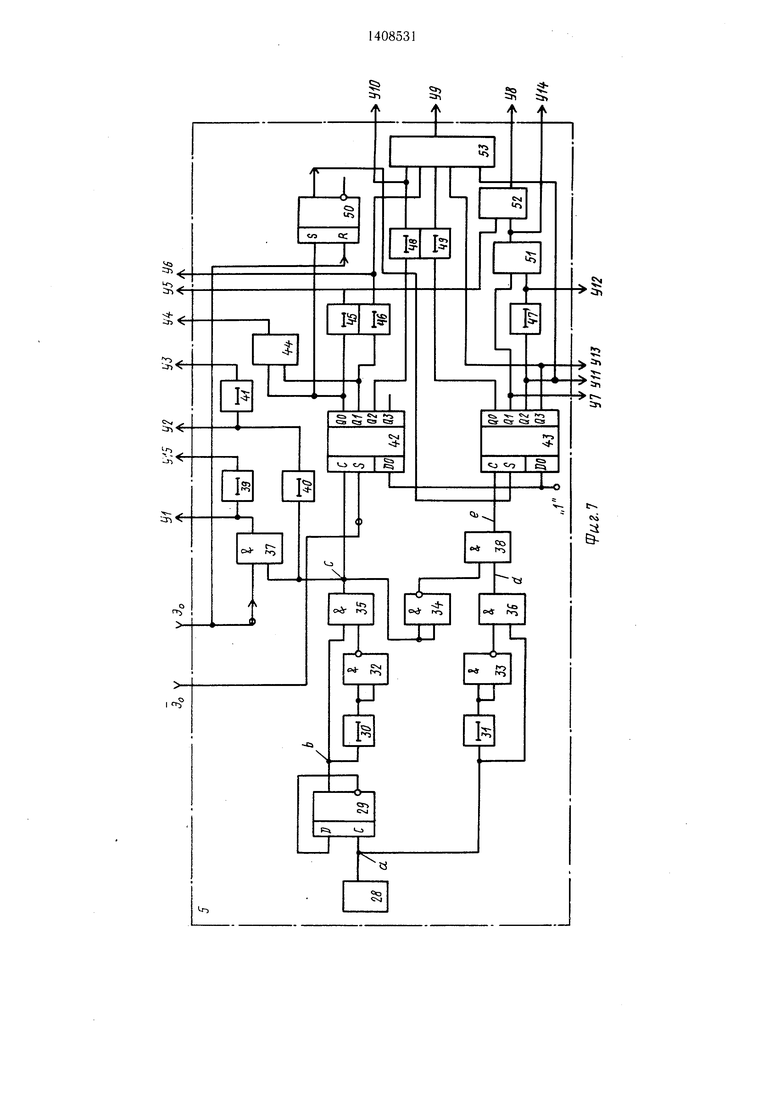

На фиг. I изображена блок-схема анало- i 0-цифрового иреобразователя; на фиг. 2 - схема блока анализа состояния процесса; на фиг. 3 - временная диаграмма работы нреобразователя; иа фиг. 4 - схема блока вычитания; на фнг. 5 - схема блока аналого-цифрового иреобразования разности; иа фиг. 6 - временная диаграмма работы блока синхронизации; на фиг. 7 - схема блока синхронизации; на фиг. 8 - схема б.чока экстраполяции.

А и а л о |-о - ц и ф ро во и 11 р еоб р а з о в ат ел ь (фиг. 1) содержит б. юк 1 вычитания, блок 2 аналого-цифрового нреобразоваиия разности, основной блок 3 цифроа1 а, 1огово1 о нреобразования, блок 4 анализа состояния процесса, блок 5 синхронизации, блок 6 экстра- п(), 1яц|1и, му.льтиилексор 7, накаи, 1иваю1ци| 1 с мматор 8, донолнительный б.чок 9 цифро- аналогового преобразования и регистр 10. На фиг. 1 обозначены входной ana. ioroBijul сигнал Ux, сигналы РЧ- и Р переполнения и зае- ма блока 2, знак и модуль S и1Ы1 результатов иреобразова1пня б,1ока 2, ирямой и инверсный выходы Э() и Эо сигнала экстраполяции ny/ie- вого норядка, выходы Э и Э сигналов экстраполяции первого и Bjoporo иорядков, знак и модуль S и N результата блока 6, токи Ь,. и Л1/. на выходах основного и допол- нптельного цифроаналоговых преобразователей 3 и 9, выходные сигналы У1, У2 ... У14 блока 5 синхронизации.

Блок 4 анализа состояиия ироцесса (фнг. 2) содержит триггеры И и 12, элементы НЕ 13, И 14 п 15, элеме1гг 16 задержкн и элемент ИЛИ 17.

Блок 1 вычитания (фиг, 4) содержит операционный усилитель 18 и ава резистора 19 и 20.

Блок 2 аналого-цифрового иреобразо1 а- ния разности (фиг. 5) содержит аиа, Ю1Ч)- цифровые нреобразователи 21 и 22 с рабочими дианазонами (О-1) В и (0) - (-1) В соответственно, элемент ИЛИ 23, элемент НЕ 24, элемент ИЛИ-НЕ 25, группу 26 элементов НЕ и мультиплексор 27.

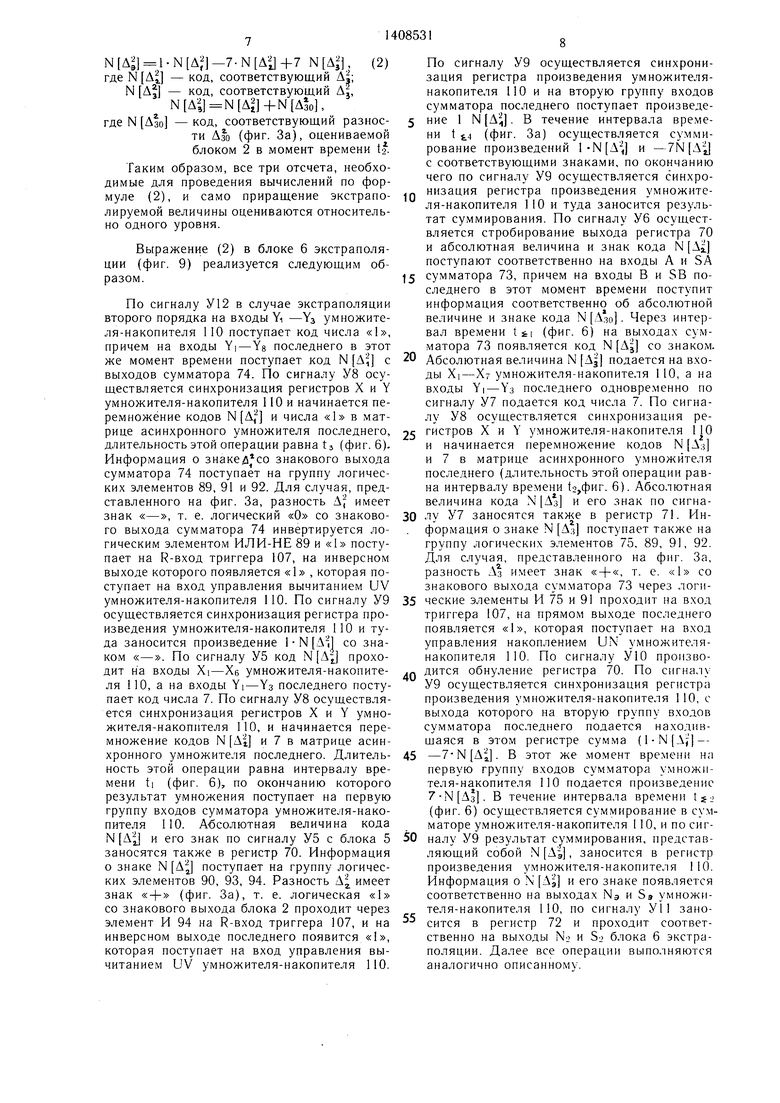

Блок 5 синхронизации (фиг. 7) содержит генератор 28 импульсов, делитель 29 частоты на два, выполпенный иа D-триггере, элемси- ты 30 и 31 задержки, элементы HEi 32 34, И 35-38, элементы 39-41 задержкп, регистры 42 н 43 сдвига, элемент ИЛИ 44, элементы 45-49 задержки, триггер 50, э.ме- менты ИЛИ 5i-53. Элементы 39, 40, 45 и 46 имеют время задержки t;i..i., где t,). д вре.мя преобразования аналогового сигна.ча к код в блоке 2, э. 1емент 41 имеет время задержки t:i., где Ь.1 время выиолиеиия

0

5

0

5

0

5

0

5

операции су.ммирования сигна„1ов в накапливающем сумматоре 8. Время задержки t.s..4 элемента 48 определяется из условия (фиг. 6) обеспечения интервала времени (. нри фор.мировании сигнала У10 (tvMii -- время выполнения операции умно- жеиня в блоке 6 экстраполяции). Время задержки t:i.4 элемента 49 определяется из условия обеспечения интервала времени (фиг. 6). Время задержки t.j.a элемента 47 выбирается равным времени tot выполнения операции суммирования в блоке 6 экстраполяции.

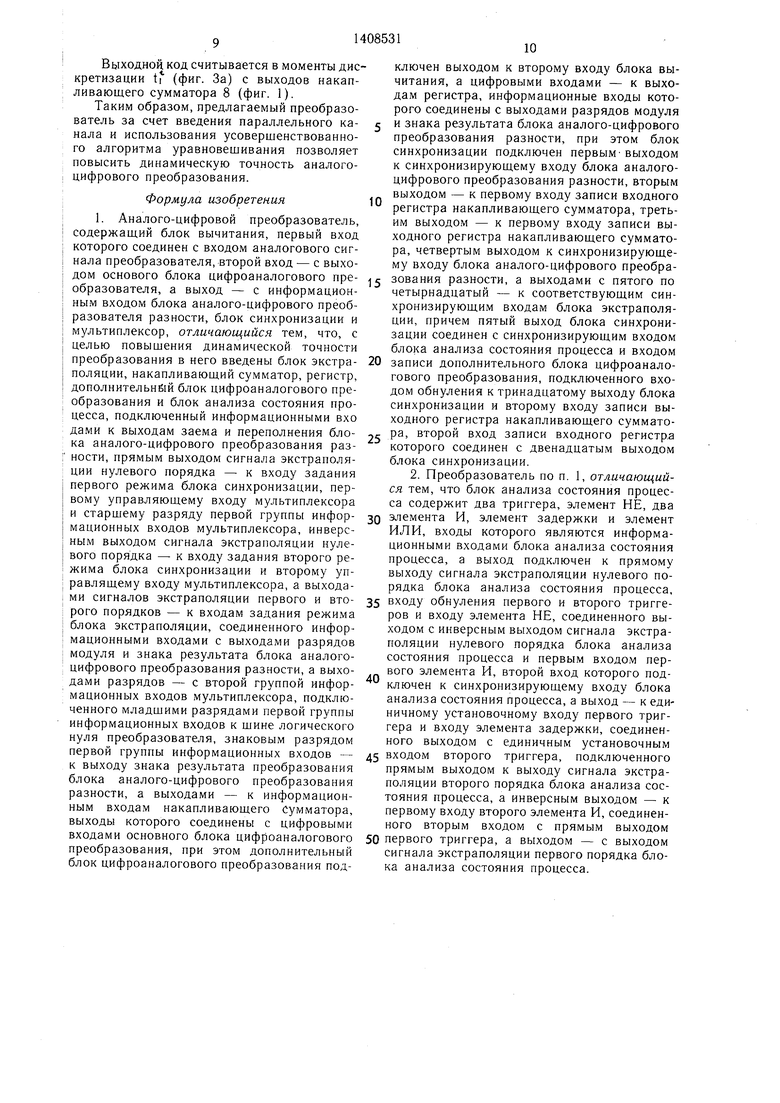

Б.10К 6 экстраиоляцин (фиг. 8) содержит элемепты И , ИЛИ 68 и 69, регистры 70- -72, сумматоры 73 и 74, элементы И 75--88, и1И-НЕ 89 и 90, И 91 - 106, трн1тер 107, элементы ИЛИ 108 и 109, умножитель-накопитель 110. В качестве умножи- теля-иаконителя 1 К) может быть использована микросхема К1813ВЖ1.

Аналого-цифровой преобразователь работает следующим образом.

Блок 2 нреобразователя разности (фиг. 1) оценивает разность измеряемого и уравно- ве1Н1п$аю1цего сш налов, которая поступает с выхода б, 1ка 1 В1)1чнтания (фиг. 4). Если такая разность превыспт верхнюю границу рабочего диаиазона аиа. юго-цифрового преобразователя 21 (фщ-. 5), то,на его входе 7 (выходе перепо.шепия Р.. б.юка 2) появится . югическая «1. Ec.ni разпость из.меряе.мого и уравновеи1иваюи1его сигна. юв выйдет за нижнюю границу рабочего дпапазопа аналого- ци1)рового преобразовате;1я 22 (фиг. 5), то иа выходах 1-6 и 7 последнего будут нули, а на выходе Р блока 2 появится .логическая «1. Ири положительной разности между измеряемым и уравповеп1иваюпи1м сигналами иа выходе 7 аналого-цифрового преобразователя 22 и на знаковом выходе S блока 2 присутствует лоп .ческая «1, при отрицательной - логический «О. В случае, когда разиость измеряе.мого и уравновешивающего си1 на;1ов находится в преде, 1ах рабочего диапазона ана. юго-цифрового преобразователя 21, то на выходе 7 последнего присутствует ,; оп1ческ11Й «О, а п выходах 1-6 --- кодовая ко.мбинация, соответствующая оцениваемой разности, которая через .мультиплексор 27 иройдет иа выходы Д : мод), результата б. юка 2.

В , когда разность измеряемого и уравиове ииваюи1его сигналов находится в пределах рабочего диаиазона аналого-цифрового нреобразователя 22, то на выходе 7 нос.педиего присутствует логический «О, а иа выходах 1-6 - обратный код оценн- ваемой разностн, который иреобразуется в |рямой с номои1ью логического эле.ментов НЕ 26 и проходит через мультиплексор 27 на В121ходы N блока 2.

Б. ЮК 4 анализа состояиия процесса в зависимости от кодов разностей измеряемого п уравновеп1иваюшего сигпалов определяет

один из возможных режимов работы устройства: равномерно ступенчатая отработка, следящий, экстраполяция первого порядка, экстраполяция второго порядка. При наличии логической «1 на выходах переполнения Р. или заема Р (фиг. 5), на выходе Эо блока 4 (фиг. 2) появляется логическая «1, что обеспечивает работу устройства в режиме равномерно-ступенчатой отработки измеряемого сигнала (интервал О-to фиг. 3 а). Оценка разности измеряемого и уравновешивающего сигнала в блоке 2 аналого-цифрового преобразования разности производится по сигналу У1 (фиг. 6) с блока 5 (фиг. 7), если эта разность выходит за рабочий диапазон блока 2, то логическая «1, с выхода Эо блока 4 поступает на первый управляющий вход мультиплексора 7 (фиг. 1), что разрещает прохождение через последний по его первому каналу кода, старший разряд которого - «1 с выхода Эо блока 4, а в остальных разрядах - нули, по знаковому входу первого канала мультиплексора 7 проходит информация о знаке с выхода S блока 2. С выходов мультиплексора 7 код приращения уравновешивающего сигнала со знаком попреобразователь 3 вводит приращение уравновешивающего сигнала, соответствующее разности До (фиг. За).

Если после оценки разности измеряемого

с и уравновещивающего сигналов блоком 2 на выходе Эо появилась логическая «1, то следующее стробирование блока 2 производится по сигналу У4 (фиг. 6) с блока 5, после оценки разности блоком 2 на выходе Э -сохраняется логическая «1, то появляется

0 сигнал У5 (фиг. 6) с блока 5, который установит триггер 11 (фиг. 2) в «1, и на выходе Э| блока 4 появится логическая «1, что обеспечивает работу устройства в режиме экстраполяции первого порядка. При экстра 5 поляции первого и второго порядков стробирование блока 2 производится по сигналу У4 (.фиг. 6) с блока 5, таким образом задается такое расположение узлов экстраполяции tu t-2, что (фиг. За), где Т - время цикла экстраполяции устройства. Сиг20 налы на выходах регистра 43 сдвига (фиг. 7) появляются лишь после появления сигнала «1 на выходе QO регистра 42 сдвига, который устанавливает триггер 50 в «1,.так обеспечивается очередность появления уп30

35

40

ступает по сигналу У2 (фиг. 6) с блока 5 во 25 равляющих сигналов У4-У14, показанная

на фиг. 6.

В режиме экстраполяции первого порядка (интервал t -1 , фиг. За) на выходе блока 6 экстраполяции формируется код приращения уравновешивающего сигна, 1а .Э (фиг. За) в соответствии с выражением, полученным из уравнения для интерполяционного полинома Лагранжа для случая расположения узлов экстраполяции t и t, представленного на фиг. За:

.,()

-код, соответствующий разности

- код, соответствующий разности АЗ.

Дополнительный цифроаналоговый преобразователь 9 по сигналу У5 (фиг. 6) с блока 5 компенсирует разность измеряемого и уравновешивающего сигналов в моменты времени t . Это приводит к уменьще- нию абсолютной величины разности, оце.- нивае.мой блоком 2 в моменты времени t . Разнрсти, оцениваемые в моменты времени tf и Ь (фиг. За), необходимо привести к одному уровню, относительно которого вводится и приращение экстраполируемой величины. В связи с этим

N A;o +N4Ai, где N AM -код, соответствующий разности А зо, оцениваемой блоком 2 в момент времени t (фиг. За). В конце каждого такта экстраполяции по сигналу У13 (фиг. 6) с блока 5 обнуляется дополнительный цифроаналогОвый преобразователь 9, а основной цифроаналоговый пре образователь 3 вводит соответствующее приращение уравновешивающей величины.

входной регистр накапливающего сумматора 8 (прибавляется к содержимому последнего, если на выходе S-1, и вычитается, если «О), затем по сигналу УЗ (фиг. 6) с блока 5 стробируется выходной регистр накапливающего сумматора 8, и основной цифроаналоговый преобразователь 3 вводит приращение уравновещивающего сигнала Ьмакс (фиг. 3 а).

В случае, когда разность уравновещивающего и измеряемого сигналов находится в пределах рабочего диапазона блока 2, то на выходах Р и Р блока 2 присутствуют логические нули, а на выходе Эо блока 4 (фиг. 2) появится логическая «1. Эта «1 поступает на второй управляющий вход мультиплексора 7, что разрешает прохождение по второму каналу последнего информации об абсолютной величине и знаке приращения уравновешиваюплего сигнала соответственно с выходов N-2 и $2 блока 6 экстраполяции.

Если стробирование блока 2 аналого- цифрового преобразования разности было произведено по сигналу У1 (фиг. 6) с блока 5, а после оценки разности измеряе.мого и уравновешивающего сигналов блоком2 на выходе Эо появляется логическая «1, то устройство работает в следующем режиме (интервал to-ti, фиг. За), т. е. по сигналу У5 (фиг. 6) с блока 5 информация с выходов iNi и S блока 2 пройдет на выходы блока 6 экстраполяции, а затем по второму каналу мультиплексора 7 и по сигналу У2 (фиг. 6) с блока 5 занесется во входной регистр сумматора 8. По сигналу УЗ (фиг. 6) с блока 5 стробируется выходной регистр сумматора 8 и основной цифроаналоговый

45

50

55

преобразователь 3 вводит приращение уравновешивающего сигнала, соответствующее разности До (фиг. За).

Если после оценки разности измеряемого

и уравновещивающего сигналов блоком 2 на выходе Эо появилась логическая «1, то следующее стробирование блока 2 производится по сигналу У4 (фиг. 6) с блока 5, после оценки разности блоком 2 на выходе Э -сохраняется логическая «1, то появляется

0 сигнал У5 (фиг. 6) с блока 5, который установит триггер 11 (фиг. 2) в «1, и на выходе Э| блока 4 появится логическая «1, что обеспечивает работу устройства в режиме экстраполяции первого порядка. При экстра5 поляции первого и второго порядков стробирование блока 2 производится по сигналу У4 (.фиг. 6) с блока 5, таким образом задается такое расположение узлов экстраполяции tu t-2, что (фиг. За), где Т - время цикла экстраполяции устройства. Сиг0 налы на выходах регистра 43 сдвига (фиг. 7) появляются лишь после появления сигнала «1 на выходе QO регистра 42 сдвига, который устанавливает триггер 50 в «1,.так обеспечивается очередность появления упВыражение (1) реализуется в блоке 6 экстраполяции (фиг. 8) следующим образом.

По сигналу У5 (фиг. 6) с блока 5 код проходит на . входы регистра Х|-Хб умножителя-накопителя 1 10, а на в.хо- ды YI-Y.-j последнего (входы регистра У) поступает код числа 3. По сигналу У8 с блока 5 осупдествляется синхронизация регистров X и У и начинается перемножение кодов NfA i и 3 в матрице асинхронного умножителя-накопителя 110. Длительность этой операции равна интервалу времени ti (фиг. б) по окончанию чего по сигналу У9 с блока 5 осуществляется синхронизация регистра произведения умножителя-накопителя 110 и в него заносится результат перемножения. Абсолютная величина кода и его знак по сигналу У5 с блока 5 заносятся также в регистр 70. Информация о знаке )j (если « + , то «I если «-, то «О) поступает на группу логически.х элементов 90, 93, 94. Разность Д для случая, представленного на фиг. За, имеет знак «-|-. т. е. логическая «1 со знакового выхода S блока 2 проходит через элемент И 94 на вход триггера 107, и на инверсном выходе последнего появляется логическая «1, которая поступает на вход управления вычитанием УУ умножителя-накопителя НО. Дополнительный блок 9 цифроаналогового преобразователя (фиг. ) по сигналу У5 с блока 5 компенсирует разность Л |, вводя (фиг. За). В момент времени t: блок 2 проводит оценку разности Дао (фиг. За). По сигналу У6 с блока 5 осуществляется стро- бирование выхода регистра абсолютная величина и знак кода поступают соответственно на входы А и SA сумматора 73, причем на входы В и SB последнего в этот момент времени поступает информация соответственно об абсолютной величине и знаке кода . Через интервал времени (фиг. 6) на выходах сумматора 73 появляется код со знако.ад. Абсолютная величина N Д о подается на входы Х|-Х умножителя-накопителя 110, и на входы последнего одновременно по сигналу У7 с блока 5 подается код числа 4. По сигналу У8 с блока 5 осуществляется синхронизация регистров X и У умножителя-накопителя 110 и начинается перемножение кодов N Д 2 и 4 в матрице асинхронного умножителя умножителя-накопите- . 1Я 110, длительность этой операции равна интервалу времени ta (фиг. 6). Абсолютная величина кода N Да и его знак по сигналу У7 с блока 5 заносятся также в регистр 71. Информация о знаке N Да поступает на группу логических элементов 75, 89, 91. 92. Для случая, представленного на фиг. За, разность имеет знак «+, т. е. логическая «1 со знакового выхода сум.матора 73 проходит через логические элементы И 75, 91 на вход

5

триггера 107, на прямом выходе последнего появляется «1, которая поступает на вход управления накоплением UN умножителя- накопителя 110. По сигналу У10 с блока 5

производится обнуление регистра 70. По сигналу У9 с блока 5 осуществляется синхронизация регистра произведения умножителя-накопителя ПО, с выхода которого на вторую группу входов сумматора умножителя-накопителя 110 подается находивщееся

в этом регистре произведение - . В этот же момент времени на первую группу входов сумматора умножителя-накопителя 110 подается произведение 4 . В течение интервала времени t 52 (фиг. 6) осуг ществляется суммирование этих произведений в сумматоре умножителя-накопителя 110 и по сигналу У9 с блока 5 результат сум- .мирования, представляющий собой код , заносится в регистр произведения умножителя-накопителя 110. Информация об

0 и его знака появляется соответственно на выходах Х э и 5э умножителя-накопителя 110, по сигналу УП с блока 5 заносится в регистр 72, поступает соответственно на входы В и SB сумматора 74 и проходит соответственно на выходы .N2 и Sa блока 6 экстраполяции. По сигналу У11 с блока 5 осуществляется стробирование выхода регистра 71 и на входы А и SA сумматора 74 поступает соответственно информация о коде . и его знаке. В су.мматоре 74 осуществля0 ется вычитание от кода, и.меющегося на входах А, кода, присутствующего на входах В (с учетом знаков этих кодов), длительность этой операции (фиг. 6). На выходах сумматора 74 образуется код, соответствующий (фиг. За)

.

Код и его знак соответственно с выходов .N2 и За блока 6 экстраполяции проходят по второму каналу мультиплексора 7 (фиг. 1) и по сигналу У12 с блока 5

0 заносятся в накапливающий сумматор 8 (фиг. 1). По сигналу У12 с блока 5 осуществляется обнуление регистра произведения и сумматора умножителя-накопителя 110 (фиг. 8). По сигналу У13 с блока 5 производится обнуление регистров 71 и 72 бло КЗ 6.

Через интервал вре.мени Т. (фиг. За) после начала экстраполяции первого порядка при наличии «1 на выходе Эц блока 4 нояв- ляется «1 на выходе Эа блока 4 (фиг. 2). 0 Это обеспечит работу устройства в режиме экстраполяции второго порядка. В режиме экстраполяции второго порядка в блоке 6 экстраполяции формируется код приращения экстраполируемой величины (уравновешивающего сигнала) Д| (фиг. За) в соответствии с выражением, полученны.м из интерполяционного полинома Лагранжа (3) для случая расположения узлов экстраполяции (2, t, {2, представленного на фиг. За:

5

N Д, (2) где N AI - код, соответствующий N Д| - код, соответствующий д,

, где N Дзо - код, соответствующий разности Дзо (фиг. За), оцениваемой блоком 2 в момент времени tfТаким образом, все три отсчета, необходимые для проведения вычислений по формуле (2), и само приращение экстраполируемой величины оцениваются относительно одного уровня.

Выражение (2) в блоке 6 экстраполяции (фиг. 9) реализуется следующим образом.

По сигналу У12 в случае экстраполяции второго порядка на входы Yi умножителя-накопителя 110 поступает код числа «1, причем на входы YI-Yg последнего в этот

10

По сигналу У9 осуществляется синхронизация регистра произведения умножителя- накопителя 110 и на вторую группу входов сумматора последнего поступает произведение 1 Ы(Д. В течение интервала времени t (фиг. За) осуществляется суммирование произведений , и с соответствующими знаками, по окончанию чего по сигналу У9 осуществляется синхронизация регистра произведения умножителя-накопителя 110 и туда заносится результат суммирования. По сигналу У6 осуществляется стробирование выхода регистра 70 и абсолютная величина и знак кода N Д поступают соответственно на входы А и SA 5 сумматора 73, причем на входы В и SB последнего в этот момент времени поступит информация соответственно об абсолютной величине и знаке кода N Азо. Через интервал времени tii (фиг. 6) на выходах сумматора 73 появляется код N Дз со знаком.

же момент времени поступает код N Д, с 20 Абсолютная величина N Д| подается на вховыходов сумматора 74. По сигналу У8 осуществляется синхронизация регистров X и Y умножителя-накопителя 110 и начинается перемножение кодов и числа «1 в матрице асинхронного умножителя последнего, длительность этой операции равна 1з (фиг. 6). Информация о знакей со знакового выхода сумматора 74 поступает на группу логических элементов 89, 91 и 92. Для случая, представленного на фиг. За, разность Д; имеет знак «-, т. е. логический «О со знакового выхода сумматора 74 инвертируется логическим элементом ИЛИ-НЕ 89 и «I поступает на R-вход триггера 107, на инверсном выходе которого появляется «1 , которая поступает на вход управления вычитанием UV умножителя-накопителя 110. По сигналу У9 осуществляется синхронизация регистра произведения умножителя-накопителя 110 и туда заносится произведение со знаком «-. По сигналу У5 код проходит н а входы Xi-Хб умножителя-накопителя 110, а на входы YI-Ya последнего поступает код числа 7. По сигналу У8 осуществляется синхронизация регистров X и Y умножителя-накопителя ПО, и начинается перемножение кодов N Ai и 7 в матрице асинхронного умножителя последнего. Длительность этой операции равна интервалу времени ti (фиг. 6), по окончанию которого результат умножения поступает на первую группу входов сумматора умножите.ая-нако- пителя 110. Абсолютная величина кода

ды Xi-Ху умножителя-накопителя 1 10, а на входы YI-Y3 последнего одновременно по сигналу У7 подается код числа 7. По сигналу У8 осуществляется синхронизация репс гистров X и Y умножителя-накопителя 110 и начинается перемножение кодов N Дз и 7 в матрице асинхронного умножителя последнего (длительность этой операции равна интервалу времени 12,фиг. 6). Абсолютная величина кода и его знак по сигна- 30 лу У7 заносятся также в регистр 71. Информация о знаке N Дз поступает также на группу логических элементов 75, 89, 91, 92. Для случая, представленного на фиг. За, разность Дз имеет знак «-{-«, т. е. «1 со знакового выхода сумматора 73 через логи- 35 ческие элементы И 75 и 91 проходит на вход триггера 107, на прямом выходе последнего появляется «1, которая поступает на вход управления накоплением UN умножителя- накопителя 110. По сигналу У10 пропзво- дд дится обнуление регистра 70. По сигналу У9 осуществляется синхронизация регистра произведения умножителя-накопителя 110, с выхода которого на вторую группу входов сумматора последнего подается находившаяся в этом регистре сумма ( 45 . В этот же момент времени на

первую группу входов сумматора умножителя-накопителя ПО подается произведение . В течение интервала времени tji (фиг. 6) осуществляется суммирование в сумматоре умножителя-накопителя 110, и по сигМ Д и его знак по сигналу У5 с блока 5 50 налу У9 результат суммирования, предстаг заносятся также в регистр 70. Информацияляющий собой N Дэ, заносится в регистр

произведения умножителя-накопителя 110. Информация о N Дэ и его знаке появляется

знак «-|- (фиг. За), т. е. логическая «1

со знакового выхода блока 2 проходит через

Эv eмeнт И 94 на R-вход триггера 107, и на

о знаке поступает на группу логических элементов 90, 93, 94. Разность Д; имеет

55

инверсном выходе последнего появится «1, которая поступает на вход управления вычитанием UV умножителя-накопителя 110.

соответственно на выходах Ng и 5э умножителя-накопителя 110, по сигналу УМ заносится в регистр 72 и проходит соответственно на выходы .NO и So блока 6 экстраполяции. Далее все операции выполняются аналогично описанному.

По сигналу У9 осуществляется синхронизация регистра произведения умножителя- накопителя 110 и на вторую группу входов сумматора последнего поступает произведение 1 Ы(Д. В течение интервала времени t (фиг. За) осуществляется суммирование произведений , и с соответствующими знаками, по окончанию чего по сигналу У9 осуществляется синхронизация регистра произведения умножителя-накопителя 110 и туда заносится результат суммирования. По сигналу У6 осуществляется стробирование выхода регистра 70 и абсолютная величина и знак кода N Д поступают соответственно на входы А и SA сумматора 73, причем на входы В и SB последнего в этот момент времени поступит информация соответственно об абсолютной величине и знаке кода N Азо. Через интервал времени tii (фиг. 6) на выходах сумматора 73 появляется код N Дз со знаком.

Абсолютная величина N Д| подается на вхоАбсолютная величина N Д| подается на входы Xi-Ху умножителя-накопителя 1 10, а на входы YI-Y3 последнего одновременно по сигналу У7 подается код числа 7. По сигналу У8 осуществляется синхронизация регистров X и Y умножителя-накопителя 110 и начинается перемножение кодов N Дз и 7 в матрице асинхронного умножителя последнего (длительность этой операции равна интервалу времени 12,фиг. 6). Абсолютная величина кода и его знак по сигна- лу У7 заносятся также в регистр 71. Информация о знаке N Дз поступает также на группу логических элементов 75, 89, 91, 92. Для случая, представленного на фиг. За, разность Дз имеет знак «-{-«, т. е. «1 со знакового выхода сумматора 73 через логи- ческие элементы И 75 и 91 проходит на вход триггера 107, на прямом выходе последнего появляется «1, которая поступает на вход управления накоплением UN умножителя- накопителя 110. По сигналу У10 пропзво- дится обнуление регистра 70. По сигналу У9 осуществляется синхронизация регистра произведения умножителя-накопителя 110, с выхода которого на вторую группу входов сумматора последнего подается находившаяся в этом регистре сумма ( . В этот же момент времени на

произведения умножителя-накопителя 110. Информация о N Дэ и его знаке появляется

соответственно на выходах Ng и 5э умножителя-накопителя 110, по сигналу УМ заносится в регистр 72 и проходит соответственно на выходы .NO и So блока 6 экстраполяции. Далее все операции выполняются аналогично описанному.

Выходной код считывается в моменты дискретизации t (фиг. За) с выходов накапивающего сумматора 8 (фиг. 1).

Таким образом,предлагаемый преобразоатель за счет введения параллельного каала и использования усовершенствованноо алгоритма уравновешивания позволяет овысить динамическую точность аналого- ифрового преобразования.

Формула изобретения

5

0

5

ключен выходом к второму входу блока вычитания, а цифровыми входами - к выходам регистра, информационные входы которого соединены с выходами разрядов модуля и знака результата блока аналого-цифрового преобразования разности, при этом блок синхронизации подключен первым- выходом к синхронизирующему входу блока аналого- цифрового преобразования разности, вторым выходом - к первому входу записи входного регистра накапливающего сумматора, третьим выходом - к первому входу записи выходного регистра накапливающего сумматора, четвертым выходом к синхронизирующему входу блока аналого-цифрового преобразования разности, а выходами с пятого по четырнадцатый - к соответствующим синхронизирующим входам блока экстраполяции, причем пятый выход блока синхронизации соединен с синхронизирующим входом блока анализа состояния процесса и входом записи дополнительного блока цифроаналогового преобразования, подключенного входом обнуления к тринадцатому выходу блока синхронизации и второму входу записи выходного регистра накапливающего сумматора, второй вход записи входного регистра которого соединен с двенадцатым выходом блока синхронизации.

5 входом второго триггера, подключенного прямым выходом к выходу сигнала экстраполяции второго порядка блока анализа состояния процесса, а инверсным выходом - к первому входу второго элемента И, соединенного вторым входом с прямы.м выходом

0 первого триггера, а выходом - с выходом сигнала экстраполяции первого порядка блока анализа состояния процесса.

0

5

0

/V

/L

Лг

,

20

, 0

2

4I«

Гц

ST

i t; «2

wl

ЛЛ1/С 1я ;i2.4di

/«

.

t; t|

.л

а i

(Ри.г.6

:n

| Аналого-цифровой преобразователь | 1973 |

|

SU486470A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР № 915236, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-07-07—Публикация

1986-04-16—Подача