1

Изобретение,относится к измерительной и вычислительной технике и может быть использовано для получения количественной информации о бы- стропротекающих процессах.

Целью изобретения является уменьшение динамической погрешности и рширение частотного диапазона входного сигнала,

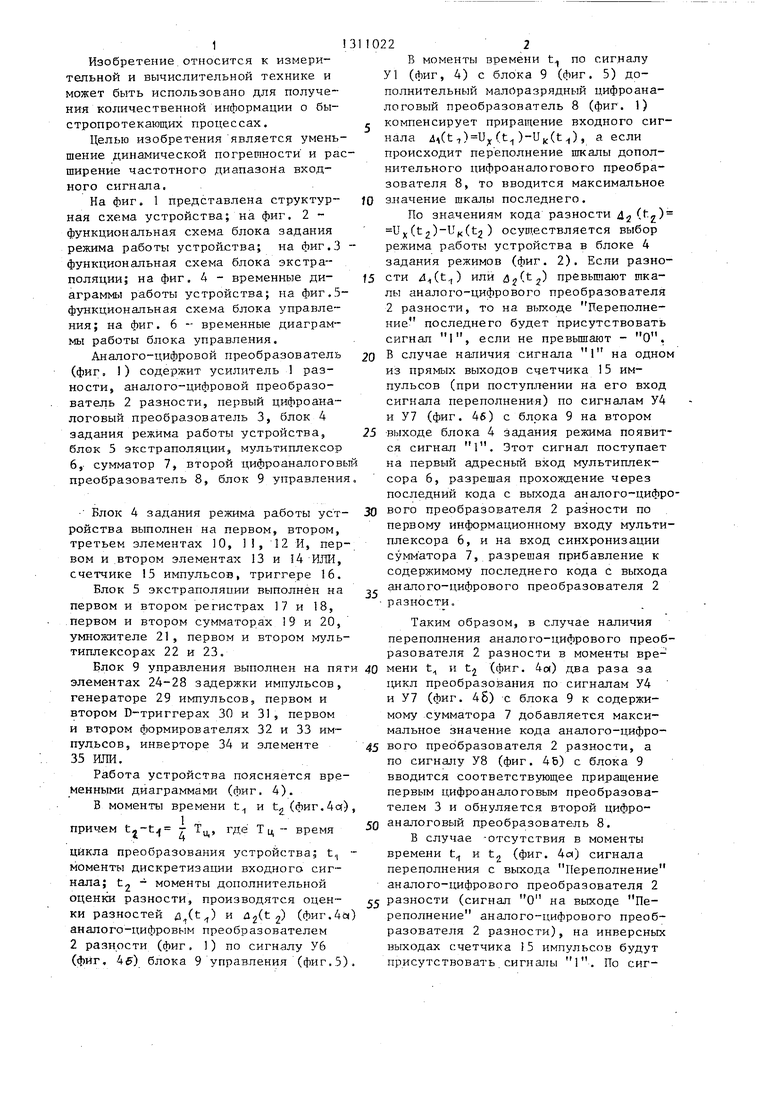

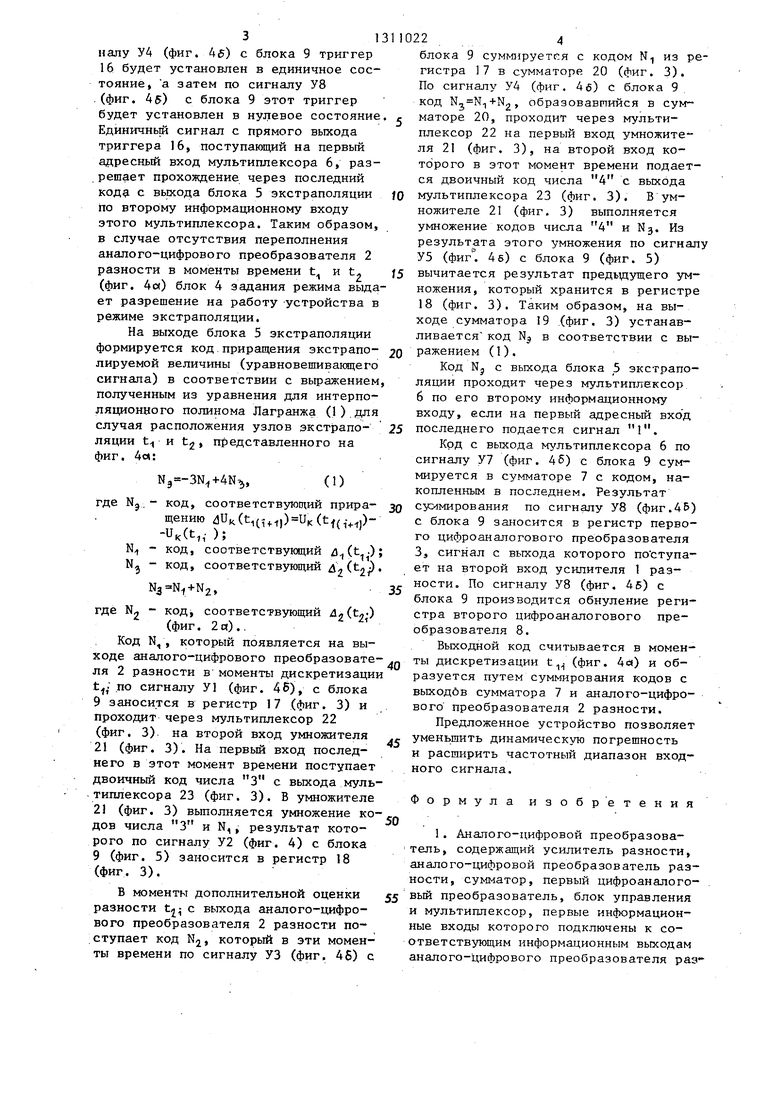

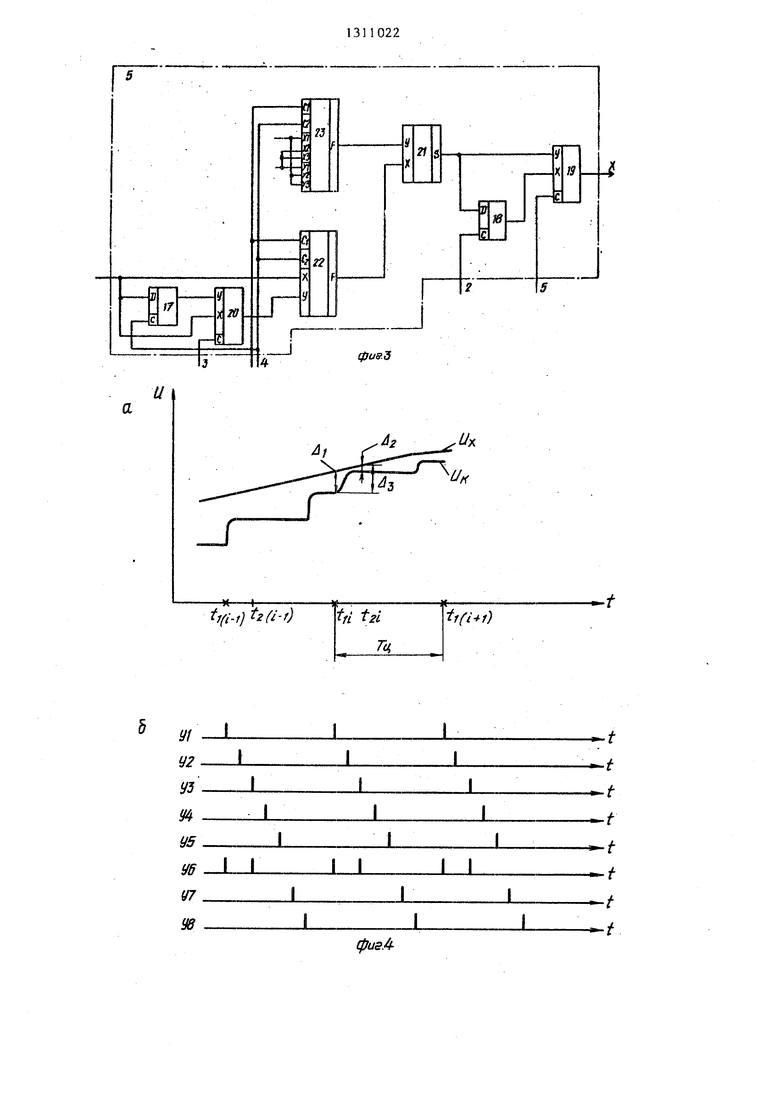

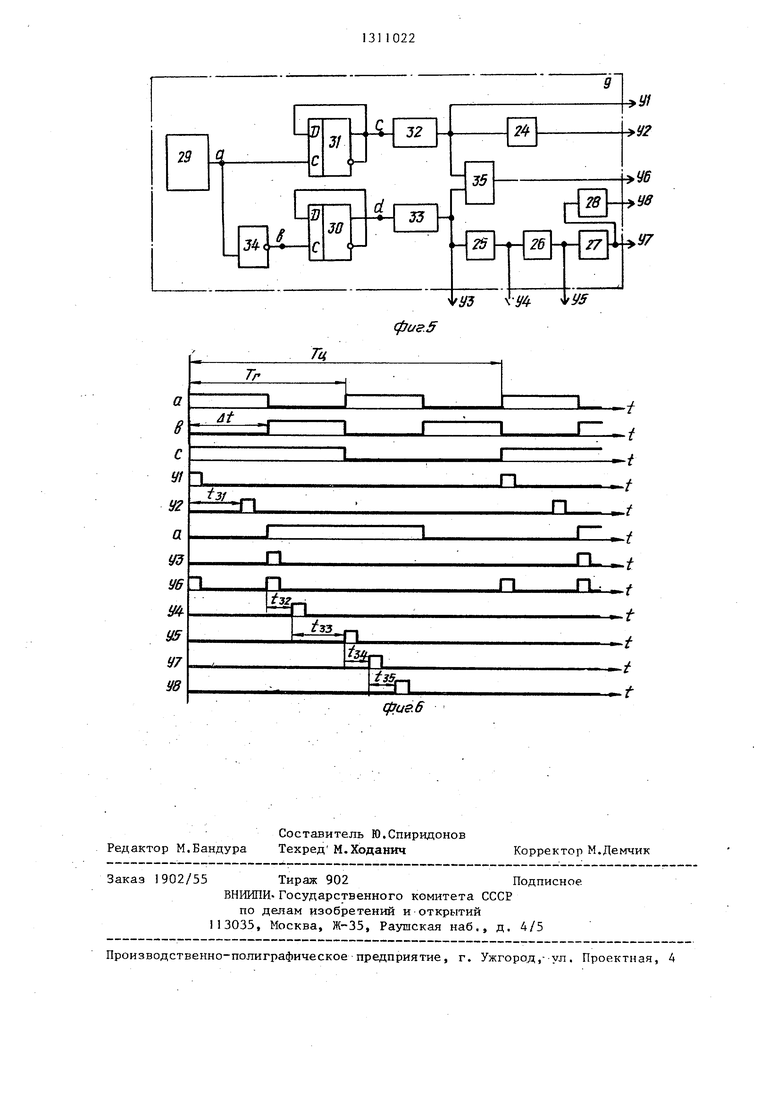

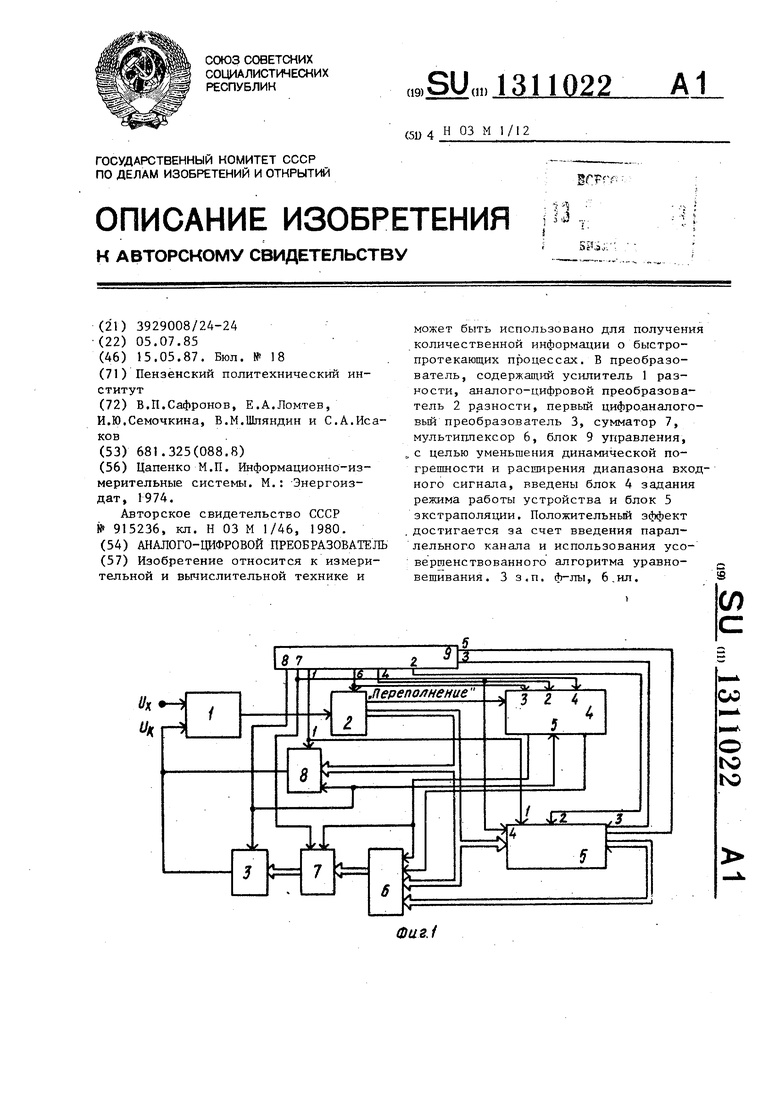

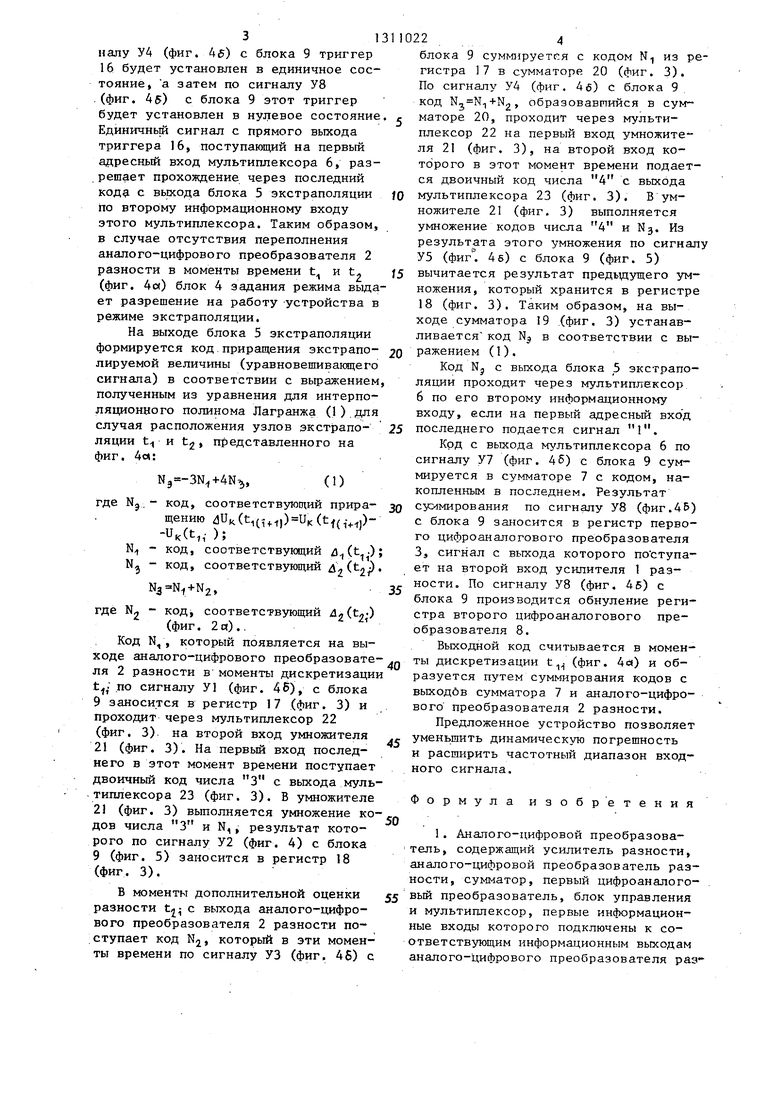

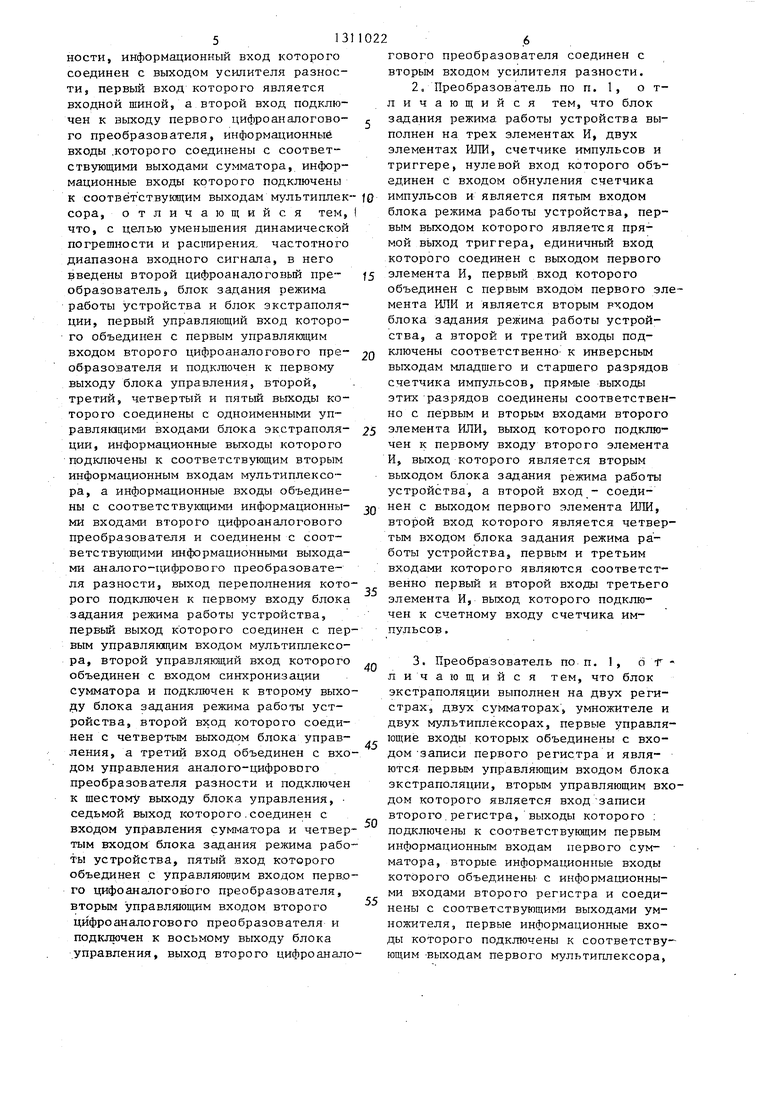

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - функциональная схема блока задания режима работы устройства; на фиг. функциональная схема блока экстраполяции; на фиг, 4 - временные диаграммы работы устройства; на фиг. функциональная схема блока управления; на фиг. 6 - временные диаграммы работы блока управления.

Аналого-цифровой преобразовател (фиг, ) содержит усилитель 1 разности, аналого-цифровой преобразователь 2 разности, первый цифроана логовый преобразователь 3, блок 4 задания режима работы устройства, блок 5 экстраполяции, мультиплексо 6,- сумматор 7, второй цифроаналого преобразователь 8, блок 9 управлен

Блок 4 задания режима работы устройства выполнен на первом, втором, третьем элементах 10, 1, 12 И, первом и .втором элементах 13 и 14 ИЛИ, счетчике 15 импульсов, триггере 16. Блок 5 экстраполяции выполнен на первом и втором регистрах 17 и 18, .первом и втором сумматорах 19 и 20, умножителе 21, первом и втором мультиплексорах 22 и 23,

Блок 9 управления выполнен на пяти 40 мени t и t (фиг. 4о() два раза за

элементах 24-28 задержки импульсов, генераторе 29 импульсов, первом и втором D-триггерах 30 и 31 , первом и втором формирователях 32 и 33 им- пул.ьсов, инверторе 34 и элементе 35 ИЛИ.

Работа устройства поясняется временными диаграммами (фиг. 4).

В моменты времени t и t2(фиг.4a),

- 7 T, где Тц- время

цикла преобразования устройства; t,, - моменты дискретизации входного сигнала; t2 моменты дополнительной оценки разности, производятся оценки разностей 4/t) и (t. (фиг.4а) аналого-цифровым преобразователем 2 разности (фиг. 1) по сигналу У6 (фиг, 45) блока 9 управления (фиг.З).

причем tj-t - Т,

1ЩКЛ преобразования по сигналам У4 и У7 (фиг. 4б) с блока 9 к содержимому сумматора 7 добавляется максимальное значение кода аналого-цифро

45 вого преобразователя 2 разности, а по сигналу У8 (фиг. Аб) с блока 9 вводится соответствующее приращение первым цифроаналоговым преобразователем 3 и обнуляется второй цифро50 аналоговый преобразователь 8.

В случае -отсутствия в моменты времени t: и ty (фиг. 4с() сигнала переполнения с выхода Переполнение аналого-цифрового преобразователя 2

«15 разности (сигнал О на выходе Переполнение аналого-цифрового преоб разователя 2 разности), на инверсны выходах счетчика 15 импульсов будут присутствовать.сигналы 1. По сиг

В моменты времени t по сигналу У1 (фиг. А) с блока 9 (фиг. 5) дополнительный малоразрядный цифроана- логовый преобразователь 8 (фиг. 1) компенсирует приращение входного сигнала 4д(1 т)и, (t )-U.(t), а если происходит пер еполнение шкалы дополнительного цифроаналогового преобразователя 8, то вводится максимальное злачение шкалы последнего.

По значениям кода разности д(t) U(t2)U(t2 ) осуит.ествляется выбор режима работы устройства в блоке 4 задания режимов (фиг. 2). Если разно- сти л(t) или г -г- превьш1ают шкалы аналого-цифрового преобразователя 2 разности, то на выходе Переполнение последнего будет присутствовать

сигнал I, если не превьшгают - О. В случае наличия сигнала 1 на одном из прямых выходов счетчика 15 импульсов (при поступлении на его вход сигнала переполнения) по сигналам У4 и У7 (фиг. 4б) с блока 9 на втором

-выходе блока 4 задания режима появится сигнал l. Этот сигнал поступает на первый адресный вход мультиплексора 6, разрешая прохождение через последний кода с выхода аналого-цифрового преобразователя 2 разности по первому информационному входу мультиплексора 6, и на вход синхронизации сумм атора 7, разрешая прибавление к содержимому последнего кода с выхода аналого-цифрового преобразователя 2 разности.

Таким образом, в случае наличия переполнения аналого-цифрового преобразователя 2 разности в моменты вре

1ЩКЛ преобразования по сигналам У4 и У7 (фиг. 4б) с блока 9 к содержимому сумматора 7 добавляется максимальное значение кода аналого-цифро45 вого преобразователя 2 разности, а по сигналу У8 (фиг. Аб) с блока 9 вводится соответствующее приращение первым цифроаналоговым преобразователем 3 и обнуляется второй цифро50 аналоговый преобразователь 8.

В случае -отсутствия в моменты времени t: и ty (фиг. 4с() сигнала переполнения с выхода Переполнение аналого-цифрового преобразователя 2

«15 разности (сигнал О на выходе Переполнение аналого-цифрового преобразователя 2 разности), на инверсных выходах счетчика 15 импульсов будут присутствовать.сигналы 1. По сиг313

налу У4 (фиг. 45) с блока 9 триггер 16 будет установлен в единичное состояние, а затем по сигналу У8 .(фиг. 45) с блока 9 этот триггер будет установлен в нулевое состояние. Единичньш сигнал с прямого выхода триггера 16, поступающий на первый адресньй вход мультиплексора 6, разрешает прохождение через последний код с вькода блока 5 экстраполяции по второму информационному входу этого мультиплексора. Таким образом, в случае отсутствия переполнения аналого-цифрового преобразователя 2 разности в моменты времени ц и t, (фиг. 4а) блок 4 задания режима вьща- ет разрешение на работу устройства в режиме экстраполяции.

На выходе блока 5 экстраполяции формируется код.приращения экстраполируемой величины (уравновеншвакщего сигнала) в соответствии с выражением, полученным из уравнения для интерполяционного полинома Лагранжа (1).для случая расположения узлов экстраполяции t и tg, представленного на фиг. 4«:

, (1)

где NJ , - код, соответствующий приращению 4Uk(t,(.,)U,(tf(V-r))-ик(Ц,- );

N - код, соответствующий 4-) (t-) 5 N, - код, соответствующий ).

N3 N|+N2,

где N- код, соответствующий (2

(фиг. 2 я) ..

Код N,, который появляется на выходе аналого-цифрового преобразователя 2 разности в моменты дискретизации по сигналу У1 (фиг. 46), с блока 9 заносится в регистр 17 (фиг. 3) и проходит через мультиплексор 22 (фиг. 3) на второй вход умножителя 21 (фиг. 3). На первый вход последнего в этот момент времени поступает двоичный код числа 3 с выхода мультиплексора 23 (фиг. 3). В умножителе 2 (фиг. 3) выполняется умножение кодов числа 3 и N,, результат которого по сигналу У2 (фиг. 4) с блока 9 (фиг. 5) заносится в регистр 18 (фиг. 3).

В моменты дополнительной оценки разности tj с выхода аналого-цифрового преобразователя 2 разности поступает код N2, который в эти моменты времени по сигналу УЗ (фиг. 45) с

224

блока 9 суммируется с кодом N из регистра 17 в сумматоре 20 (фиг. 3) По сигналу У4 (фиг. 4б) с блока 9 код , образовавшийся в сум- маторе 20, проходит через мультиплексор 22 на первый вход умножителя 21 (фиг. 3), на второй вход которого в этот момент времени подается двоичный код числа 4 с выхода

мультиплексора 23 (фиг. 3). В умножителе 21 (фиг. 3) выполняется умножение кодов числа 4 и N3. Из результата этого умножения по сигналу У5 (фиг. 4б) с блока 9 (фиг. 5)

вычитается результат предьщущего умножения, который хранится в регистре 18 (фиг. 3). Таким образом, на выходе сумматора 19 (фиг. 3) устанавливается код N в соответствии с выражением (I).

Код NJ с выхода блока 5 экстраполяции проходит через мультиплексор 6 по его второму информационному входу, если на первый адресньй вход

последнего подается сигнал 1.

Код с выхода мультиплексора 6 по сигналу У7 (фиг. 46) с блока 9 суммируется в сумматоре 7 с кодом, накопленным в последнем. Результат

су 1мирования по сигналу У8 (фиг.4Б) с блока 9 заносится в регистр первого цифроаналогового преобразователя 3, сигнал с выхода которого по ступа- ет на второй вход усилителя 1 разности. По сигналу У8 (фиг. 46) с блока 9 производится обнуление регистра второго цифроаналогового преобразователя 8.

Выходной код считывается в моменты дискретизации t (фиг. 4с«) и образуется путем суммирования кодов с выходов сумматора 7 и аналого-цифрового преобразователя 2 разности.

Предложенное устройство позволяет

уменьшить динамическую погрешность и расширить частотный диапазон входного сигнала.

Формула изобр е тения

50

1. Аналого-цифровой преобразова- тель, содержащий усилитель разности, аналого-цифровой преобразователь разности, сумматор, первый цифроаналого- 55 вый преобразователь, блок управления и мультиплексор, первые информационные входы которого подключены к соответствующим информационным выходам аналого-цифрового преобразователя раз

51311

ости, информационный вход которого оединен с выходом усилителя разноси, первый вход которого является ходной шиной, а второй вход подклюен к выходу первого цифроаналогового преобразователя, информационные входы .которого соединены с соответствующими выходами сумматора, информационные входы которого подключенЕ 1 к соотвётствуклдим выходам мультиплек сора, отличающийся тем, I что, с целью уменьшения динамической погрешности и рас1чирения, частотного иапазона входного сигнала, в него введены второй цифроаналоговый преобразователь, блок задания режима работы устройства и блок экстраполяции, первый управляющий вход которо- го объединен с первым управляющим входом второго цифроаналогового преобразователя и подключен к первому выходу блока управления, второй, третий, четвертый и пятый выходы которого соединены с одноименными уп- равлянзцими входами блока экстраполяции, информационные выходы которого подключены к соответствующим вторым информационным входам мультиплексора, а информационные входы объединены с соответствующими информационными входами второго цифроаналогового преобразователя и соединены с соот- ветств ующими информационными выходами аналого-1Ц1фрового преобразователя разности, выход переполнения которого подключен к первому входу блока задания режима работы устройства, первый выход которого соединен с первым управляющим входом мультиплексора, второй управляющий вход которого объединен с входом синхронизации сумматора и подключен к второму выходу блока задания режима работы устройства, второй вход которого соединен с четвертым выходом блока управления, а третий вход объединен с входом управления аналого-цифрового преобразователя разности и подключен к шестому выходу блока управления, седьмой выход которого.соединен с входом управления сумматора и четвертым входом блока задания режима рабо- Т Ы устройства, пятый вход которого объединен с управляющим входом перв.о- го цифоаналогового преобразователя, вторьм управляющим входом второго цифроаналогового преобразователя и подкгаочен к восьмому выходу блока управления, выход второго цифроангшо6

гового преобразователя соединен с вторым входом усилителя разности.

2, Преобразователь по п. 1, отличающийся тем, что блок

задания режима работы устройства выполнен на трех элементах И, двух элементах ИЛИ, счетчике импульсов и триггере, нулевой вход которого объединен с входом обнуления счетчика

импульсов и является пятым входом блока режима работы устройства, первым выходом которого является прямой вькод триггера, единичный вход которого соединен с выходом первого

элемента И, первый вход которого

объединен с первым входом первого элемента ИЛИ и является вторым входом блока задания режима работы устройства, а второй и третий входы подключены соответственно- к инверсным выходам младшего и старшего разрядов счетчика импульсов, прямые вмкоды этих разрядов соединены соответственно с первым и вторым входами второго

элемента ИЛИ, выход которого подключен к первому входу второго элемента И, выход которого является вторым выходом блока задания режима работы устройства, а второй вход - соединен с вьглодом первого элемента ЮШ, второй вход которого является четвертым входом блока задания режима работы устройства, первым и третьим входами которого являются соответственно первый и второй входы третьего элемента И, выход которого подключен к счетному входу счетчика импульсов .

3. Преобразователь по п. , d т - личающийся тем, что блок экстраполяции выполнен на двух регистрах, двух сумматорах, умножителе и двух мультиплексорах, первые управляющие входы которых объединены с входом записи первого регистра и являются первым управляющим входом блока экстраполяции, вторым управляющим входом которого является вход-записи второго.регистра, выходы которого : подключены к соответствукнцим первым информационным входам первого сумматора, вторые информационные входы которого объединены- с информационными входами второго регистра и соединены с соответствующими выходами умножителя, первые информационные входы которого подключены к соответствующим -выходам первого мультиплексора.

713

а вторые информационные входы подключены к соответствующим выходам второго мультиплексора, второй управляющий вход которого объединен с

вторым управляющим входом первого .. мультиплексора и является четвертым уп|)авляющим входом блока экстраполяции, а вход младшего разряда первой информационной группы входов объединен с входами старших разрядов второй информационной группы входов и подключен к пшне логического О, входы старших разрядов первой информационной группы входов и вход младшего разряда второй информационной группы входов второго мультиплексора объединены и подключены к 1иине логической 1, первые информационные входы первого мультиплексора и второго сумматора объединены с соответствующими информационными входами первого регистра и являются соответствующими информационными входами блока экстраполяции, пятым управляющим входом которого является вход синхронизации первого сумматора, выходы которого являются информационными выходами блока экстраполяции, третьи управляющим входом которого является вход синхронизации второго сумматора, выход которого подключен к вторым информационным входам первого мультиплексора, а вторые информационные входы соедьшены с соответствующими выходами первого регистра.

28

4. Преобразователь по п. 1, отличающийся тем, что блок управления выполнен на пяти элементах задержки импульсов, генераторе

импульсов, двух D-тригГерах, двух формирователях импульсов, инверторе и элементе ИЛИ, выход которого является шестым выходом блока управления, а первый вход объединен с входом первого элемента задержки импульсов, подключен к выходу первого формирователя импульсов и является первым выходом блока управления, вторым выходом которого является выход

первого элемента задержки импульсов а третьим выходом - является выход второго формирователя импульсов, который подключен к второму входу элемента ИЛИ и входу второго элемента задержки импульсов, вход второго формирователя импульсов соединен с прямым выходом первого D-триггера, инверсный выход которого подключен: к его В- входу, а С-вход соединен с

выходом инвертора, вход которого

объединен с С-входом второго D-триггера и подключен к выходу генератора импульсов, D-вход второго D-триггера соединен с его инверсным выходом, а

прямой выход подключен к входу первого формирователя импульсов, второй, третий, четвертый и пятьй эле- менты задержки импульсов соединены последовательно,а их выходы являются соответственно четвертым, пятым,седьмьм

и восьмым выходами блока управления.

фаг. 2

75

IS

-4

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1986 |

|

SU1408531A1 |

| Система управления вибростендом | 1984 |

|

SU1275396A1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| Устройство для определения автокорреляционной функции | 1984 |

|

SU1363254A1 |

| Экстраполятор видеосигнала изображения | 1989 |

|

SU1718246A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Устройство для определения корреляционной функции | 1984 |

|

SU1363255A1 |

| Устройство для регистрации информации | 1985 |

|

SU1457163A1 |

Изобретение относится к измерительной и вычислительной технике и может быть использовано для получения количественной информации о быстро- протекающих процессах. В преобразователь, содержащий усилитель 1 разности, аналого-цифровой преобразователь 2 разности, первый цифроаналого- вый преобразователь 3, сумматор 7, мультиплексор 6, блок 9 угфавления, ,с целью уменьшения динамической погрешности и расширения диапазона входного сигнала, введены блок 4 задания режима работы устройства и блок 5 экстраполяции. Положительный зффект достигается за счет введения параллельного канала и использования усовершенствованного алгоритма уравновешивания. 3 з.п. ф-лы, 6.ил. 9 . i

€

13

20

e

13

a

и

фие.З

1

fr{i-f) fz(i-f)

til tzL

У1 - У2

-L

L

I I

У7 У8

)

-f

-f t

I I

фигАtt

фаг.5

| Цапенко М.П | |||

| Информационно-измерительные системы | |||

| М.: Энергоиз- дат, 1974 | |||

| Авторское свидетельство СССР № 915236, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-05-15—Публикация

1985-07-05—Подача