Изобретение относится к вычислительной технике и может быть применено в специализированных вычислителях устройств цифровой обработки сигналов .

Цель изобретения - расширение класса решаемых задач за счет возможности вычисления совокупности тригонометрических функций (arcsinx, arc- cos X, arctg X, arcctg x, arcsin XI /X2, arccosXl/X2, arctgXl/X2, arc- ctg XI /X2) и выполнения операции деле- ния (XI /Х2, 1/Х2).

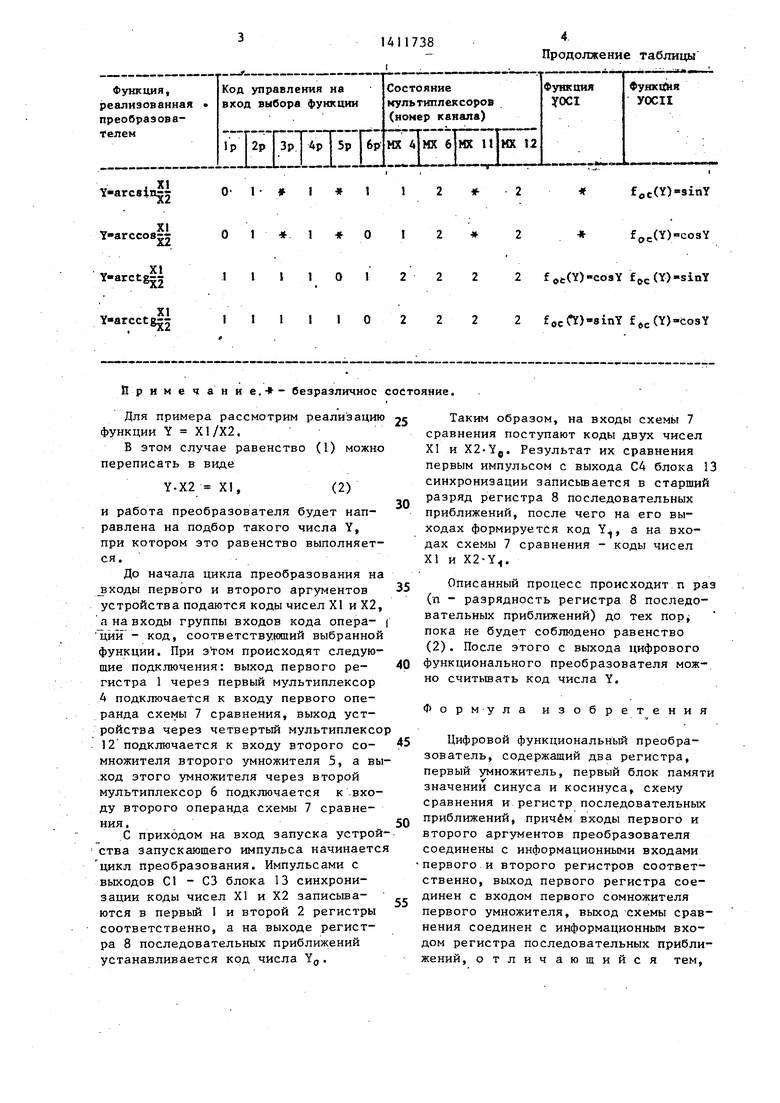

На чертеже представлена функциональная схема преобразователя.

Преобразователь содержит первый 1 и второй 2 регистры, первый умножитель 3, первый мультиплексор 4, второй умножитель 5, второй,мультиплексор 6, схему 7 сравнения, регистр 8 последовательных приближений, первый блок 9 памяти значений синуса и косинуса, второй блок Ю памяти значений синуса и косинуса, третий мультиплексор 11, четвертый мультиплексор 12, блок 13 синхронизации.

Преобразователеработает следующи образом.

Перед началом про.цесса преобра- зования на первый и второй входы преобразователя поступают в виде двоичных кодов два числа XI и Х2, а на группу входов кода операции - код требуемой функции.

Алгоритм работы преобразователя основан на том, что с помощью регистра 8 последовательных приближений на выходе преобразователя устанавливается такое число Y, при котором выполняется равенство

.Л) ,г, (Y), (1)

oct

-Ос и

где XI

Х2

0

-OCI

(1) 5

ос Г,(Y)

код первого числа, поступающего на вход преобразователя;

код второго числа, поступающего на вход преобразователя;

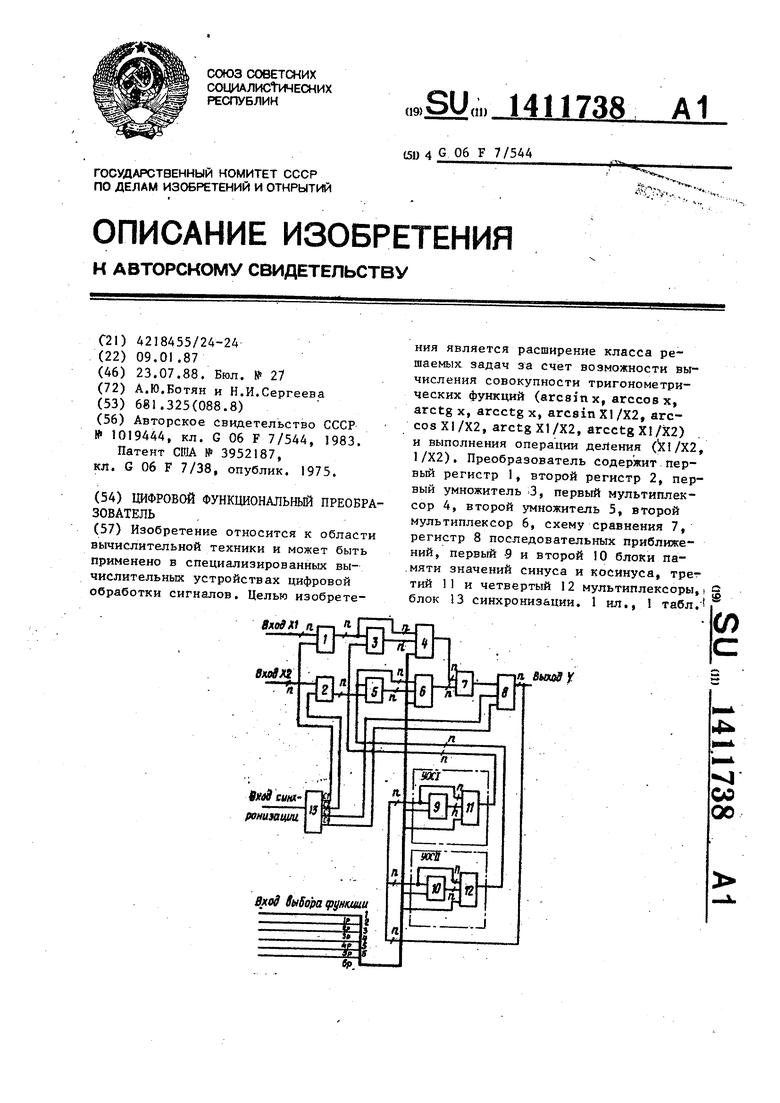

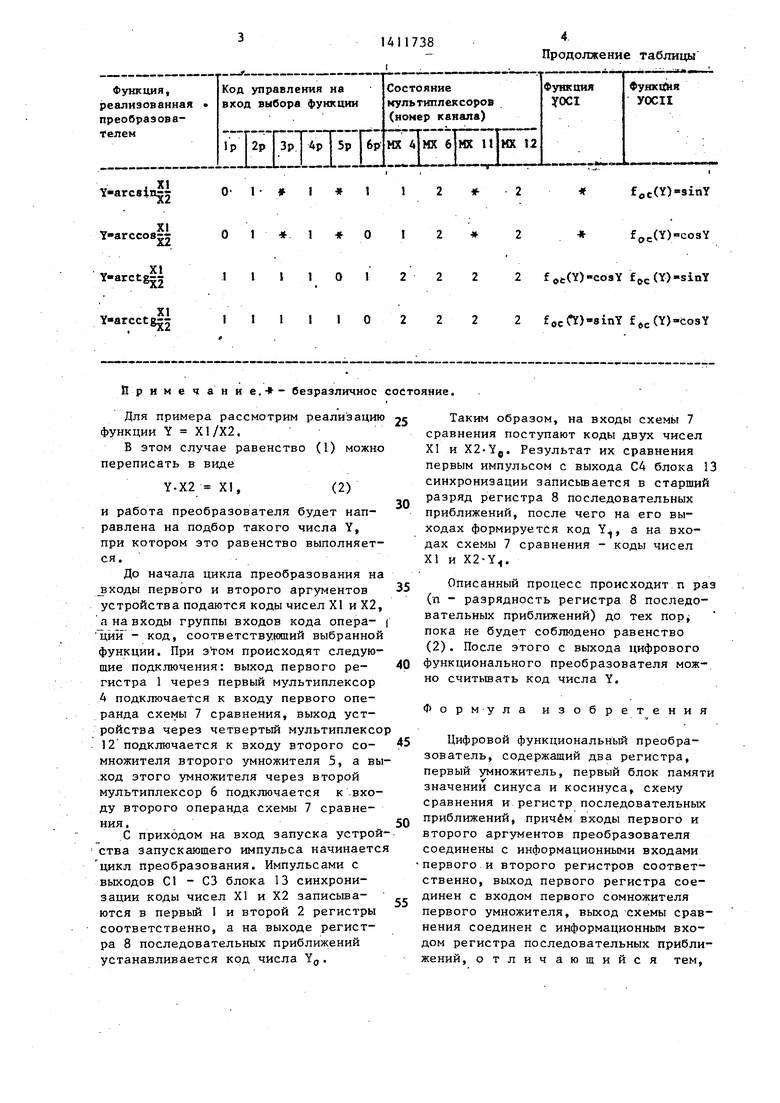

функция, реализованная первым узлом обратной связи (УОС1), содержащим первый блок 9, памяти и третий мультиплексор 11; функция, реализованная вторым узлом обратной связи (УОСИ), содержащим второй блок 10 памяти и. четвертый мультиплексор 12. . В соответствии с управляющим кодом, поступающим на входы группы вхр- дов кода операции, на выходах УОС1 и УОСИ вырабатываются коды одной из .перечисленных ниже функций выходного числа Y:

focW Y; sinY;

(Y) COSY .

Изменяя код, поступающий на входы группы входов кода операции, можно реализовать различные алгебраические 5 и тригонометрические функции входных величин XI и Х2, представленные в таблице управляющих сигналов на входах элементов и узлов преобразовате-. ля.

0

5

0

Для примера рассмотрим реализацию 25 функции Y XI/Х2,

В этом случае равенство (I) можно переписать в виде

Y.X2 XI,

(2)

и работа преобразователя будет направлена на подбор такого числа Y, при котором это равенство выполняется.

До начала цикла преобразования на

Jвxoды первого и второго аргументов устройства подаются коды чисел XI и Х2, а на входы группы входов кода опера-

код, соответствующий выбранной функции. При происходят следующие подключения: выход первого регистра 1 через первый мультиплексор 4 подключается к входу первого операнда схемы 7 сравнения, выход устройства через четвертый мультиплексо 12 подключается к входу второго со- множителя второго умножителя 5, а вы .ход этого умножителя через второй мультиплексор 6 подключается к .входу второго операнда схемы 7 сравнения.

С приходом на вход запуска устройства запускающего импульса начинаетс

цикл преобразования. Импульсами с выходов С1 - СЗ блока 13 синхронизации коды чисел XI и Х2 записываются в первый I и второй 2 регистры соответственно, а на выходе регистра 8 последовательных приближений устанавливается код числа Y.

5

0

5

0

4 0

5

Таким образом, на входы схемы 7 сравнения поступают коды двух чисел XI и X2 Yp. Результат их сравнения первым импульсом с выхода С4 блока 13 синхронизации записьшается в старший разряд регистра 8 последовательных приближений, после чего на его выходах формируется код Y, а на входах схемы 7 сравнения - коды чисел XI и X2-Y.

Описанный процесс происходит п раз (п - разрядность регистра 8 последовательных приближений) до тех пор пока не будет соблюдено равенство (2). После этого с выхода цифрового функционального преобразователя можно считьтать код числа Y.

Фор м у ла изобретения

Цифровой функциональный преобразователь, содержащий два регистра, первый умножитель, первый блок памяти значении синуса и косинуса, схему сравнения и регистр последовательных приближений, причём входы первого и второго аргументов преобразователя соединены с информационными входами первого и второго регистров соответственно, выход первого регистра соединен с входом первого сомножителя первого умножителя, выход схемы сравнения соединен с информационным входом регистра последовательных приближений, отличающийся тем.

что, с целью расширения класса решаемых задач за счет возможности вычисления совокупности тригонометрических функций и выполнения операции деления, в него дополнительно введены второй умножитель, второй блок памяти значений синуса и косинуса, четыре мультиплексора и блок синхронизации, причем выход второго регистра соединен с входом первого сомножителя второго ут ножителя, выходы первого и второго умножителей соединены с вторыми информационными входами первого и второго мультиплексоров соот- ветственно, первый информационный вход первого мультиплексора соединен с выходом первого регистра, первый информационный вход второго мультиплексора объединен с входом -второго сомножителя второго умножителя, входы вторых сомножителей первого и вто- 1рого умножителей соединены с выходами I третьего и четвертого мультиплексо- i.pOB соответственно, выходы первого и второго мультиплексоров соединены с iпервым и вторым входами соответствен- Но схемы сравнения, выход регистра Последовательных приближений соединен :С адресными входами первого и второго Iблоков- памяти- значений синуса и ко- Iсинуса и с первыми информационными входами третьего и четвертого мульти

0

5

0

плексоров, вторые информационные входы третьего и четвертого мультиплексоров соединены с выходами соответственно первого и второго блоков памяти значений синуса и косинуса, выход регистра последовательных приближений соединен с выходом результата преобразователя, вход запуска которого соединен с одноименным входом блока синхронизации, первый и второй выходы которого соединены с входами начальной записи первого и второго регистров соответственно, третий и четвертый выходы блока синхронизации соединены с входами начальной записи и синхронизации соответственно регистра последовательных приближений, первый и второй входы группы входов кода операции преобразователя соединены с управляюшими входами первого и второго мультиплексоров соответственно, третий и четвертый входы группы входов кода операции преобразователя соединены с управляющими входами третьего и четвертого мультиплексоров соответственно, пятый и шестой входы группы вводов кода операции преобразователя соединены с управляющими входами выбора функции соответственно первого и второго блоков памяти значений синуса и косинуса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дифференцирующее устройство | 1988 |

|

SU1674120A1 |

| Устройство для преобразования координат | 1989 |

|

SU1681313A1 |

| Устройство для преобразования координат | 1990 |

|

SU1800455A1 |

| Цифровой преобразователь координат | 1979 |

|

SU842801A1 |

| Устройство для моделирования синусно-косинусного трансформаторного датчика угла | 1990 |

|

SU1778766A1 |

| Вычислительное устройство | 1990 |

|

SU1742814A1 |

| Цифровой функциональный генератор | 1985 |

|

SU1285452A1 |

| Цифровой генератор функций | 1989 |

|

SU1663607A1 |

| Устройство для вычисления функций | 1985 |

|

SU1280391A1 |

| Синусно-косинусный преобразователь | 1986 |

|

SU1330628A1 |

Изобретение относится к области вычислительной техники и может быть применено в специализированных вычислительных устройствах цифровой обработки сигналов. Целью изобрете8яо9Х1 а. BMdXi вХдЗсинХ ронизацщ кия является расширение класса решаемых задач за счет возможности вычисления совокупности тригонометрических функций (arcsinx, arccosx, arctg X, arcctg x, arcsin XI /X2, arc- cos XI/X2, arctgXl/X2, arcctg X1/X2) и выполнения операции деления (lXl/X2, 1/Х2). Преобразователь содержит первый регистр 1, второй регистр 2, первый умножитель 3, первый мультиплексор 4, второй умножитель 5, второй мультиплексор 6, схему сравнения 7, регистр 8 последовательных приближений, первый -9 и второй 10 блоки памяти значений синуса и косинуса, трег тий II и четвертый 12 мультиплексоры, блок 13 синхронизации. 1 ил., 1 табл. Q & (Л I-1Л Вьоч Y 00 СХ)

| Функциональный преобразователь | 1982 |

|

SU1019444A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент СЮА № 3952187, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

Авторы

Даты

1988-07-23—Публикация

1987-01-09—Подача