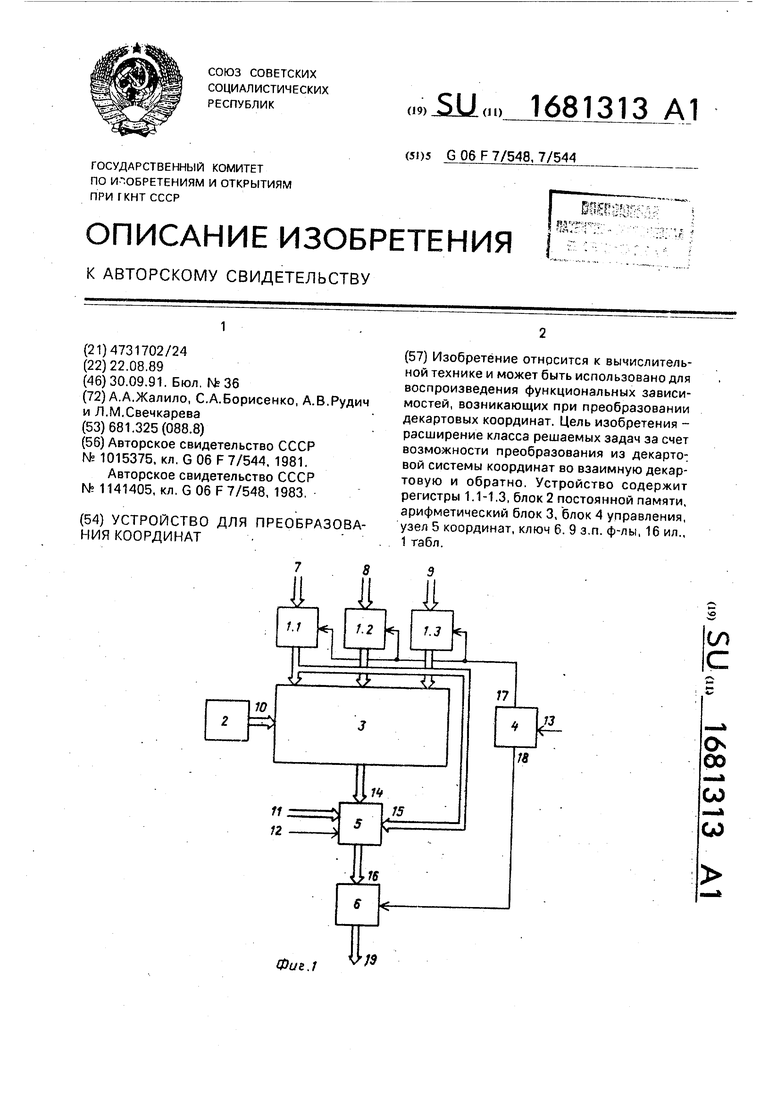

t1lt12t13 t2U22t23

(5) 25

(8)

узуз

t31t32t33 ,t32 - pl--t31-| T...Известно, что

где строки матрицы Т представляют собой

направляющие косинусы осей ox, oy, oz за-t /-ft112+t9i2)

данной системы координат oxyz соответст-30

венно относительно взаимной системыПодставляя в третье уравнение системы

координат oxyz, а столбцы матрицы Т пред- уравнений (2) координаты второй и третьей

ставляют собои направляющие косинусы опорных получаем новую систему из

осей ox, oy.oz взаимной системы координат двух уравнений

oxyz соответственно относительно задан-35

НОЙ OXyZ.0 tnCx9-Xl)+t94fV5-Vll-HWZ9-Z1

Во взаимной системе oxyz выраженияU T13IX2 (22 zi)

(5) 25

(8)

узуз

t32 - pl--t31-|

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования координат | 1990 |

|

SU1800455A1 |

| Устройство для вычисления координат | 1989 |

|

SU1635178A1 |

| Преобразователь координат | 1988 |

|

SU1645951A2 |

| Дифференцирующее устройство | 1988 |

|

SU1674120A1 |

| Преобразователь координат | 1990 |

|

SU1742816A2 |

| Цифровой измеритель показателей качества электрической энергии трехфазной сети | 1988 |

|

SU1633368A1 |

| Вычислительное устройство | 1989 |

|

SU1689947A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Вычислительное устройство | 1989 |

|

SU1691837A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1434427A1 |

для координат трех опорных точек имеют0 t13(x3-xi)+t23(y2-yi)+t33(z3-z1).(9)

Si- II xi, yi, z-1 II1 51-0, , решая ее относительно t13 и t23 имеем

Х2 II Х2, У2, Z2 II , , ,

I I J

-гТ12- (У2 -У1 )(а -21 ) (УЗ -У1 )(г2 Z1 |

ХЗ II ХЗ, УЗ, Z3 II , ХЗ -- (П2 +4g(x2 -xi )(y3-yi)-(x3-xi)(y2-yl)

+П32-Г232)(10), (11)

уз- ± . 2з - 0:(6)|,Х2.Х1|, пзЩи - zi ||, , Oil

где П2Г13 и Г23 - расстояния между первой ихз . Х1-1123| 3 . tw« Oj|(12)

второй, первой и третьей, второй и третьей50 точками соответственно .Обозначая

(x2-X1)2+(y2-yi)-+(z2-Zl)А||Х2-Х1 у2-у1|((22 - 21

(a-.1y+(a--yiy+(a-.,y V3-y,ll ,-Ез-21|| „3)

-.получаем

Г23 V ( ХЗ - Х2 / + ( уз -У2Г +(Z3 - Z2 J,

Направляющие косинусы оси бх, зада-,.t13

ваемой первой и второй опорными точками,JJ t23

Р -Ь

35

Р -Ь

35

еР Ф

1

1)7 det Ф Ai(y2-yiXz3-ziHy3-yiXz2-zi)

А,

AZ

iXZ2-Z 1)-{X2-X 1XZ3-Z1)

det Ф(х2-х1Хуз-у1Нхз-х1Ху2-у1),

(15)

(16)

(17) (18)

тогда

tl32W llt13t23ll|H t332 -Ф (19)

FzjH После преобразований получаем

t33 ±V(1 4-Рт Р)1 или

(i +tf ф-т -v)

(20)

В настоящем алгоритме координата уз третьей опорной точки во взаимной системе координат oxyz (6) успешно выбирается положительной, что одновременно определяет направление оси оу в пространстве. Направляющие косинусы tis, t23 и тзз оси oz взаимной системы координат имеют знаковую неопределенность, характеризующую неоднозначность ориентации оси oz в про- .странстве. Для формирования правой тройки векторов системы oxyz и устранения указанной неоднозначности в алгоритме используется известное свойство матрицы направляющих косинусов

,

где det T t1lt22t33+t21t32t31 + tl2t23t31- - t13t22t31-t1lt32t23-t21t12t33-(21)

Знак элемента 1зз условно выбирается положительным и определяются значения элементов tta и t23. По формуле (21) вычис- 4 лйется детерминант матрицы Т, с помощью которого производится операция коррекции знаков направляющих косинусов tis, t23

И t33

К-ьТиМ.

t13 t23 t33

det Т

(22)

в результате применения которой в предложенном алгоритме исключается возможность ошибочного знакоопределения элементов третьего столбца матрицы Т, задающих ориентацию оси of взаимной системы координат в трехмерном пространстве измерений,

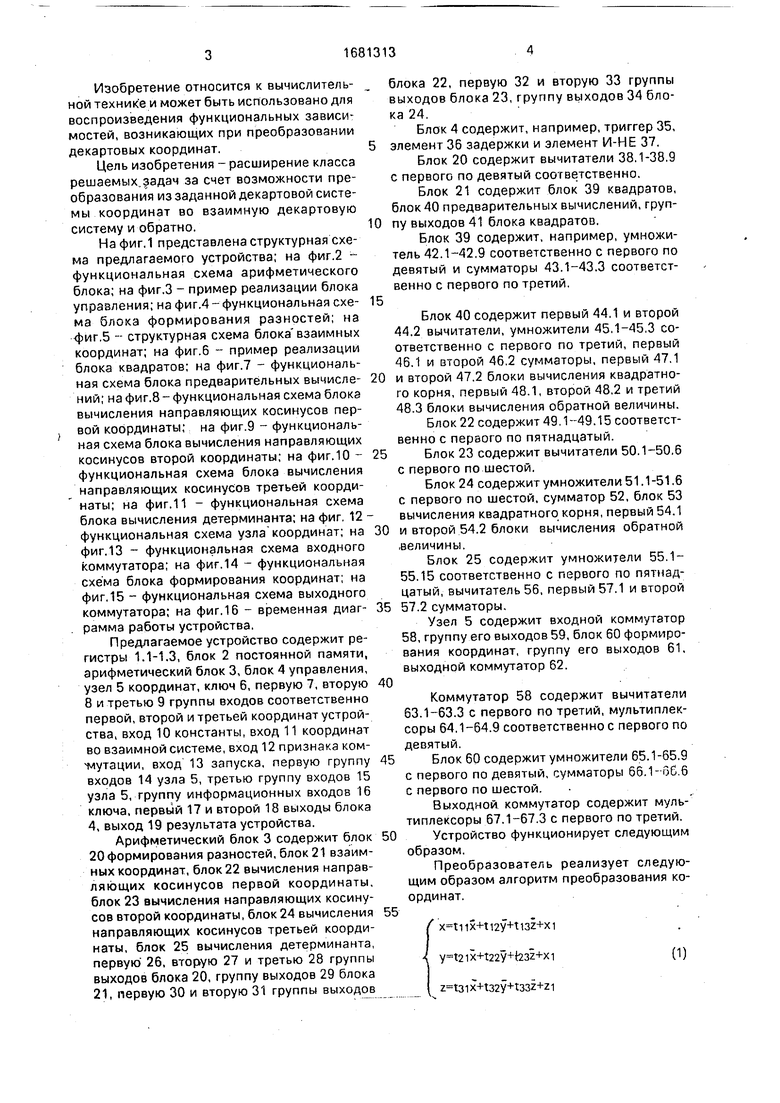

Пример. Пусть координаты точки во взаимной системе координат соответственно равны

x 570;y 650;z 10.

Здесь и далее при рассмотрении работы устройства двоичный эквивалент чисел не используется, так как при этом теряется на- 0 глядность. Пространственные координаты опорных точек, определяющих взаимную систему, в заданной системе координат равны соответственно

5 x 2336y 1396z 4807 x 2215y 4347z 4094

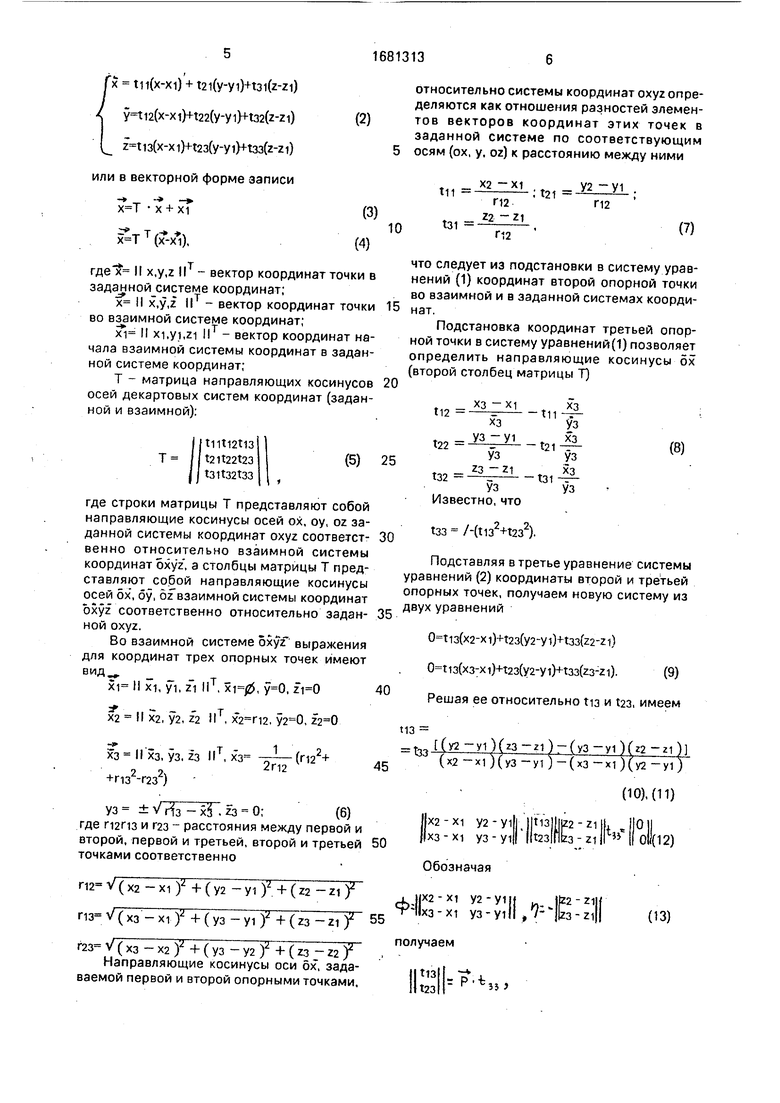

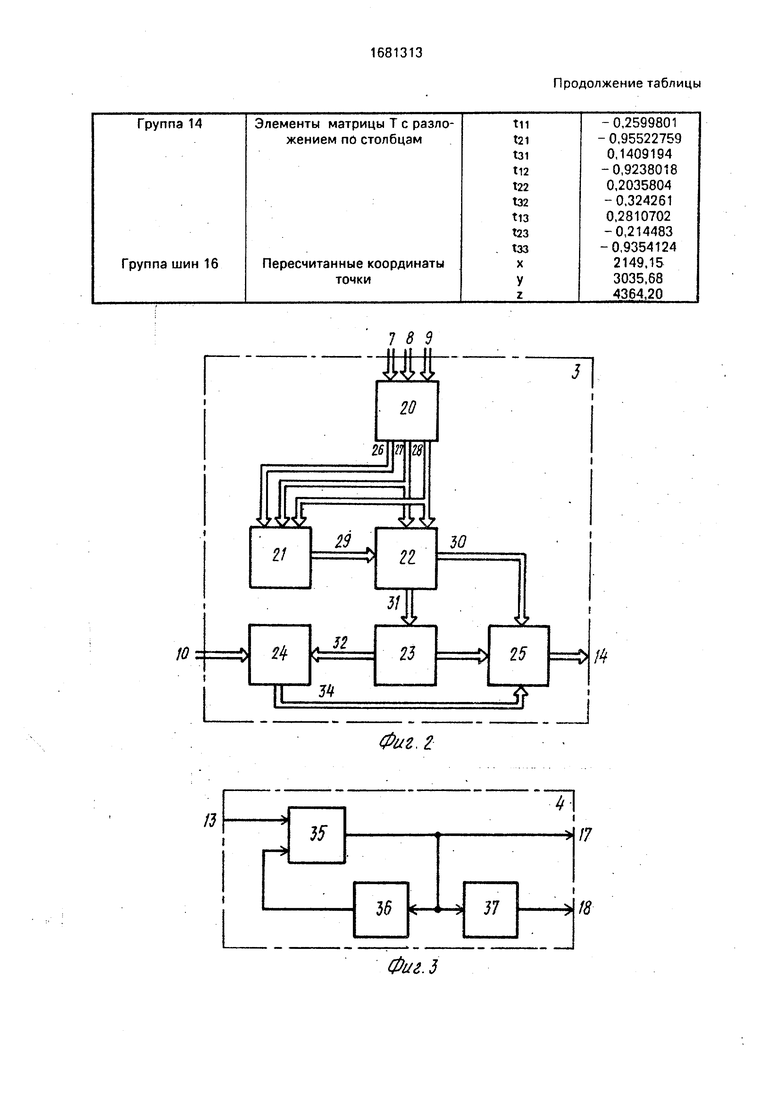

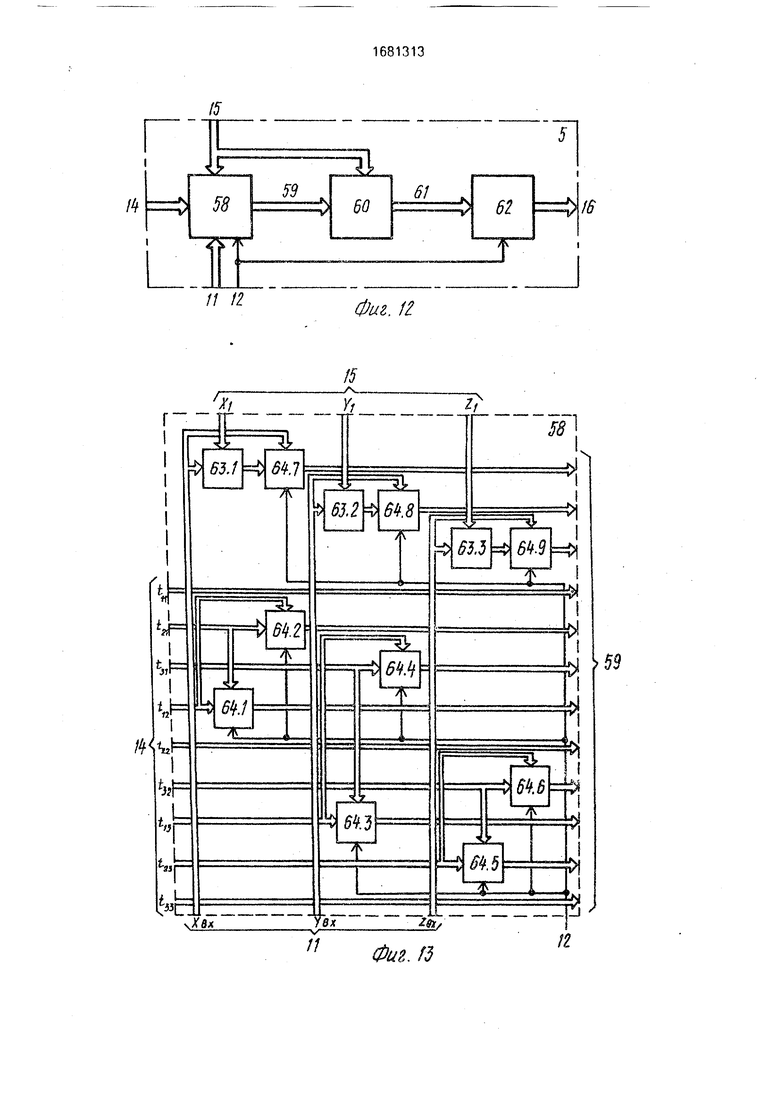

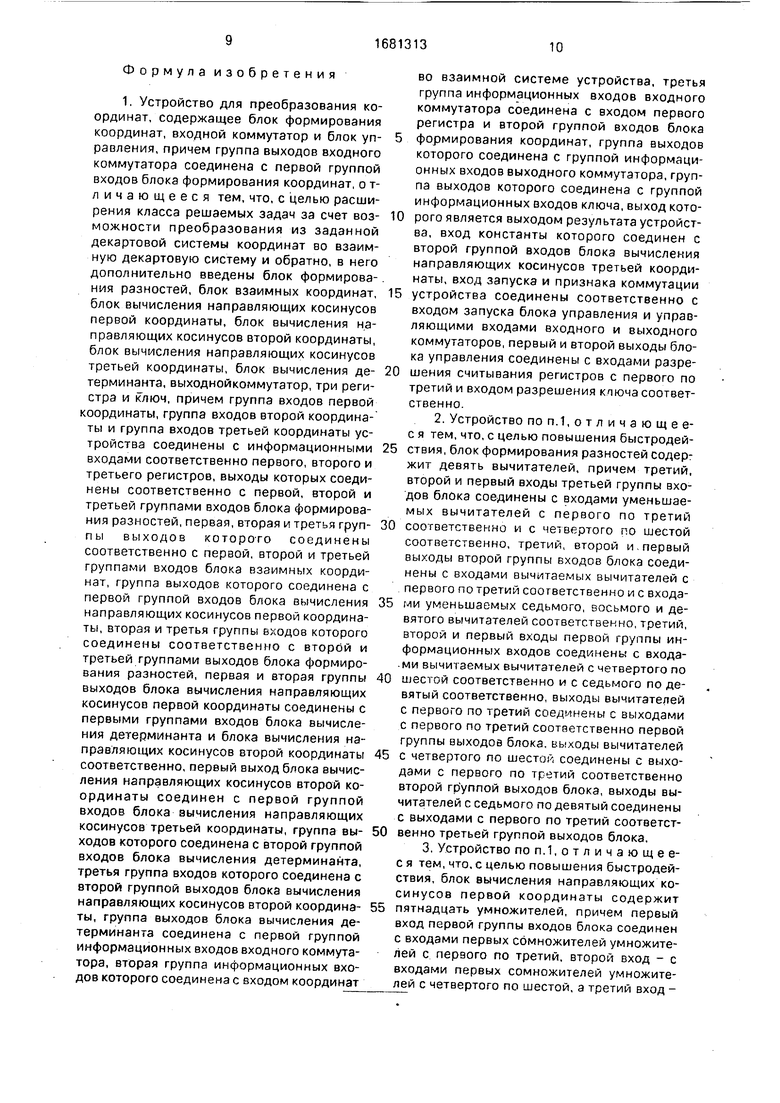

Работа устройства начинается с того, 0 что по входам 7, 8 и 9 прступают значения xi, yi и zi (,3) соответственно, по входам 11 - значения величин х,у,Ј, а по входу 12 - сигнал внешнего управления, который для рассматриваемого случая преобразования 5 декартовых координат точки из взаимной системы в заданную систему координат подключает на весь цикл вычислений выходы всех мультиплексоров 64.1-64.9, 67.1- 67.3 в узле 5 координат к своему первому 0 входу.

Основная работа устройства осуществляется с помощью блока уравнения 4 и начинается подачей сигнала на вход 13

5 (см.фиг.З) внешнего запуска. При этом переводится в единичное состояние триггер 35 и тем самым разрешается чтение информации из регистров. Кроме того, выход триггера 35 соединен с входом элемента 36

0 задержки и входом элемента И-НЕ 37, где происходит инвертирование сигнала. В результате отрицательный перепад напряжения на выходе элемента И-НЕ 37 закрывает ключ 6 (см. фиг.1). С выхода элемента 36

5 задержки задержанный сигнал (логическая единица) поступает на вход установки в ноль триггера 35, на входе которого появляется отрицательный перепад напряжения и тем самым запрещается чтение информа0 ции из регистров. Кроме того, сигнал с выхода триггера 35 (логический ноль) поступает на вход элемента И-НЕ 37, выход которого соединен с управляющим входом ключа, инвертируется и открывает ключ 6.

5 Длительность задержки сигнала в элементе 36 выбирается из условия полного завершения всего цикла вычислений.

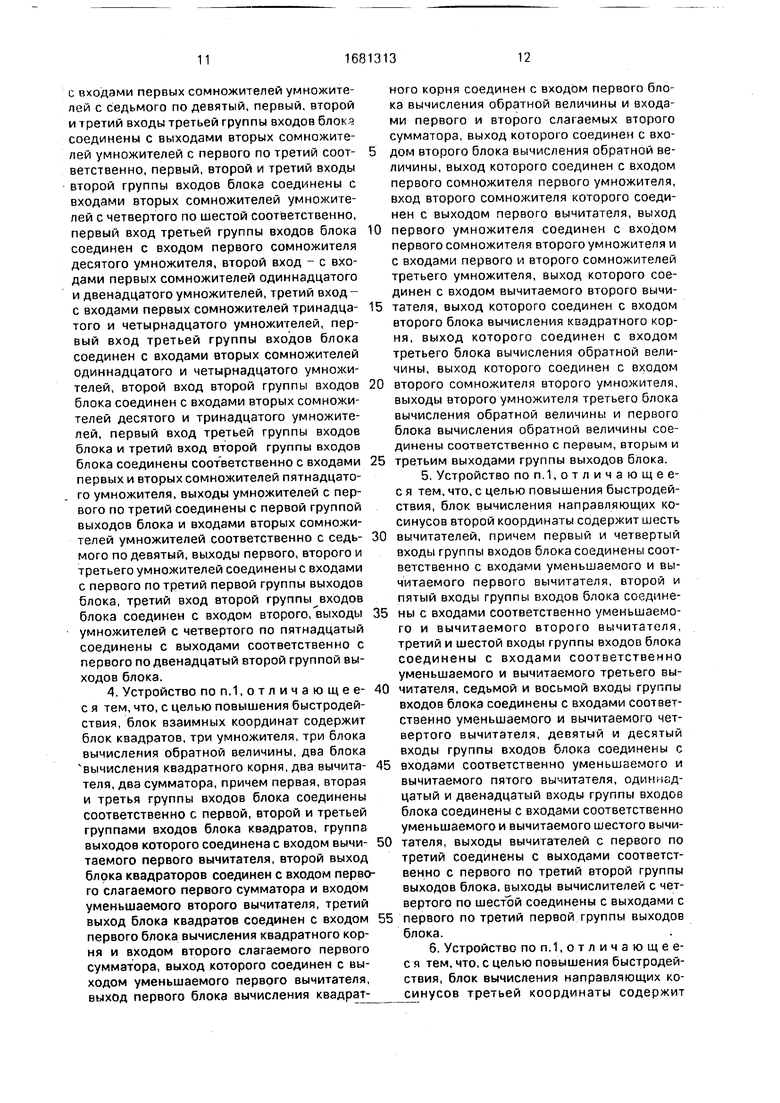

Процесс вычислений для заданного примера представлен в таблице.

Формула изобретения

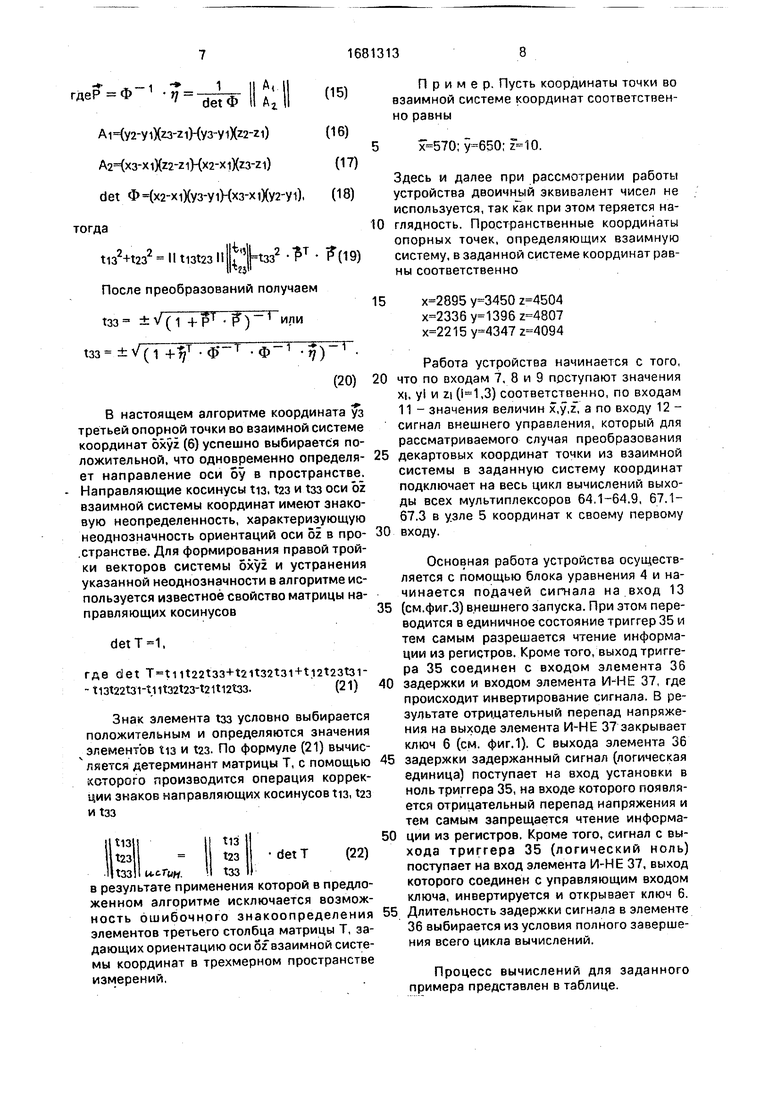

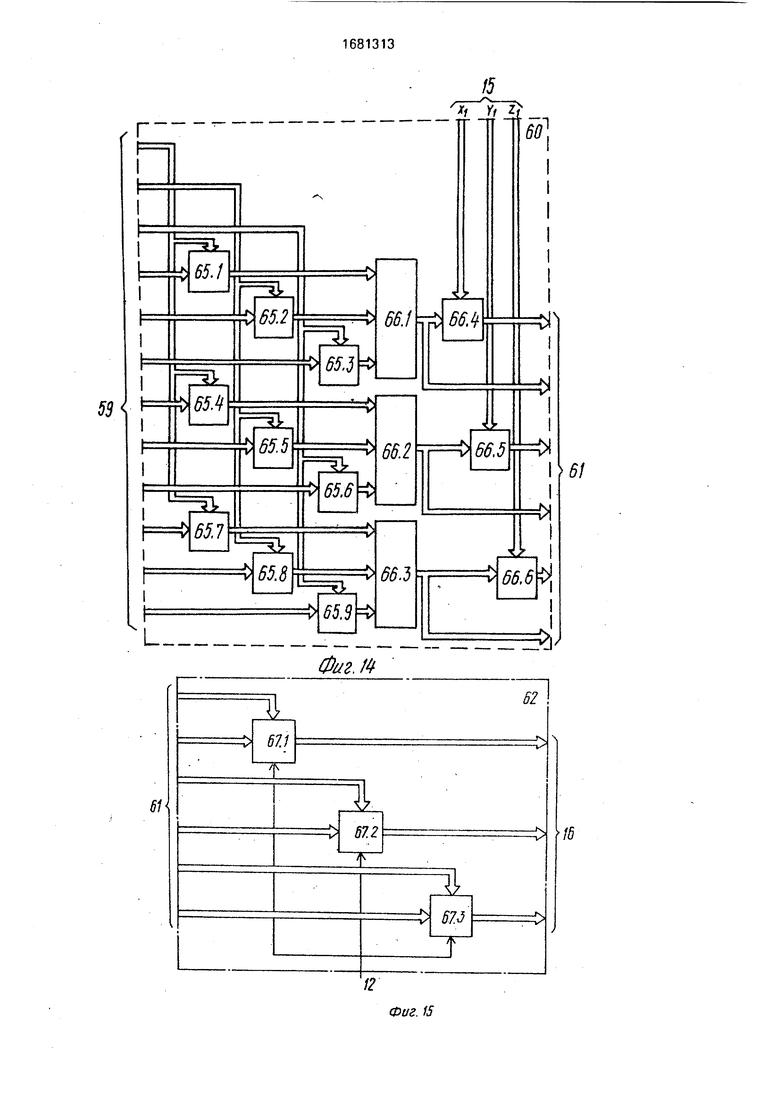

1, Устройство для преобразования координат, содержащее блок формирования координат, входной коммутатор и блок управления, причем группа выходов входного коммутатора соединена с первой группой входов блока формирования координат, о т- личающееся тем, что, с целью расширения класса решаемых задач за счет возможности преобразования из заданной декартовой системы координат во взаимную декартовую систему и обратно, в него дополнительно введены блок формирования разностей, блок взаимных координат, блок вычисления направляющих косинусов первой координаты, блок вычисления направляющих косинусов второй координаты, блок вычисления направляющих косинусов третьей координаты, блок вычисления детерминанта, выходнойкоммутатор, три регистра и ключ, причем группа входов первой оординаты, группа входов второй координаты и группа входов третьей координаты устройства соединены с информационными входами соответственно первого, второго и третьего регистров, выходы которых соединены соответственно с первой, второй и третьей группами входов блока формирования разностей, первая, вторая и третья груп- пы выходов которого соединены соответственно с первой, второй и третьей группами входов блока взаимных координат, группа выходов которого соединена с первой группой входов блока вычисления направляющих косинусов первой координаты, вторая и третья группы входов которого соединены соответственно с второй и третьей группами выходов блока формирования разностей, первая и вторая группы выходов блока вычисления направляющих косинусов первой координаты соединены с первыми группами входов блока вычисления детерминанта и блока вычисления направляющих косинусов второй координаты соответственно, первый выход блока вычисления направляющих косинусов второй координаты соединен с первой группой входов блока вычисления направляющих косинусов третьей координаты, группа выходов которого соединена с второй группой входов блока вычисления детерминанта, третья группа входов которого соединена с второй группой выходов блока вычисления направляющих косинусов второй координаты, группа выходов блока вычисления детерминанта соединена с первой группой информационных входов входного коммутатора, вторая группа информационных входов которого соединена с входом координат

во взаимной системе устройства, третья группа информационных входов входного коммутатора соединена с входом первого регистра и второй группой входов блока

5 формирования координат, группа выходов которого соединена с группой информационных входов выходного коммутатора, группа выходов которого соединена с группой информационных входов ключа, выход кото0 рого является выходом результата устройства, вход константы которого соединен с второй группой входов блока вычисления направляющих косинусов третьей координаты, вход запуска и признака коммутации

5 устройства соединены соответственно с входом запуска блока управления и управляющими входами входного и выходного коммутаторов, первый и второй выходы блока управления соединены с входами разре0 шения считывания регистров с первого по третий и входом разрешения кпюча соответственно.

0 соответственно и с четвертого по шестой соответственно, третий, второй и первый выходы второй группы входов блока соединены с входами вычитаемых вычитателей с первого по третий соответственно и с входа5 ми уменьшаемых седьмого, восьмого и девятого вычитателей соответственно, третий, второй и первый входы первой группы информационных входов соединены с входами вычи i эемых вычитателей с четвертого по

0 шестой соответственно и с седьмого по девятый соответственно, выходы вычитателей с первого по третий соединены с выходами с первого по третий соответственно первой группы выходов блока, выходы вычитателей

5 с четвертого по шесток соединены с выходами с первого по третий соответственно второй группой выходов блока, выходы вычитателей с седьмого по девятый соединены с выходами с первого по третий соответст0 венно третьей группой выходов блока,

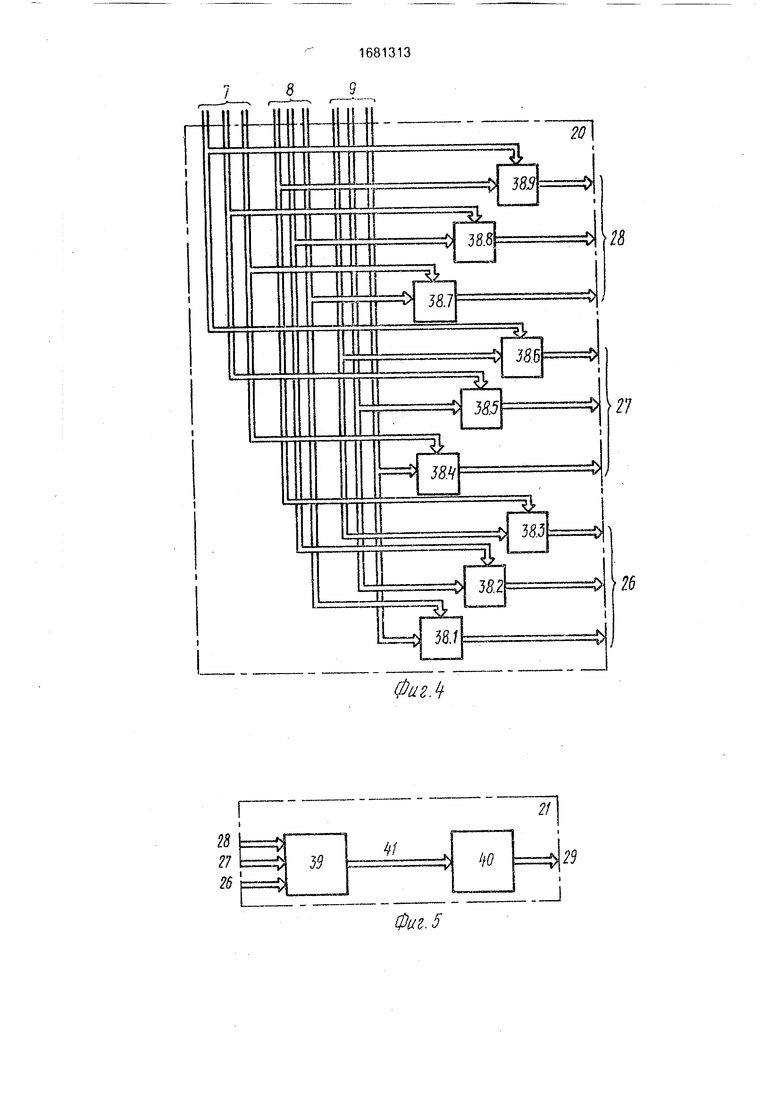

3,Устройство поп.1,отличающее- с я тем, что, с целью повышения быстродействия, блок вычисления направляющих косинусов первой координаты содержит

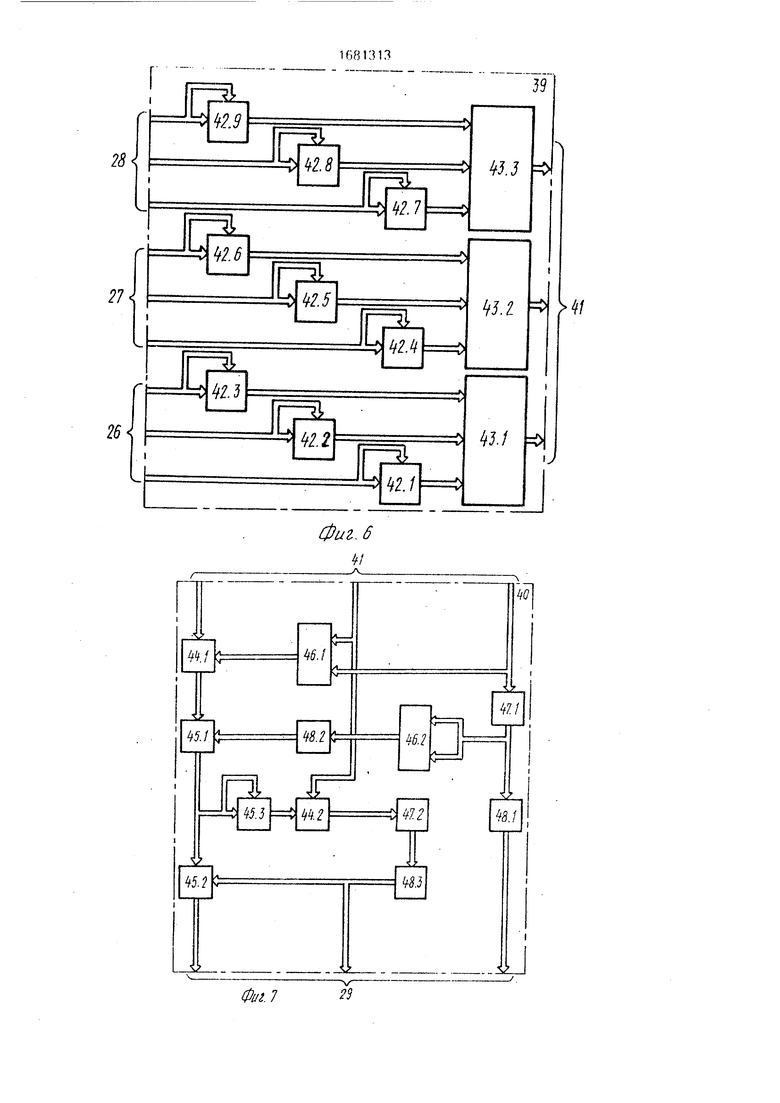

5 пятнадцать умножителей, причем первый вход первой группы входов блока соединен с входами первых сомножителей умножителей с первого по третий, второй вход - с входами первых сомножителей умножителей с четвертого по шестой, а третий вход с входами первых сомножителей умножителей с седьмого по девятый, первый, второй и третий входы третьей группы входов блока соединены с выходами вторых сомножителей умножителей с первого по третий соот- ветственно, первый, второй и третий входы второй группы входов блока соединены с входами вторых сомножителей умножителей с четвертого по шестой соответственно, первый вход третьей группы входов блока соединен с входом первого сомножителя десятого умножителя, второй вход - с входами первых сомножителей одиннадцатого и двенадцатого умножителей, третий вход- с входами первых сомножителей тринадца- того и четырнадцатого умножителей, первый вход третьей группы входов блока соединен с входами вторых сомножителей одиннадцатого и четырнадцатого умножителей, второй вход второй группы входов блока соединен с входами вторых сомножителей десятого и тринадцатого умножителей, первый вход третьей группы входов блока и третий вход второй группы входов блока соединены соответственно с входами первых и вторых сомножителей пятнадцатого умножителя, выходы умножителей с первого по третий соединены с первой группой выходов блока и входами вторых сомножителей умножителей соответственно с седь- мого по девятый, выходы первого, второго и третьего умножителей соединены с входами с первого по третий первой группы выходов блока, третий вход второй группы входов блока соединен с входом второго, выходы умножителей с четвертого по пятнадцатый соединены с выходами соответственно с первого по двенадцатый второй группой выходов блока.

шесть умножителей, два блока вычисления обратной величины, сумматор, блок вычисления квадратного корня, причем первый вход группы входов блока соединен с входом первого блока вычисления обратной величины, второй и третий входы группы входов блока соединены с входами первых сомножителей первого и второго умножителей, входы вторых сомножителей которых объединены и соединены с выходом первого блока вычисления обратной величины, выходы первого и второго умножителей соединены с входами первых и вторых сомно- жителей соответственно третьего и четвертого умножителей, выходы которых соединены с входами соответственно первого и второго слагаемых сумматора, вход третьего слагаемого которого соединен с второй группой входов блока, выход сумматора соединен с входом второго блока вычисления обратной величины, выход которого соединен с входом блока вычисления квадратного корня, выход которого сое- динен с входами первых сомножителей пятого и шестого умножителей, входы вторых сомножителей которых соединены с выходами соответственно первого и второго умножителей, выходы пятого умножителя, шестого умножителя и блока вычисления квадратного корня соединены с первым, вторым и третьим выходами группы выходов блока.

восьмого и двенадцатого умножителей, второй вход с входами вторых сомножителей девятого и одиннадцатого умножителей, а третий вход - с входами вторых сомножите- 5 лей седьмого и десятого умножителей, выходы умножителей с седьмого по девятый соединены с входами слагаемых соответственно с первого по третий первого сумматора, выходы умножителей с десятого по

0 двенадцатый соединены с входами слагаемых соответственно с первого по третий второго сумматора, выходы первого и второго сумматоров соединены с входами соответственно уменьшаемого и вычитаемого

5 вычитателя, выход которого соединен с входом первого сомножителя умножителей с тринадцатого по пятнадцатый, входы вторых сомножителей которых соединены соответственно с первым, вторым и третьим

0 входами второй группы входов блока, первый, второй и третий входы первой группы входов блока, первый, второй и третий входы третьей группы входов блока и выходы умножителей с тринадцатого по пятнадца5 тый соединены с выходами соответственно с первого по девятый группы выходов блока. 8. Устройство поп.1,отличающее- с я тем, что, с целью повышения быстродействия, выходной коммутатор содержит

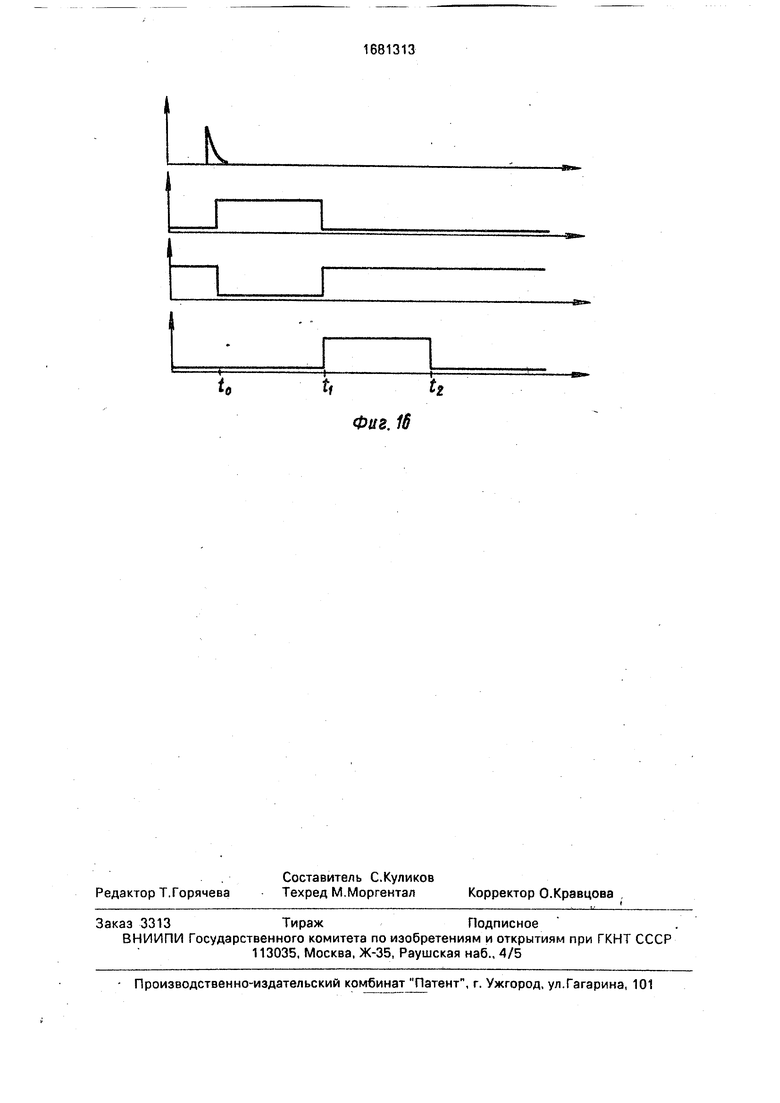

0 три мультиплексора, причем первый, третий, пятый входы группы входов блока соединены с первыми информационными входами мультиплексоров с первого по третий соответственно, второй, четвертый и

5 шестой входы группы входов выходного коммутатора соединены с вторыми информационными входами мультиплексоров с первого по третий соответственно, выходы которых соединены соответственно с пер0 вым, вторым и третьим выходами группы выходов выходного коммутатора, управляющий вход которог о соединен с управляющими входами мультиплексоров с первого по третий

5 9. Устройство поп,1,отличающее- с я тем, что, с целью повышения быстродействия, входной коммутатор содержит три вычитателя и девять мультиплексоров, причем второй вход первой группы входов вход0 ного коммутатора соединен с первыми информационными входами первого и второго мультиплексоров, третий вход первой группы входов входного коммутатора соединен с первыми информационными входа5 ми третьего и четвертого мультиплексоров, четвертый вход первой группы входов входного коммутатора соединен с вторыми информационными входами первого и второго мультиплексоров, шестой вход первой группы входов входного коммугаюрз соединен

с первыми информационными входами пятого и шестого мультиплексоров, седьмой вход первой группы входов входного коммутатора соединен с вторыми информационными входами третьего и четвертого .t , мультиплексоров, восьмой вход первой группы входов входного коммутатора соединен с вторыми информационными входами пятого и шестого мультиплексоров, первый вход второй группы входов входно- го коммутатора соединен с входом уменьшаемого первого вычйтателя и первым информационным входом седьмого мультиплексора, второй информационный вход которого соединен с выходом первого вычйтателя, второй вход второй группы входов входного коммутатора соединен с входом уменьшаемого второго вычйтателя и первым информационным входом восьмого мультиплексора, второй информационный вход которого соединен с выходом второго вычйтателя, третий вход второй группы входов входного коммутатора соединен с входом уменьшенного третьего вычйтателя и с первым информационным входом девятого мультиплексора, второй информационный вход которого соединен с выходом третьего вычйтателя, входы с первого по третий третьей группы входов соединены с входами вычитаемых выч йтателёй соответствен- но с первого .по третий, выходы мультиплексоров с седьмого по девятый, первый вход первой группы входов входного коммутатора, выходы второго четвертого, первого мультиплексоров, пятый вход пер-

вой группы входов входного: коммутатора, выходы шестого, третьего и пятого мультиплексоров и девятый вход первой группы входо в входного коммутатора соединены с выходами с первого по двенадцатый соответственно входного коммутатора.

Ю

Продолжение таблицы

7 8 9

/4

ФигЛ

Фиг, 5

л

Т

№

/К

л

Г

(p

#

Uli:t99l

Фиг.З

MV

Yr

//

Z

Фиг. ft

ft

Г

Mte

S3

М

Ф

L.

. /

Л Yi Z

60

0 Ф

./

o.

$}

5/

M

О

.3

,5Й

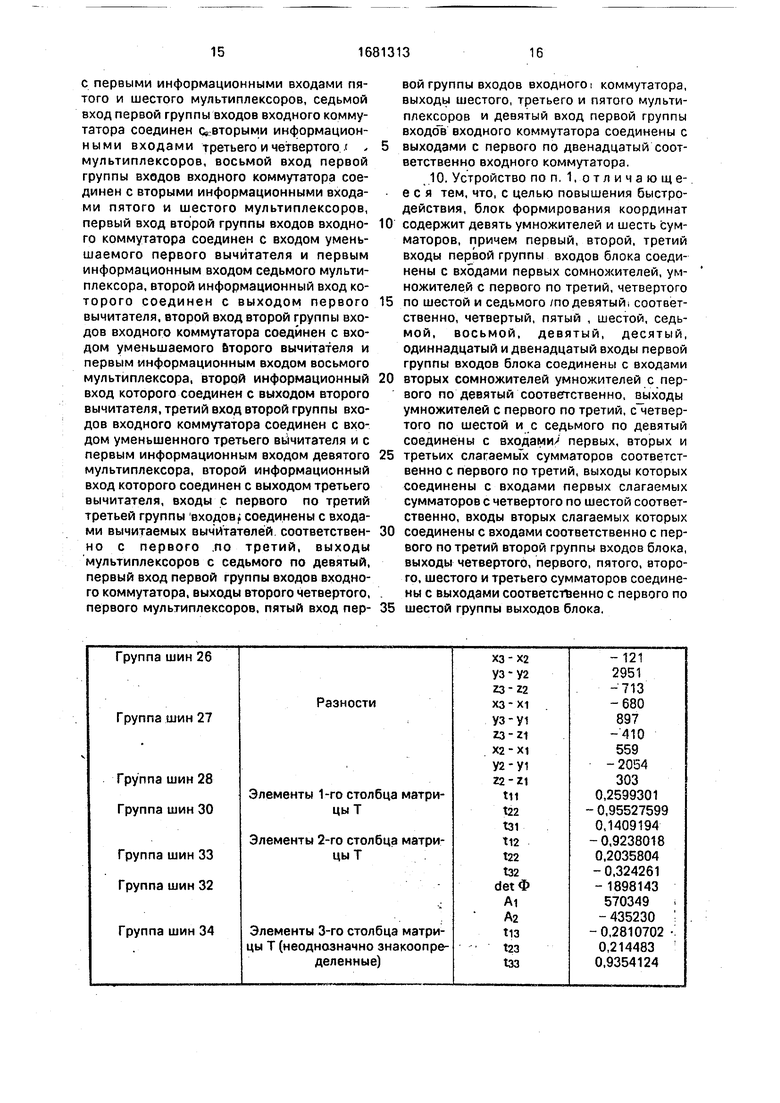

Фиг 15

L

tofftz

Фиг. 16

-

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для преобразования координат | 1983 |

|

SU1141405A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-09-30—Публикация

1989-08-22—Подача