42

(Л

СП

ел

14)

Изобретение относится к вычислительной технике, может быть использовано при отладке программ специализированных систем (СЦВС) реального времени и является усовершенствованием устройства по авт. ев, ,

№ 1348841 .

Цель изобретения - сокращение времени отладки программ.

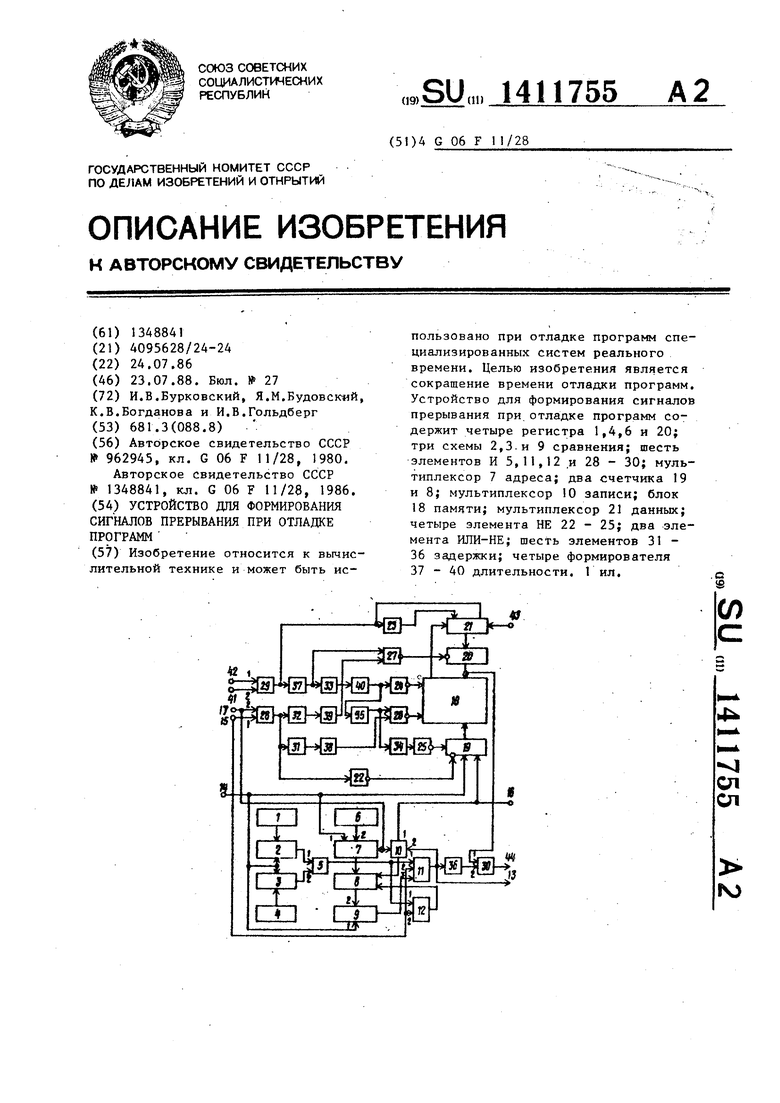

На чертеже представлена схема устройства для формирования сигналов прерьгоания при отладке программ.

Устройство содержит первый регистр 1 ,. первую 2 и вторую 3 схемы

сравнения, второй регистр 4, первый элемент И 5, четвертый регистр 6, мультиплексор 7 адреса, второй счетчик В, третью схему 9 сравнения, мультиплексор 10 записи, второй 11 и шестой 12 элементы И, второй выход 13 прерывания, адресный вход 14, вход 15 строба адреса, вход 16 на чальной установки, первый вход 17 установки режима, блок 18 памяти, первый счетчик 19, третий регистр 20, мультиплексор 21 данных, первый 22, второй 23, третий 24 и четвертый 25 элементы НЕ, первый 26 и второй 27 элементы ИЛИ-НЕ, третий 28, четвертый 29 и пятый 30 элементы И, пер вый 3, второй 32, третий 33, четвертый .34, пятый 35 и шестой 36 элементы задержки, первый 37, второй 38, третий 39 и четвертый 40 формирователи длительности, второй вход 14

установки режима, вход 42 строба даи ных, вход 43 данных и первый выход 44 прерывания.

,Работа устройства начинается с установки исходных данных в регистры 1,4- и-6 и счетчик 19 и разметки блока 18 памяти. На регистрах 1 и 4 устанавливаются верхняя и нижняя граница области памяти ЭВМ, отведенной для хранения команДд на регистре 6 - начальньй адрес отлаживаемой программы, а на счетчике 19 - начальный адрес блока 18. Загрузка резисторов 1,4 и 6 может выполняться с

лицевой панели устройства или в простейшем варианте они могут быть выполнены в виде тумблерных наборников на лицевой панели устройства,

В режиме загрузки исходных данных на первом выходе 17 установки режима устанавливается на уровень логического

О

а на втором входе 41 установки режима - уровень логической

0

0

5

1 5 что соответствует режиму записи в блок 18 и вводу начального адреса программы в счетчик 8,

С входа 17 устройства на управляющие входы мультиплексоров 7 и 10 поступает управляющий потенциал, соответствующий вводу начального адреса с регистра 6 через мультиплексор 7 в счетчик 8 под управлением сигнала, поступающего с входа 16 устройства через мультиплексор 10 на установочный вход счетчика 8. Одновременно сигнал с входа 16 устанавливает счетчик 19 в начальное (нулевое) состо9ние. На входы 43 и 42 устройства подаются от внешнего устройства соответственно данные для записи в блок 18 памяти и сопровождающий их строб данных. Строб данных через элемент И 29 проходит на установочный вход мультиплексора 21, разрешая прохождение данных с входа 43 устройства через мультиплексор 21 на вход регистра 20. Кроме того., ,сигнал с выхода элемента И 29 после формирования по длительности формирователем 37 через второй элемент ИЛИ- НЕ 27 поступает на тактовый вход регистра 20, осуществляя занос в регистр данных с входа 53 устройства.

Сигнал с выхода формирователя 37 после задер}кки на элементе ЗЗ, необ- ходимый для обеспечения записи дан™. ных в регистр 20, формируется по длительности на формирователе 40 и через элемент НЕ 24 поступает отрицательным сигналом на режимный вход записи блока 18„ Одновременно сигнал с вь1хода формирователя 40 после задержки на четвертом элементе 35 задержки на время, определяемое требованиями временной диаграммы блока 18 памяти, через первый элемент ИЛИ-НЕ 26 .отрицательным сигналом пос тупает на вход опроса блока 18 памяти.

0

5

0

В результате сигналы на входах опроса и записи обеспечивают запись данных с регистра 20 по адресу, установленному на счетчике 19„ Прн этом сигнал с выхода элемента 35 задержки после задержки на четвертом элементе 34 задержки на время, необходимое для записи информации в блок 18 памяти, через четвертый элемент НЕ 25 поступает на счетный вход счетчика 19, увеличивая его содержимое на 1, таким образом подготавливая

код адреса блока 18 к приходу следующих данных на вход 43 устройства.

Последовательно записывая данные в блок 18 памяти, например единицу в выделенный разряд, с входа 43 устройства но стробу с входа 42 по адресам, совпадагошим-с адресами отлаживаемой программы, в которых при наличии адресного перехода требуется реализация прерывания, осуществляется разметка блока 18 памяти. После заноса исходных данных и разметки блока 18 памяти изменяют управляющие сигналы на первом 17 и втором 41 входах установки режима. На входе 17 устанавливают потенциал высокого уровня (1), на выходе 41 - потенциал низкого уровня (О), что соответствует режиму отладки программ и считывания из блока 18 памяти.

В результате информационные входы счетчика 8 через мультиплексор 7 подключаются к адресным входам 14 устройства, а установочный вход счетчика 8 через мультиплексор.10 - к выходу второго элемента И 11, разрешается прохождение строба адреса с входа 15 устройства через четвертый элемент И 28, подается потенциал низкого уровня на второй установочный вход мультиплексора 21 данных с выхода пятого элемента И 29, запрещающий прохождение данных с входа 43 устройства через мультиплексор 21. Через второй элемент НЕ 23 подается на первый установочный вход мультиплексора 21 потенциал, разрешающий прохождение информации с выхода блока 18 памяти через мультиплексор 21 данных на регистр 20.

Пйсле запуска программы при появ- .лений на входах 41 устройства кода адреса в сопровождении строба адреса на входе 15 производится его анализ на принадлежность полю адресов ПЗУ, т.е. определяется считывается ли в данный момент команда или операнд.

Текущий адрес с входов 14 устройства поступает на первые входы схем

2и 3 сравнения. На выходе схемы 2 сравнения.присутствует положительный потенциал, е сли текущий адрес меньше адреса верхней границы, установленного на регистре 1, а на выходе схемы

3сравнения, - если больще адреса нижней границы, зафиксированного на регистре 4, На выходе элемента И 5 присутствует положительный потенциал

0

5

0

5

0

5

0

5

0

5

если текущий адрес находится в зоне адресов, ограниченной регистрами 1 и 4, что соответствует считыванию команды.

Одновременно с этим текущий адрес сравнивается с содержимым счетчика 8,

8случае равенства этих значений с выхода схемы 9 сравнения на третий вход элемента И 11 поступает запрещающий потенциал, блокирующий появление сигнала на его выходе. При этом по заднему фронту строба адреса с входа 15 устройства через элемент

И 12 поступает на счетный вход счетчика 8 и увеличивает его содержимое на -1-2 (для ЭВМ Элек роника 60).

При несовпадении текущего адреса на первых входах схемы 9 сравнения с .текущим содержимым счетчика 8 схема

9сравнения вырабатьшает разрешающий потенциал. Таким образом, на всех входах элемента И 11 присутствуют разрешающие сигналы и на выход эле-. мента И 11 проходит положительный сигнал, поступающий одновременно через мультиплексор 10 на установочный вход счетчика 8 и через элемент 36 задержки на второй вход элемента

И 30.

в результате в счетчик 8 через мультиплексор 7 заносится новое значение, соответствующее значению текущего адреса на входе 14 устройства, которое далее по заданному фронту строба адреса увеличивается на +2. После этого значение счетчика 8 соответствует адресу следующей команды.

При считывании операнда на выходе элемента 5 присутствует запрещающий потенциал, блокирующий элементы И-11 и 12, текущие значения счетчика 8 не изменяются и на выходе элемента И 11 и соответственно на втором входе эяе- мента И 30 и выходе 13 прерьгеания устройства присутствует запрещающий потенциал.

Сигнал на первом входе элемента И 30 формируется следующим образом,

Строб .адреса с входа 15 устройства через элементы И 28 и НЕ 22 по-| ступает на тактовый вход четвертого регистра 19, занося в него адрес с адресного входа 14 устройства. Потенциал низкого уровня с выхода элемента И 29 через формирователя 37 и 40 и элемент 33 задержки поступает на вход элемента НЕ 24 и после инвертирования передается на вход записи блока 18 памяти.

Положительный сигнал с выхода элемента И 28 задерживается, на элементе 31 задержки на время, необходимое для записи в счетчик 19 адреса с входа 14 устройства, и после формирования по длительности на формирователе 38 через .элемент ИЛИ-НЕ 26 отрицательным импульсом поступает |на вход опроса блока 18 памяти, Со- |четание потенциала высокого уровня |на входе записи и отрицательного |сигнала на входе опроса, блока 18 па- |мяти соответствует режиму считывания информации из блока 18 памяти на |первый информационный вход мультиплексора 21, Так как на первом установочном входе мультиплексора 21 в режиме считывания присутствует разрешающий потенциал, информа- ция проходит через мультиплек- Icop 21 на вход регистра 20. При этом |Сигнал с выхода элемента И 28 задер- ивается элементом 32 задержки на время, необходимое для считьтания ин }формации из блока 18 памяти, формиру |ется по длительности на формировате- |пе 39 и через элемент ИЛИ-НЕ 27 по- |ступает на тактовый вход регистра. 20 Ьбеспечивая занос в него информации 3 блока 18 памяти. ; Если по .адресу, присутствующему (на адресном входе 14 устройства, из Ьпределенного разряда блока 18 памя- |ги в регистр 20 и далее на первый Ьход элемента И 30 поступает 1 (занесенная по указанному адресу в ежиме разметки блока 18 памяти), то Ьри появлении сигнала на втором вхо- fte элемента. И 30 на выходе 44 устройства появляется сигнал прерывания.

При. этом элемент 36 задержки обеспечивает задержку сигнала на втором :Входе элемента И 30 на время считывания информации из блока 18 памяти i на первый вход элемента И 30.

Формула изобретения

Устройство для формирования сигналов прерывания при отладке программ по авт. св. № 1348841, о т л и ч а ю ш е е с я тем, что, с целью сокращения времени отладки программ, в устройство введены четвертьй регистр, второй счетчик, третья схема сравнения, шестой элемент Н, мультиплексор

адреса и мультиплексор записи, причем выход четвертого регистра соединен с первым информационным входом мультиплексора адреса, адресный вход устройства соединен с входом первого

сравниваемого числа .третьей схемы сравнения и с вторым информационным входом мультиплексора адреса, выход которого соединен с информационным входом второго счетчика, первый вход

установки режима устройства соединен с управляющими входами мультиплексора адреса и мультиплексора записи, выход которого соединен с установочным входом второго счетчика, выход

которого соединен с входом второго сравниваемого числа третьей схемы сравнения, вькод которой соединен с третьим -входом второго элемента И, выход второго элемента И является вт.орым выходом прерывания устройства и соединен с первым информационным входом мультиплексора записи, вход начальной установки устройства соединен с вторым информационнЕлм

входом мультиплексора записи, выход первого элемента И соединен с первым входом шестого элемента И, выход которого соединен со счетным входом второго счетчика, вход строба адреса устройства соединен с вторым входом

шестого элемента И,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования сигналов прерывания при отладке программ | 1986 |

|

SU1348841A1 |

| Устройство для формирования сигналов прерывания при отладке программ | 1986 |

|

SU1312582A2 |

| Устройство для формирования сигналов прерывания при отладке программ | 1986 |

|

SU1405061A2 |

| Устройство для отладки микропроцессорных систем | 1989 |

|

SU1672455A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для отладки программ | 1984 |

|

SU1238086A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| Устройство для формирования сигналов прерывания при отладке программ | 1984 |

|

SU1185343A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1587514A1 |

| Устройство для ввода информации | 1986 |

|

SU1345184A1 |

Изобретение относится к вычислительной технике и может быть использовано при отладке пpoгpa м специализированных систем реального времени. Целью изобретения является сокращение времени отладки программ. Устройство для формирования сигналов прерывания при,отладке программ содержит четыре регистра 1,4,6 и 20; три схемы 2,3-и 9 сравнения; шесть элементов И 5,11,12 и 28 - 30; мультиплексор 7 адреса; два счетчика 19 и 8; мультиплексор 10 записи; блок 18 памяти; мультиплексор 21 данных; четыре элемента НЕ 22 - 25; два элемента ИЛИ-НЕ; шесть элементов 31 36задержки; четыре формирователя 37- 40 длительности. Гил. .с

| Устройство для прерывания при отладке программ | 1980 |

|

SU962945A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для формирования сигналов прерывания при отладке программ | 1986 |

|

SU1348841A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-07-23—Публикация

1986-07-24—Подача