1

Изобретение относится к в.1числи- тельной технике и может быт использовано при отладке программ специализированных цифровых вычислительных систем (СЦВС) pea.-if,Horo времени.

Целью изобретения является расширение функ11иоиал1 ных возможностеГ устройства за счет запоминания множества точек адресного поля )ВМ, при обращении к кторым требуется форми- ровар1ие сиг нала прерывания.

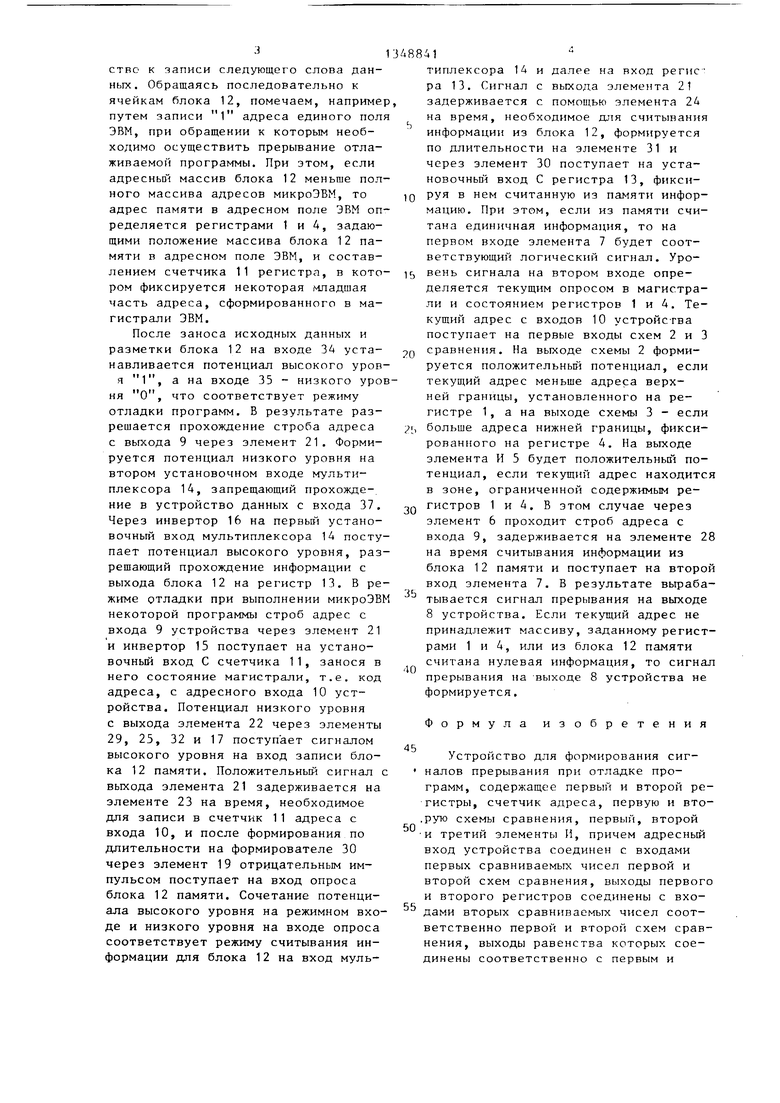

На чертеже схематично изображено устройство для формирования сигналов прерывания при отладке программ.

Предлагаемое устройство содержит первый регистр 1, первую 2 и вторую схемы сравнения, второй регистр , первый 5, второй 6 и трети1 7 элементы И, вь1ход 8 прерывания ycTpofi- ства, вход 9 строба адреса, адресньи вход 10 устройства, счетчик 11 адреса, блок 12 памяти, третий регистр 13, мультиплексор 1А данных, nepFibui

15, второй 16, третий 17 и четвертый 18 элементы HP , первьиЧ 19 и второй 20 элементы lUIH-HF::, четвертый 21 и пятый 22 элементы И, первый 23, второй 24, третий 25, четверУый 26, пятый 27 и шестоГ 28 элемс нты задержки, первый 29, второй 30, третий 31 и четвертый 32 формировате:п1 длит( ности, вход 33 начальной установки ycrpoi icTBa, .B.iii 34 и второй 35 входы установки режима устраиства, вход 36 строба данных, вход 37 данных устройства.

Рассмотрим работу устройств ; совместно с отлаживаемой СЦВС, построенной на базе IBM типа Э.иектрони- ка-60. Адресные ВХОДЕ. 10 устроггст- ва подключены к магистрадш микроЭВМ, через которую осуществляется обмен информацией между ее различными уст1

ройствами. Вход

строба адреса устройства подключается, например, к шине Обмен микроЭВМ, Сигналы на входы начальной, установки 33, первы; 34 и BTopoi i 35 входы установки режима работы подаются, например, с лицевои панели управле.:ия устройства (не показана). :-:од i7 данных и вход 36 строба ланн(-1х подключены к внешнему ycTpoiicTBy, наг ример стендовой ЭВМ, обеспечивающей загшсь информации в блок 12 памяти (разметку памяти). Выход 3 прерыр.ания устройства подключается к системе прерывания СЦВС. Работа устрч;1С Т1а начинается с раз

3

10

Hi

0

488412

метки блока 12 памяти и установки исходных данных в регистрах 1 и 4 и счетчике 11. На регистрах 1 и 4 устанавливаются верхняя и нижняя гра- Н1ЩЫ массива адресов единого поля микро 1ВМ, контролируемых данным уст- poiicTBOM, а на счетчике 1 1 - началь- адрес блока 12 памяти. Загрузка регистров 1 и 4 может вьтолняться с лицевой панели устройства, В простейшем варианте регистры 1 и 4 могут быть выполнены в виде тумблерных на- борников на лицевой панели,

В режиме загрузки исходных данных на первый вход 34 установки режима подается сигнал уровня О, а на второй вход 35 - 1, что соответствует режиму записи в блок 12 памяти, Сигналом с входа 33 устройства устанавливают в начальное (нулевое) состояние счетчик 11, На входы 37 и 36 устройства подают от внешнего устройства соответственно данные для записи в блок памяти и сопровождающий их строб данны Х, Строб данных через элемент И 22 проходит на второй уста- новленнь1й вход мультиплексора 14, разрешая прохождение данных с входа 37 устройства через мультиплексор 14 на вход регистра 13, Кроме того, сигнал с выхода элемента 22 после формирования по д;штельности на формирователе 29 через первый вход элемента 20 поступает на тактовый вход С регистра 13, осушествляя запись в него данных. Сигнал с выхода формирователя 29 после задержки на элементе 25 на время заноса данных в регистр 13 формируется по длительности на эле- ме}1те 32 и через инвертор 17 поступает на режимньи вход записи блока 12 памяти. Одновременно сигнал с выхода форгчирователя 32 после задержки на элементе 27 на время, определяемое требованиями временной диаграммы блока памяти, через элемент ИЛИ-НЕ 19 низким уровнем поступает на вход опроса блока 12 памяти, В результате на входах блока 12 памяти формируются сигналы, обеспечивающие запись да1П1ых с входа 37 по адресу, установленному на счетчике 11. Цри этом с выхода элемента 27 после задержки на элементе 26 на время записи информации через инвертор 18 поступает на счетньм вход счетчика 11, увеличивая его содержимое на 1, тем самым подготавливая устрой30

ЗЬ

111

45

ЬО

55

ство к записи следующего слова данных. Обращаясь последовательно к ячейкам блока 12, помечаем, например путем записи 1 адреса единого поля ЭВМ, при обращении к которым необходимо осуществить прерывание отлаживаемой программы. При этом, если адресньо1 массив блока 12 меньше полного массива адресов микроЭБМ, то адрес памяти в адресном поле ЭВМ определяется регистрами 1 и А, задающими положение массива блока 12 памяти в адресном поле ЭВМ, и составлением счетчика 11 регистра, в котором фиксируется некоторая младшая часть адреса, сформированного в магистрали ЭВМ.

После заноса исходных данных и разметки блока 12 на входе 34 устанавливается потенциал высокого уров- я 1, а на входе 35 - низкого уровня О, что соответствует режиму отладки программ. В результате разрешается прохождение строба адреса с выхода 9 через элемент 21. Формируется потенциал низкого уровня на втором установочном входе мультиплексора 14, запрещающий прохождение в устройство данных с входа 37. Через инвертор 16 на первый установочный вход мультиплексора 1А поступает потенциал высокого уровня, разрешающий прохождение информации с выхода блока 12 на регистр 13. В режиме отладки при выполнении микроЭВМ некоторой программы строб адрес с входа 9 устройства через элемент 21 и инвертор 15 поступает на установочный вход С счетчика 11, занося в него состояние магистрали, т.е. код адреса, с адресного входа 10 устройства. Потенциал низкого уровня с выхода элемента 22 через элементы 29, 25, 32 и 17 поступает сигналом высокого уровня на вход записи блока 12 памяти. Положительный сигнал с выхода элемента 21 задерживается на элементе 23 на время, необходимое для записи в счетчик 11 адреса с входа 10, и после формирования по длительности на формирователе 30 через элемент 19 отрицательным импульсом поступает на вход опроса блока 12 памяти. Сочетание потенциала высокого уровня на режимном входе и низкого уровня на входе опроса соответствует режиму считывания информации для блока 12 на вход муль0

Ь

0

0

ь

0

5

0

5

типлексора 1А и далее на вход регис ра 13. Сигнал с выхода элемента 21 задерживается с помощью элемента 24 на время, необходимое для считывания информации из блока 12, формируется по длительности на элементе 31 и через элемент 30 поступает на уста- HOBO4Hbrfi вход С регистра 13, фиксируя в нем считанную из памяти информацию. При этом, если из памяти считана единичная информация, то на первом входе элемента 7 будет соответствующий логический сигнал. Уровень сигнала на втором входе определяется текущим опросом в магистрали и состоянием регистров 1 и 4. Текущий адрес с входов 10 устройства поступает на первые входы схем 2 и 3 сравнения. На выходе схемы 2 формируется положительный потенциал, если текущий адрес меньше адреса верхней границы, установленного на регистре 1, а на выходе схемы 3 - если больше адреса нижней границы, фиксированного на регистре 4. На выходе элемента И 5 будет положительньп потенциал, если текущий адрес находится в зоне, ограниченной содержимым регистров 1 и 4. В этом случае через элемент 6 проходит строб адреса с входа 9, задерживается на элементе 28 на время считывания информации из блока 12 памяти и поступает на второй вход элемента 7. В результате вьфаба- тывается сигнал прерывания на выходе 8 устройства. Если текущий адрес не принадлежит массиву, заданному регистрами 1 и 4, или из блока 12 памяти считана нулевая информация, то сигнал прерывания на выходе В устройства не формируется.

Формула изобретения

Устройство для формирования сигналов прерывания при отладке программ, содержащее первый и второй регистры, счетчик адреса, первую и вто- .рую схемы сравнения, первый, второй и третий элементы И, причем адресный вход устройства соединен с входами первых сравниваемых чисел первой и второй схем сравнения, выходы первого и второго регистров соединены с входами вторых сравниваемых чисел соответственно первой и второй схем сравнения, выходы равенства которых соединены соответственно с первым и

вторым входами первого элемента И, выход первого элемента И соединен с первым входом второго элемента И, вход строба адреса устройства соединен с вторым входом второго элемента И, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет запоминания множества точек адресного поля ЭВМ, при обращении к которым требуется формирование сигнала прерывания, в устройство введены блок памяти, третий регистр, мультиплексор данных, первый, второй, третий и четвертый элементы НЕ, первьй и второй элементы ИЛИ-НЕ, четвертый и пятый элементы И, шесть элементов задержки, четыре формирователя длительности, причем входы стро- 2о вторым входом первого элемента

ба адреса и первый вход установки режима устройства соединены соответственно с первым и вторым входами третьего элемента И, выход которого соединен через последовательно соединенные первый элемент задержки и первый формирователь длительности с первым входом первого элемента ИЛИ-НЕ, через последовательно соединенные второй элемент задержки и второй формирователь длительности - с первым входом второго элемента ИЛИ-НЕ и через первый элемент НЕ - с тактовым входом счетчика адреса, адресный и установочный входы устройства соединены соответственно с информационным входом и входом начальной установки счетчиц адреса, выход которого соединен с адресным входом блока памяти, вход строба данных и второй вход установки режима устройства соединены

25

30

35

40

ИЛИ-НЕ и через пятый элемент заде ки - с входом четвертого элемента выход которого соединен со счетны входом счетчика адреса, вход данн устройства соединен с первым инфо ционным входом мультиплексора дан группа разрядных выходов третьего регистра соединена с группой информационных входов блока памяти с группой входов пятого элемента выход которого является выходом п рывания устройства, выход второго элемента И через шестой элемент з держки соединен со стробирующим в дом пятого элемента И, выходы тре го элемента НЕ и первого элемента ИЛИ-НЕ соединены соответственно с входами записи и обращения блока мяти, выход которого соединен с в рым информационным входом мультип сора данных.

Редактор Е.Копча

Составитель И.Сигалов Техред А.Кравчук

Заказ 4803/49 Тираж 670Подписное

ВНШШИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

348841°

соответственно с первым и вторыми входами четвертого элемента И, выход которого соединен с первым управляющим входом и через второй элемент НЕ - со вторым управляющим входом мультиплексора данных, выход которого соединен с информационным входом третьего регистра, выход четвертого элемента И через третий формирователь длительности соединен с входом третьего элемента задержки и вторым входом второго элемента ИЛИ-НЕ, выход которого соединен с тактовым входом третьего регистра, выход третьего элемента задержки соединен через четвертый формирователь длительности с входом третьего элемента

10

15

НЕ,

через четвертый элемент задержки вторым входом первого элемента

ИЛИ-НЕ и через пятый элемент задержки - с входом четвертого элемента НЕ, выход которого соединен со счетным входом счетчика адреса, вход данных устройства соединен с первым информационным входом мультиплексора данных, группа разрядных выходов третьего регистра соединена с группой информационных входов блока памяти и с группой входов пятого элемента И, выход которого является выходом прерывания устройства, выход второго элемента И через шестой элемент задержки соединен со стробирующим входом пятого элемента И, выходы третьего элемента НЕ и первого элемента ИЛИ-НЕ соединены соответственно с входами записи и обращения блока памяти, выход которого соединен с вторым информационным входом мультиплексора данных.

Корректор М.Пожо

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования сигналов прерывания при отладке программ | 1986 |

|

SU1411755A2 |

| Устройство для формирования сигналов прерывания при отладке программ | 1986 |

|

SU1312582A2 |

| Устройство для формирования сигналов прерывания при отладке программ | 1986 |

|

SU1405061A2 |

| Устройство для отладки программ | 1984 |

|

SU1238086A1 |

| Устройство для формирования сигналов прерывания при отладке программ | 1984 |

|

SU1185343A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для отладки программ | 1989 |

|

SU1674135A1 |

| Устройство для отладки микропроцессорных систем | 1989 |

|

SU1672455A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1425683A1 |

Изобретение относится к цифровой вычислительной технике и предназначено для использования при отладке программ специализированных вычислительных систем реального времени. Цель изобретения - расши10 рение функциональных возможностей устройства. Цель достигается тем, что в устройство, содержащее первый 1, второй 4 регистры, счетчик 11 адреса, первую 2 и вторую 3 схемы срав нения, первый 5, второй 6 и третий 7 элементы И, введены блок 12 памяти, четвертый регистр 13, мультиплексор данных 14, первый 15, второй 16, третий 17 и четвертый 18 элементы НЕ, первый 19 и второй 20 элементы ИЛН-НЕ, четвертый 21 и пятый 22 элементы И, первый 23, второй 24, третий 25, четвертый 26, пятый 27 и шестой 28 элементы задержки, а также первый 29, второй 30, третий 31 и четвертый 32 формирователи длитель ности с соответствующими связями. 1 ил. - S (/ С е

| Устройство для прерывания при отладке программ | 1980 |

|

SU962945A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для формирования сигналов прерывания при отладке программ | 1984 |

|

SU1185343A1 |

| Способ получения молочной кислоты | 1922 |

|

SU60A1 |

Авторы

Даты

1987-10-30—Публикация

1986-06-04—Подача