Изобретение отьюсится к вычис,чите;1ь- ной технике и может быть использовано при отладке программ епециализировапных сие- тем (СЦВС) реального времени я является усовершенствованием изобретения по авт. св. № 1185343.

Целью изобретения является расншре- нне функциональных возможностей устройства за счет запоминании адрееов переходов.

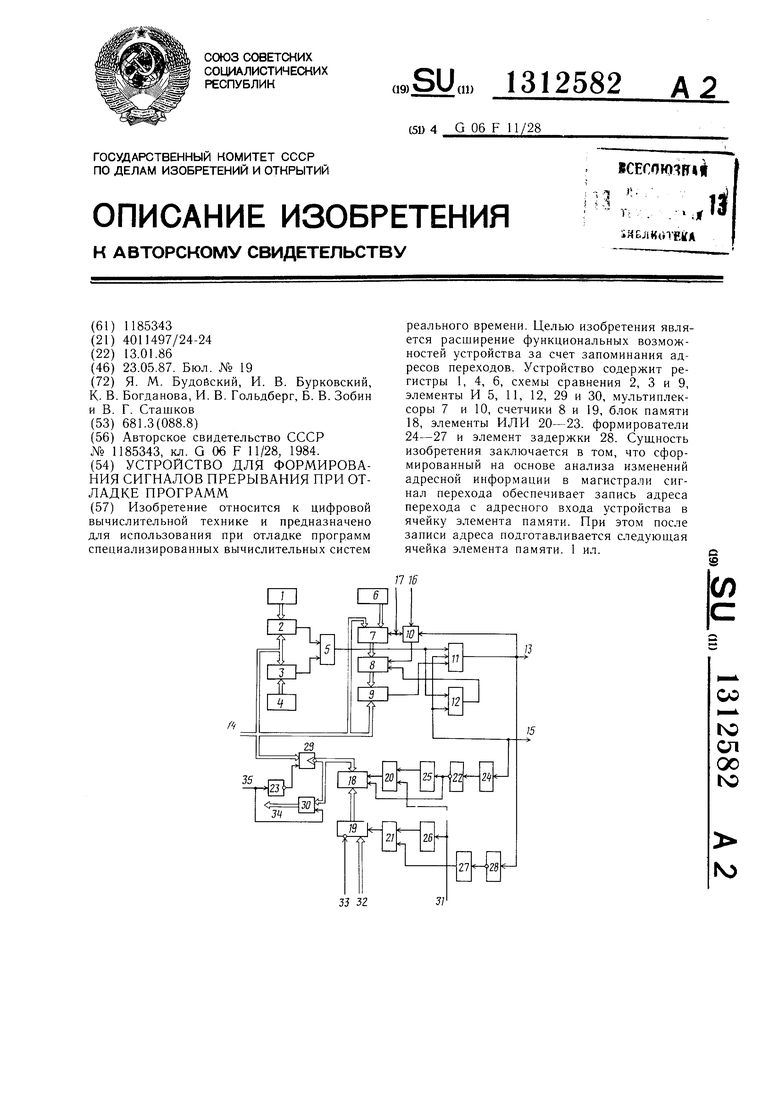

На чертеже представлена схема уст- ройства.

Устройство содержит нервый рег истр 1, первую 2 и вторую 3 схемы сравнения, второй регистр 4, первый элемент И 5, третий регистр 6, мультиплексор 7 адреса, нервый счетчик 8, третью схему 9 сравнения, мультиплексор 10 сигнала записи, второй 11 и третий 12 элементы И, выход 13 прерывания, адресный вход 14, вход 15 строба адреса. вход 16 начальной установки, первый вход 17 установки режима, блок 8 памяти, второй счетчик 19, первый 20 и второй 21 элементы ИЛИ, первый 22 и второй 23 элементы НЕ, первый 24, второй 25, третий 26, чет вертый 27 формирователи длител ности, элемент 28 задержки, четвертый 29 и пятый 30 элементы И, вход 3 опроса, второй ад ресный вход 32, вход 33 установки адреса памяти, информационный выход 34, вто рой вход 35 установки режима уетройст1 а. Рассмотрим работу устройства совместно с отлаживаемой СЦВС, построенной на базе ЭВМ тина «Электроника--60. Адрес11ь:е входы 14 устройства подключены к магистрали микро-ЭВМ, к которой подключены таь;- же ностоянное запоминающее устройство (ПЗУ) для хранения команд и оне)ати1,нос заномипаюнлее устройст во (ОЗУ) для храпения операндов программ (не ноказаны) ОЗУ и ПЗУ имеют раз;1ич1П51е а;феса в едином адресном прос транстне магистрали микро-ЭВМ.

Работа ус 1 ройства 1-1ачинается с установки на регистрах i и 4 верхней и пижпей границ области памяти, отведенной для хранения команд, а на регистре 6 - начального адрса отлаживаемой iiporpaMMiii. В нро етейшем случае регистры 1, 4 li 6 вып.ол- пяютея в виде тумблерных иабпр1-н гчОЗ.

С входа 17 устройе: ва н;, унг)ав..чяк)- щие входы мультинлекеоров 7 н И) ноету- нает управляюнг.П поте:п1иал, соответствую- Н1ИЙ вводу начального a;i.peca с регистра 6 через му,;1ьтип;1ексор 7 и в счетчик 8 под унравлением сигнала, ностунающегг: с входа 16 устройства через мультиплексор 10 на ycтaнoвoчlHJlй вход счетчика 8. Унрав.ляюш.пе сигналы на вход1э1 17 и 18 подаются с лицевой панели устройс П а.

Нос.те заноса начального адреса программы в счетчик 8 изменением унраг.чяю- щего нотенциала па вхол.е 17 yc rpoi-ic r;ia информационные входы счетч1--;ка 8 через мультинлексор 7 подключажтси л аиресшул:

че)ез мультиплексор элемента И. J 1.

к выходу второго

5

0

5

5

5

0

устанавливается во втсрчом ечетчике 19 по сигналу с входа 33 уег юйства начальный адрес зоны блока 18 памяти, отведенной для фиксирования адресов нереходов. В ра- ,почем режиме отладки нрограмм, сонровож- даю1цемся записью адресов переходов в блок 18 памяти, потенциал па втором входе 35 установки режима устройства запрещает прохождение и)формации через пятый элемент И 30 на информационный выход 34 устройетва.

При этом через второй элемент НЕ 23 подается разрешаюнгий потенциал на управ- „чяюпдий вход четвертого элемента И 29 и разрешается нрохо к;ич1ие информац ; --; с первого адресног О 11хода 14 стройства на 1)хол.-выход данных, блока 18 памяти для последующей записи адреса перехода но адресу блока 18, установленному на счетчике 19.

Ноеле 3aiiyci;a прог раммы при ноявлении на входах 14 уст)ойст15а кода адреса в сопровождении строба адреса на входе 15 производится его анализ на принадлежность нолю адрееов ПЗУ, т.е. определяетея, считывается ли в данный момент коман.та -.ли онеранд.

Гекун;ий адрес со зх();;.ов 14 устройства поступает па iieniibie входы схем 2 и 3 сравнения. На выходе ехемы 2 сравнения присутствует ноложнтельный 11оте 1цяал. ес,ти те- кунлий адрес мень не адреса верхней границы, установленного iia pei-истре 1. а на Bi.i- х(;де схемы 3 сравнения еели больн1е адреса нижней 1 {)а1-п-1цы, зафиксиргованного в регистре 4. На выходе схемы И 5 будет но- . ожнтел1 1Цз111 ноте|-|циа,;, если тек чн1;й ал.рес находится в зоне адрееов, ограниченной Н - гнстрами 1 и 4, что соогветстнуст считыванию команды.

Одновременно е этим -reKVHuni a;i,pec

счетчика Н. В значений с ;рет1 Й |;х)д -.ie- занрен1аю1д,1Й но- С)яи,;.е;Н1е с П нала на но i.b) io vi T ;:iv)iicTBa че- i постунаст на счет- VB; iH4HiUie- см о со- ЭПМ «3.;eKv:i(ji.;:случае равенства эт1-1х 9 сравнения на мента И 11 г.остунас т тенцнал, блакнру спцнй п в)1ходе. При aroN; строба адрееа е iixo;ui рез элемент И 12 сигна. iHiHi вход счетчила 8 i .лержнмое на -f 2 для ка-60).

В елучае 1;еео;5нал.;;н;1Я са на нсрвых входах cxeMi i 9 хун1,им соде :1Жнм1лм счетчика 8 тхем;; 9 сравнения вырабат1г1;)ает ,)азрен а10 ний i orcH- . Такнм образом ча всех входах эле- ieirra I l 1 1 чрпс тств ;от разре;накицне i:i i, м на вь;ходе И устройства, iio.Uv iio- чслного V . системе поерь:ва1н:я ЭВМ. чсяв.я- ..тся 1) С1И гн I, i.ib 3bi iai;ii4;;H гчсрывание Ю реализованному переходу в программе. Одновременное появлением сигнала на выходе 13 уетройства сигнал с выхода элемента И 1 через мультиплексор 10 поступает па установочный вход ечетчика 8, но которому в счетчик 8 заносится новое зпаче- ние, еоответетвующее значению текущего адреса, которое по заднему фронту строба адреса увеличивается на . После этого значение счетчика 8 соответствует адресу следующей команды.

В случае считывания операнда на выходе элемента И 5 присутствует запрещающий потенциал, блокирующий элементы И 11 и 12. Текущие значения счетчика 8 не изменяются, и на выходе 13 сигнал не появляется вне зависимости от сигнала на выходе схемы 9 сравнения.

Д. работы устройства необходимо, чтобы адрес вектора прерываний и технологическая программа обслуживания прерывания находились впе зоны адресов ПЗУ, онределяемой регистрами 1 и 4.

Положительный сигнал строба адреса со входа 15. сопровождающий адресную нн(рормапию на входе 14 уетройства, поступает на вход элемента 24, где формируется по д;|ительности. Сигнал с выхода элемента 24 через первый элемент НЕ 22 но- стунает отрипате. гьпым сигналом на режим ный вход записи чтения блока 18 памяти.

Кроме этого, от переднего фронта сиг- пала с выхода Эиел1епта НЕ 22 формируется па втором формирователе 25 длитель; ости сигнал, который поступает на первый вход первого элемепта ИЛИ 20 и с его выхода в виде отрипате.льног о сигнала па вход OFipoca блока 18 памяти. При этом на входе 31 опроса устройст 5а присутствует ноложите.чьный поте1П,иал.

В результате на входе записи чтения и оироспом входе блока 18 памяти присутствуют сигпа.лы отрицательной no.iHp- нести, обеспечиг.ающие выгюлпение операцпи записи адреса с нервого адресного входа Ы устройства чере; четвертый элемент И 29 в 6;ioK 18 памяти по адресу, устапов. пому на счетчшчо 19.

При этом, ec. iii адрес на входе 14 устройства выз1)П1ает юявление положительного ирерызания на выходе 13 устройства, указанный сигнал поступает на вход элемента 28 заде)кки, где инвертируется и задерживаётс.и на время, необходимое дли записи ин(|уо;}мап,ии в блок 18 памяти, и пос.ле формирования но длительности на элементе 27 поступает на первый вход ВТОРОГО э.че.чента И,ПИ 2 I и с его выхода па счет- П1|й вход вгор() ;;-нг:чика 19, увеличивая и;дсржи ;ое счетч;:к;: 19. т.е. 11Одгота ;. П1вая следх ющий адрес илг;ка 18 памяти д.ля записи очере.Ч|К)й ин(Ьо1шапии е иерво|-о ад- pec:ioro ихо;,;; 14 устр(;;п;тва.

При ycJiOBiiii. что скачка адрес на входе 14 vcTiXiHCTBa нроизои ло, на выходе 13 уетройства не формируется сигнал препьпэа(П1я и соответстве1П1О на счетном входе второго счетчи.ка 19 сигнал «-(-1 не появ. -яется, содержимое счетчика 19 не меняется и запись последующей информации в блок 18 памяти с входа 14 устройства происходит но адресу нредыдупхей записи, которая при этом затираетея.

В результате в процессе прогона контрольного варианта отлаживаемой програм .мы по последовательным адресам блока 18 памяти записываются адрееа с входа 14 устройства, в которых происходит скачок адреса ил1 ветвление программы («след программы) .

5 В режиме еъема зафиксированного «следа программы из блока 18 памяти (режим .::ч Т1 вания) из еняется потепщитл на вто- гюл; входе 35 установки режима. В результате гюдаетея разрешаюпшй потенциал па управляющий вход пятого элемента И 30

0 и через второй элемент НЕ 23 запрещающий потенциал па управляющий вход четвертого элемента И 29.

В следетвие этого вход-выход данных блока 18 памяти отключается от адресного входа 14 устройства и через пятый элемент П 30 подключается к информационпому выходу 34 устройства, который может быть подключен, например, к степдово ЭВМ (устройству 1 11дикации или докумептировапия). В режиме считывания lui выходе 13 нрерыр вания и входе 15 строба адреса присут- тствуют отрицателы-:ые потенциалы («О). Соответстве1П10 с выхода э.чемепта НЕ 22 па режим}|ый вход записи-чтения блока 18 памяти передается Г1отепциал высокого уров- ия («1). На первый вход первого элемента ИЛИ 20 и па второй вход второго элемента ИЛИ 21 также подается нотепцпал

высокого ypOBiiH («1).

5

5

45

Пр|-; наличии па входе 31 опроса устройства сигна. К огрицательпо по.чярностп на

-О вход опроса блока 18 памяти через первый элемент ИЛИ 20 nocTvnaeT сигнал отрица- те,1ьной iio.iHpnocTii. С очетаппе па режимном входе записи чтепня и входе опроса б.юка 18 памяти соответствеппо сигпа.юв «1 и «О вызывает считыва;П1е и.нформацпи на информационный выход 34 устройства из блока 18 но адресу, устаповлепнол.у на втором счетчпке 19. При этом пачальный адрес iipn счптыва1П11 быть уста1ювлен заранее со адресного Bxo;ia 32 устрой5Q ства но с1-;гпалу с входа 33 устаповкн адреса.

Од|-:овреме11по от заднего фронта сигнала с входа 31 onfioca уетройства после ф(;рмпрова;1 1Я по дл1: гсльпости па элементе 26 сигнал .ерез второ :)леме1гг ИЛИ 21 но55 ступает на счетный вход вторО1Ч) счетчнка 19, увелггчпвая его содержимое па -(--1, т.е. нод отав,:1пвая с.1ед ;они1Й адрес блока 18 намят.

. Пс следовательно подавая сигналы на вход 31 опроса, обеспечивается считывание из блока 18 памяти всего массива адресов переходов («след программы) на выход 34 устрой-ства.

устройства соединен с вторым входом первого элемента ИЛИ, входом третьего формирователя длительности, выход первого элемента ИЛИ соединен с входом обращения блока памяти, информационный вход-выход которого соединен с выходом четвертого элемента И и первым входом пятого элемента И, второй адресный вход устройства соединен с информационным входом второго счетчика, информационный выход которого прерывания при отладке программ по авт. св. ю соединен с адресным входом блока памяти, № 1185343, отличающееся тем, что, с целью установочный вход устройства соединен с расширения функциональных возможностей входом начальной установки второго счет- устройства за счет запоминания адресов пе- чика, выход прерывания устройства через реходов, в него введены блок памяти, последовательно соединенные элемент за- второй счетчик, первый и второй элементы держки и четвертый формирователь длитель- ИЛИ, первый и второй элементы НЕ, первый, 15 ности соединены с первым входом второго второй, третий и четвертый формирователиэлемента ИЛИ, выход третьего формироваФормула изобретения Устройство для формирования сигналов

длительности, элемент задержки, четвертый и пятый элементы И, причем вход строба адреса устройства соединен с входом пертеля длительности соединен с вторым входом второго элемента ИЛИ, выход которого соединен со счетным входом второго счетчика.

вого формирователя длительности, выход ко- „ вход признака записи устройства соединен с

Т Г Г ifcUI л

торого через первый элемент НЕ соединен с входом записи блока памяти и входом второго формирователя длительности, выход которого соединен с первым входом первого элемента ИЛИ, вход обращения

вторым входом пятого элемента И и через второй элемент НЕ с первым входом четвертого элемента И, адресный вход устройства соединен с вторым входом четвертого элемента И.

теля длительности соединен с вторым входом второго элемента ИЛИ, выход которого соединен со счетным входом второго счетчика.

I л

вторым входом пятого элемента И и через второй элемент НЕ с первым входом четвертого элемента И, адресный вход устройства соединен с вторым входом четвертого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования сигналов прерывания при отладке программ | 1986 |

|

SU1411755A2 |

| Устройство для формирования сигналов прерывания при отладке программ | 1986 |

|

SU1348841A1 |

| Устройство для формирования сигналов прерывания при отладке программ | 1986 |

|

SU1405061A2 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1425683A1 |

| Устройство для отладки программ | 1983 |

|

SU1290334A1 |

| Устройство отладки микропрограммных блоков | 1988 |

|

SU1541617A1 |

| Устройство для откладки программ | 1987 |

|

SU1474656A1 |

| Устройство для коррекции программ | 1983 |

|

SU1141416A1 |

Изобретение относится к цифровой вычислительной технике и предназначено для использования при отладке программ специализированных вычислительных систем 35 32 реального времени. Целью изобретения является расширение функциональных возможностей устройства за счет запоминания адресов переходов. Устройство содержит регистры 1, 4, 6, схемы сравнения 2, 3 и 9, элементы И 5, 11, 12, 29 и 30, мультиплексоры 7 и 10, счетчики 8 и 19, блок памяти 18, элементы ИЛИ 20-23. формирователи 24-27 и элемент задержки 28. Сущность изобретения заключается в том, что сформированный на основе анализа изменений адресной информации в магистрали сигнал перехода обеспечивает запись адреса перехода с адресного входа устройства в ячейку элемента памяти. При этом после записи адреса подготавливается следуюш,ая ячейка элемента памяти. 1 ил. Л 16 С S (Л 00 1чЭ СП 00 N3 ISJ

| Устройство для формирования сигналов прерывания при отладке программ | 1984 |

|

SU1185343A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-05-23—Публикация

1986-01-13—Подача