Изобретение относится к-вычислительной технике и может быть использовано при отладке программ специализированных цифровых вычислительных систем (СЦВС) реального времени.

Цель изобретения - расширение функциональных возможностей за счет автоматического, накопления статистической информации об отлаживаемой программе в процессе ее выполнения.

На фиг. 1 представлена блок-схема устройства для отладки программы; на фиг;. 2 - функциональная схема блока управления; на фиг. 3 - функциональная схема блока блокировки.

Устройство для отладки программ содержит (фиг. 1) первый блок 1 памяти., второй блок 2 памяти, третий блок 3 памяти, первый коммутатор 4, второй коммутатор 5, счетчик 6, блок 7 блокировки, блок 8 управления, ре- гистр 9, информационные входы-выходы устройства 10, входную 11 и адресную шину устройства, выходы 12 данных устройства, входы 13 данных устройст- ва, вход 14 синхронизации ввода устройства, вход 15 синхронизации вывода устройства, вход 16 разрешения выбора второго блока памяти устройства,вход 17 разрешения выбора третьего блока памяти устройства, вход 18 режима устройства, блок 19 начальной установки устройства, первый синхронизи рующий вход 20 устройства, второй синхронизирзтощий вход 21 устройства.

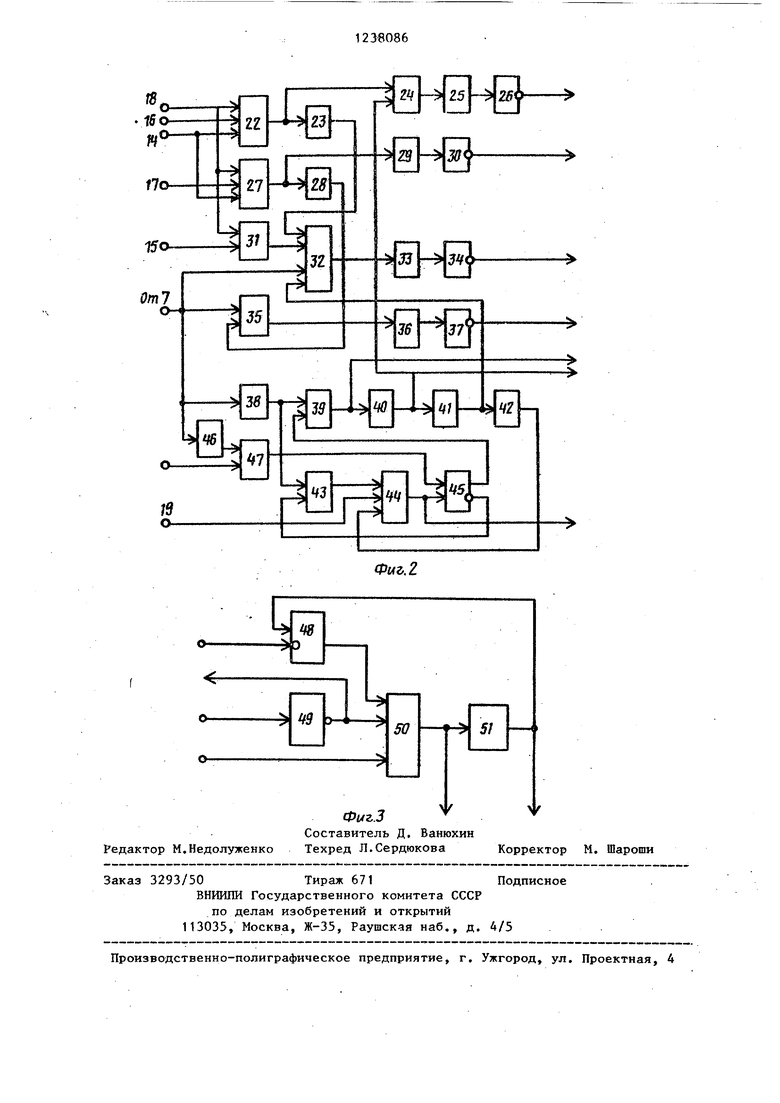

Блок 8 управления содержит (фиг.2) элемент И 22, элемент 23 задержки, элемент ИЛИ 24, формирователь длительности 25, 3|лемент НЕ 26, элемент И 27 элемёну 28 задержки, формирователь 29 длительности, элемент НЕ 30, элемент И 31, элемент ИЛИ 32, формирователь длительности 33, элемент НЕ 34, элемент ИЛИ 35, формирователь длительности 36, элемент НЕ 37, элемент за- держки 38, элемент И 39, элементы задержки 40-42, элемент И 43, элемент. ИЛИ 44, триггер 45, элемент 46 задержки, элемент И 47.

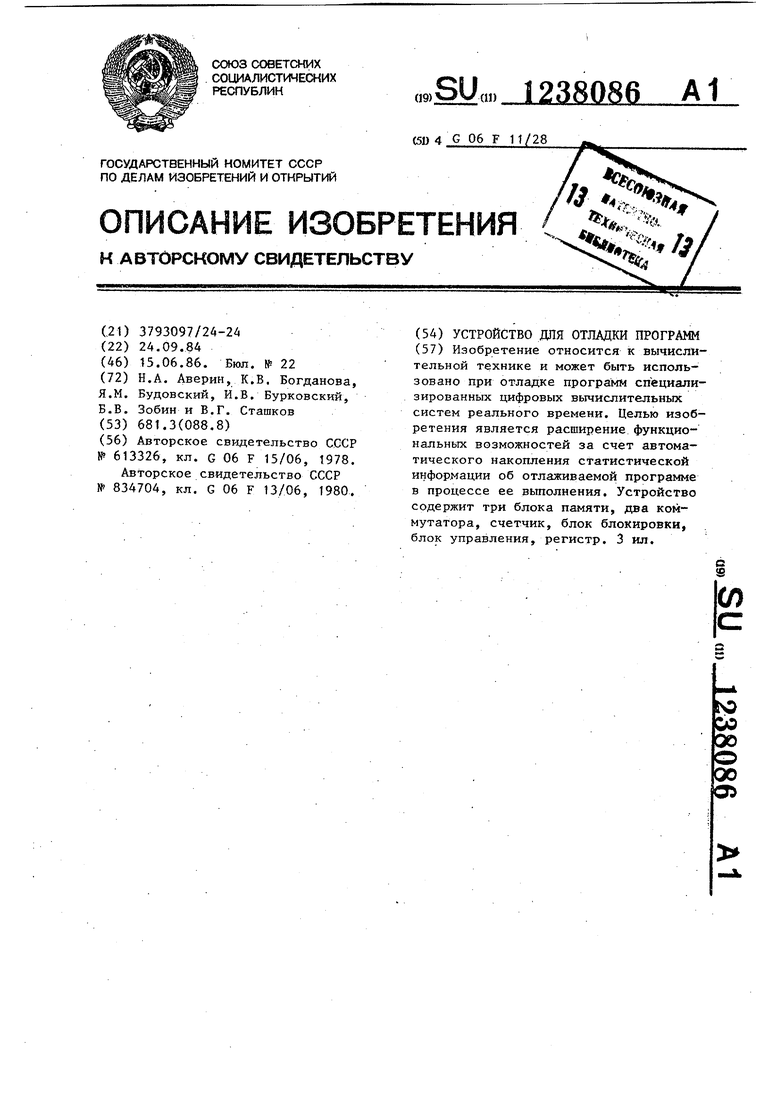

Блок 7 блокировки содержит (фиг.З) триггер 48, элемент НЕ 49, элемент И 50, элемент задержки 51.

В данном примере в качестве блока 1 памяти используется микропроцессорный модуль С.5-2113, представляющий собой ППЗУ с ультрафиолетовым стиранием информации. В качестве блоков памяти 2 и 3 используется микросхема

0

5

0

5 0 5

о j

5

541РУ2, причем блок 3 является одноразрядным. Мультиплексоры 4 и 5 выполнены на микросхемах 133 ЛР1, счетчик 6 - на микросхеме 133 ИЕ 7, триггеры 45 и 48 - на микросхемах 133 ТМ 2, элементы задержки 23, 28, 38, 40 - 42, 46, 51 и формирователи длительности 25, 29, 33, 36 - на микросхемах 133 АГ 3, остальные элементы являются стандартными и выполнены на микросхемах серии 133.

Первый блок памяти используется для хранения и считывания по сигналам из вычислительной машины команд отлаживаемой программы, второй блок памяти - для накопления статистической информации о программе в процессе ее выполнения, третий - для указания адресов команд, количество обраидений к которым необходимо подсчитывать. Регистр используется для приема из магистрали ЭВМ и хранения адреса команды на время, необходимое для работы второго и третьего блоков памяти,Запись исходной информации во BTopofi и третий блоки памяти осуществляется через первый коммутатор. При этом в третьем блоке памяти осзтцеств- ляется разметка адресов, а второй : блок памяти обнуляется. Второй коммутатор осуществляет коммутацию на адресные входы второго и третьего блоков памяти адреса, поступающего из универсальной ЭВМ при загрузке исходной информации и выводе результатов отладки, либо адреса с регистра в режиме отладки. Подсчет числа обращений к командам с помеченными адресами осуществляется с помощью счетчика. Блок блокировки обеспечивает блокировку обраш,ений к второму и третьему блокам памяти на время, необходимое для завершения в них текущих процессов.

Работа устройства рассмотрена на примере отладки программ СЦВС-, содержащей микроэвм Электроника-В , снабженной интерфейсом по ОСТ 11.305.

.903-80. Данное устройство эксплуатируется совместно с оборудованием

СЦВС и каким-либо оборудованием, обеспечивающим загрузку исходной информации в память устройства, а также вывод накопленной статистической информации на устройства наглядного отображения или документирования. Б дан.ном примере эти функции выполняет универсальная электронно-вычислительная машина (УЭВМ), состыкован

ная с данным устройством с помощью цепей сопряжения. Шины Ю, 20 и 21 подключаются к магистрали микроЭВМ, при этом 10 соединены с шинами адрес-дайные, вход 20 с ОБМ, а вход 21 - с шиной ДЧТ. Шины 11-19 подключены к устройству сопряжения УЭВМ. При этом через входы 11 поступает адрес, через шины 13 - данные, через вход 19 - сигнал начальной установки, через вход 18 - признак режима работы устройства, через вход 17 - признак выборки третьего блока памяти, через вход 16 - признак выборки второго блока памяти, че рез входь 14 и 15 - синхроимпульсы вводд и вывода информации соответственно. Через выходы 12 накопленные статистические данные выводятся из устройства в УЭВМ.

Работа по отладке программы начинается с загрузки памяти устройства. При этом в первый блок памяти заносится отлаживаемая программа. Способ фиксации программы зависит от физической реализации памяти. В данном примере первый блок памяти выполнен в виде:полупостоянного ЗУ, обеспечивающего подключение к магистрали по QCT 11.305.903-80. Запись информации в негр осуществляется с помощь nporpaivMaTopa при извлечении блока из состава дайногр устройства.

Устройство работает в двух режимах: режим I - режим обмена информации с режим II - режим отладки программ.

Режим работы устройства определяется уровнем сигнала, поступакщего на вход 18 устройс тва. При эток вы- сокий уровень сигнала соответствует режиму I, а низкий - режиму II. В ре жиме I в зависимости от поступления внешних сигналов может осуществляться ввод либо вывод информации,

После включения питания устройства на вход 19 начальной установки подают импульс положительной полярности, которьЕЙ через вход начальной установки и второй вход элемента 44 блока 8 поступает на нулевой вход триггера 45, а через третий выход блока 8 и третий вход блока 7 - на нулевой вход триггера 4В.

Загрузка исходной информацией второго и третьего блоко.в памяти осуществляется в режиме I следующим образом.

10

t5

238086 .4

Разрешающий потенциал (высокий уровень сигнала) поступает с входа 18 устройства на первые управляющие входы коммутаторов 4 и 5, через пер- 5 вый вход блока 7 - на вход элемента 49, а также через режимный вход блока 8 - на первые входы элементов 22, 27 и 31. Запрещающий потенциал (низкий уровень сигнала) формируется на втором входе элемента 50 через элемент 49 и через пе;рвь1й выход блока 7 - на вторых управлязющгос входах мутаторов 4 и 5. В этом режиме в ис ходком состоянии на входах t9, 17, 15,и 14 устройства подается потенциал низкого уровня.

В результате этого на выходах элементов 22, 27 и 31 блока 8 и втором и третьем выходах блока 7 имеем потенциал низкого уровня. На пятом и шестом выходах блока 8 формируется потенциал низкого уровня, а на первом, втором, третьем и седьмом выходах - потенциал высокого уровня.

20

Для записи информации в блок 2с входа 16 устройства подают разрешающий потенциал выбора блока 2 памяти, который через вход выбора втораго блока памяти блока 8 поступает на второй вход элемента 22 н с вхояа 14 устройства - импульс положительной по- Полярности, который через первый синхронизирующий вход блока 8 поступает на третьи входы элементов 22 и 27 я проходит через элемент 22,. на первом входе которого разрешающий потенциал-, обусловлен режимом обмена информацией с УЭВМ, Элемент 27 закрыт по второму входу запрещающим потенциалом выбора блока 3 памяти с входа 17 устройстве через вход выбора третьего блока памяти блока 8. Сигнал с выхода элемента 22 формируется На элементе 25, через первый вход элемента 24 инвер - тируется элементом 26 и через выход блока 8 поступает на вход режима запись - чтение блока 2 в виде отрицательного импульса, что сбответ- : ствует режиму записи информации В блок 2. Кроме того, сигнал с вьжода . элемента 22 через элемент 23 задержки, параметр которого учитывает время установки режима на входе блока 2 йа- мятй, а также через четвертый вход элемента 32, формирователь 33, инвертор 34 и тестой блока 8 поступает в виде отрицательного импульса на разрешакяцнй вход блока 2, осзоцествляя в нем запись информации, котора поступает на его информационные вхо- .ды с входов 13 устройства через вторые информационные входы коммутатора 4. Запись производится по адресу, сформированному на входах 11 устройства и поступающему в блок 2 через первые информационные входы коммутатора 5, поскольку на первьпс управля- ющих входах коммутаторов 4 и 5 имеется разрешающий потенциал в режиме 1, Формирование на входах 13 д улевой информции и перебор кодов адреса на входах 11 обеспечивает обнуление бло- ка 2. .

Загрузка данных в блок 3 производится аналогичным образом при поступ- ленин синхроимпульса на вход 14 устройства и разрешающего потенциала на вход 17, поступающего через вход выбора третьего блока памяти блока 8 на второй вход элемента 27. Импульс с входа 14 устройства проходит через первый синхронизирующий вход, бло- .ка 8, третий вход элемента 27, на первом входе которого имеется разрешающий потенциал, обусловленный режимом обмена информацией с УЭВМ. Далее этот импульс проходит через фор- мироватёлЬ 29, элемент НЕ 30, второй выход блока 8 на вход режима запись - чтение блока 3 в виде отрицательного импульса, устанавливая в блоке 3 памяти режим записи,Кроме того,сигнал с выхода элемента 27 проходит через элемент задержки 28, второй вход, элемента 35, с выхода которого сформированный по длительности на элементе 36 и инвертированный на элементе

37 он поступает в виде отрицательного импульса через третий рыход блока 8 на второй управляющий вход блока 3 памяти, инициируя операцию записи ин- фЪрмации. При этом на адр.есные и информационные входы блбка 3 информация- поступает с входов 11 и 13 соответст- .венно,

В режиме II, соответствующем низкому уровню потенциала на входе 18 устройства, осуществляется накопление ста.тистической информации об отлаживаемой программе. При этом используются положительные синхроим- пул&сы ОБМ, поступающие из мнкроЭВМ на вход 20 устройства. В процессе выполнения отлаживаемой программы составляющие ее командь считьшаются в

5 10 5

20 5 Q .„

0 5

5

5

магистраль Э.ВМ из блока 1 через входы-выходы 10. По сигналу ОБМ в блок принимается код адреса, формируемый микроэвм на шинах 10 устройства. На вторьгх управляющих входах коммутаторов 4 и 5, а также втором входе элемента 50 имеется разрешающ1С1 потенциал через первый вход блока 7 и элемент 49 с входа 18 устройства. Синхроимпульс с входа 20 устройства через второй вход блока 7 поступает на первый вход элемента 50, на третьем входе которого присутствует разрешающий потенциал с нулевого выхода триггера 48, находящегося в обнуленном состоянии, на втором входе - разрешающий потенциал, определяемый состоянием режимного сигнала на первом входе блока 7 (низкий уровень). Сигнал с выхода элемента 50 через второй

выход блока 7 поступает на вход син- I

хронизации регистра 9 и фиксирует в нем состояние входов 10 устройства, на которых в этот момент присутствует код адреса. Этот же сигнал, задержанный на элементе 51 на время, необходимое для установки адреса в ре- .гистре 9, поступает на вход установки триггера 48 в единичное состояние, которое запрещает прохождение, синхросигнала с второго входа блока 7 через его элемент 50, Кроме того, положительный сигнал с вьмода элемента 51 через третий выход блока 7, второй синхронизирующий вход блока 8, второй вход элемента 32 формируется и инвертируется на элементах 33 и 34 соответственно и через седьмой выход блока 8 8 поступает на резрейающйй вход блока 2 в виде отрицательного импульса.За счет Низкого уровня потенциала на сходе режима блока 8 и выходе элемента 40 н а первом выходе блока В присутствует потенциал высокого уровня через элементы 24, 25 и 26, что .определяет режим считывания информации из блока 2. Одновременно сигнал с второго синхронизирующего входа блока 8 проходит через первый вход элемента 35-, формируясь по длительности на элементе 36, и через элемент НЕ 37 н. третий выход блока 8 поступает в виде отрицательного импульса на разрешающий вход блока 3 памяти. Благодаря низкому уровню потенциала. на режимном входе блока 8 на вькоде элемента 29 также потенциал низкого

уровня, а на втором выходе данного блока - высокий уровень .потенциала через элемент НЕ 30, что соответствует режиму считывания информации из .блока памяти 3. Указанное считывание из блоков 2 и 3 происходит по адресу, фиксированному в регистре 9, поступающему на адресные входы блоков 2 и 3.через вторые информацион- ные входы коммутатора 5, у которого на втором управляющем вход разрещаю- щий потенциал, а на первом управляющем входе - запрещающий. Информация, считанная из блока 3 поступает на второй вход элемента 47. Если из блока 3 считан сигнал t (высокий уровень) , то через элемент 47 разрешено прохождение импульса с второго синхронизирующего входа блока 8, задер- жанного на элементе 46 с учетом считывания информации из блока 3. Триггер 45 устанавливается в состояние 1. Сигнал с второго синхронизирующего входа, задержанный на элементе

38на время установки триггера 45 поступает на первые входы элементов

39и 43. При указанном состоянии . триггера 45 элемент 43 закрыт по второму входу, а элемент 39 по второму входу открыт. Пройдя через элемент

39 и шестой выход блока 8 на управляющий вход счетчика 6, сигнап с второго синхронизирующего входа блока 8 зафиксирует в счетчике .6 информацию, считанную из блока памяти 2. Этот же сигнал после некоторой задержки на элементе 40, определяемой временем установки информации в счетчике 6, через пятый выход блока 8 и считанный вход счётчика 6 увеличивае его содержимое на единицу, а также, проходя через второй вход элемента 24, формируется по длительности на элементе 25 и инвертируется на элементе 26, задавая на соответствую- щее время режим записи блоку 2 (низкий уровень сигнала на его входе режима запись - чтение). С выхода элемента 40 сигнал проходит также через третий вход элемента 32, формирова- тель 33 на седьмой выход блока 8,задерживаясь на элементе 41 на время, необходимое для установки режима записи в блоке 2. В результате этого в блок памяти 2 по текущему адресу записана информация, увеличенная на единицу. После окончания процессов записи, длительность которых учитыва

ю 15 20 25

о

5

5

0

ется элементом задержки 42, через третий вход элемента 44 сброшены триггеры 45 и 48. Начиная с этого момента, второй вход блока 7 разблокирован для сигналов с входа 20 устройства. Если из блока памяти 3 считана нулевая информация, то триггер 45 остается в исходном состоянии и элемент 43 до второму входу открыт, а элемент 39 по второму входу закрыт. В результате сигнал с выхода элемента 43 пройдет через первый вход элемента 44 и через четвертый выход блока 8 и третий вход блока 7 обнулит триггер 48, после чего разрешен прием следз ощего синхросигнала с входа 20 устройства в блок 7.

Формирование-сигналов ОБМ осуществляется микроэвм по результатам обработки очередной команды программы, считываемой из блока 1 по сигналу ДЧТ,; поступающему из микрбЭВМ на вход 21 устройства. При этом считывание формации из блока 1 осуществляется независимо от работы цепей блокирозв- ки устройства. :

После накопления статистической информации в режиме I (на входе режима блока 8 потенциал высокого уровня) осуществляют ее вывод в универсальную машину через выходы 12 устройства. Для этого на вход синхронизации вывода 15 устройства подают положительный импульс, который через третий синхронизирующий вход блока 8, второй вход элемента 31, открытого по первому входу режимным сигналомj первый вход элемента 32 и седьмой выход блока 8 поступает отрицательным импульсом на разрешающий вход блока 2. Поскольку на первом выходе блока 8 сох- сохраняется потенциал высокого уровня, происходит считывание информации, из блока 2 по адресу на входах 11 устройства. Считанная информация поступает на выходы 12 устройства. Осуществляя указанные действия с подачей различных кодов на входы 11 устройства, производят считывание информации со всего массива памяти блока 2 либо его части. При этом паМять 3 находится в режиме хранения информации., .

Формул аиз о б ре те и ия

Устройство для отладки программ, содержащее первьй и второй блоки памяти, блок управления, регистр и первый коммутатор, выходы которого связаны через двунаправленную тину данных с информационными входг1ми-вы- ходами второго блока памяти причем информационные.входы-выходы первого блока памяти подключены к информа- ционньм входам-выходам устройства, первый вход синхронизации блока управления является входом синхронизации ввода устройства, первый выход блока управления соединен с входом режима запись - чтение второго блока памяти, о т л и ч а к щ е е с я тем, что, с целью расцшрения функциональных возможностей устройства за счет .автоматического накопления статистической информации об отлаживаемой программе в процессе ее выпол- нения, оно дополнительно содержит третий блок памяти, второй 1коммута тор, счетчик и блок блокировки, причем первая группа информационных входов второго коммутатора соеданена с входной адресной шиной устройства, вторая группа информационных входов соединена с группой выходов регистра, группа информационных входов которого соединена с информационными входами-выходами устройства, а выход второго коммутатора соединены с адресными входами второго и третьего блоков ламяти, вход режима, запись - чтение третьего блока памяти соедине с вторым выходом блока управления, а разрешающий вход - с третьим выходом блока управления, третий вход синхронизации блока управления является входрм синхронизации вывода устройства, выходы первого коммутатора соединены с выходами данных устройства и с информационными входами счетчшса, выходы которого соединены с первой группой информационных входов первого коммутатора, а его вторая группа информационньпс входов с входами данных устройства, через двунаправленную шину данных - с ин- фо1Я 1ационнь(ми 1входами-выходами третьего блока памяти и разрешаю1цим входом блока управления, режимный вход

блока управления соединен с первьм входом блока блокировки и первыми управляющими входами .первого и второго коммутаторов и является входом режима устройства, вторые управляю- «

щие входы первого и второго коммутаторов соединены с первым выходом блс ка блокировки, второй выход которого соединен с входом синхронизации регистра, третий выход блока блокировки соединен с вторым входом сии- хроиизадага блока управления, второй вход блока блокировки соединен с первым синхронизирующим входом устройства и разрешающим входом первого блока памяти, а третий вход блока блокировки соединен с четвертым выходом блока управления, вход разрешения выбора второго блока памяти которого является входом разрешения выбора второго блока памяти устройства, вход разрешения выбора третьего блока памя.ти блока управления является входом разрешения выбора третьего блока памяти устройства, вход начальной установки блока управления соединен с входом начальной установки устройства, а пятый, шестой и седьмой выходы блока управления соединены со счетным входом счетчика, входом синхронизации счетчиКа и: ifraa- решающим входом второго блока памяти -соответственно, причем вход чтения первого блока памяти соединен .с вторым синхронизирующим входом устройства, при этом блок блокировки содержит триггер, элемент НЕ, элемент И и элемент задержки, причем первый, второй и третий входы блока блокировки соединены соответственно с входом элемента НЕ, первым входом элемента И и нулевым входом триггера, единичный вход которого соединен с третьим выходом блока блокировки И с выходом элемента задержки, вход которого соединен с вторым выходом блока блокировки и выходом элемента И, второй вход которого соединен с первым выходом блока блокировки и выходом элемента НЕ, а третий вход - с выходом тригге{ а, при этом блок управления содержит шесть элементов И, четыре элемента ИЛИ, четыре элемента НЕ, семь элементов задержки, четыре формирователя длительности и триггер, причем режимный вход блока Управления, вход разрешения выбора второго блока памяти блок управления и первый вход синхронизации блока управления соединены соответственно с первым, вторым и третьим входами первого элемента И, выход которого соединен с входом первого элемента задержки и с первым входом

первого элемента ИЛИ, выход которого соединен с входом первого формирователя длительности, выход которо- го соединен с входом первого элемента НЕ, выход которого соединен с первым выходом блока управления, первый, второй и третий входы второго элемента И соединены соответственно с режимным входом блока управления, входом разрешения выбора третьего блока памяти блока управления, первым входом синхронизации блоки управления, а выход соединен с входом второго элемента задеряжи и входом второго формирователя длительности,выход которого через второй элемент НЕ соединен с вторым вь1ходом блока управления, первый и второй входы третьего элемента И соединены соответственно с режимньтм входом блока управления и с третьим входом синхронизации блока управления, а выход соединен с первым входом второго элемента ИЛИ, выход которого соединен с входом третьего формирователя длительности, выход которого через третий элемент НЕ соединен с седьмым выходом блока управления, четвертый вход второго элемента ИЛИ соединен с выходом первого элемента задержки, второй вход синхронизации блока управления соединен с вторым входом второго элемента ИЛИ, первый входом третьего элемента ИЛИ, с входом третьего элемента задержки и с входом седьмого элемента задержки, второй вход треть21 го

0

5

5

0

0

его элемента ИЛИ соединен с выходом второго элемента задержки, а выход - с входом четвертого формирователя длительности, выход которого через четвертый элемент НЕ соединен с третьим выходом блока управления,выход третьего элемента задержки соединен с первым входом шестого элемента И и с первым входом четвертого элемента И, выход которого соединен с шестым выходом блока управления и с входом четвертого элемента задержки, выход которого соединен с вторым входом первого элемента ИЛИ, пятым выходом блока управления и с входом пятого элемента задержки, выход которого соединен с третьим входом второго элемента ИЖ и с входом шестого элемента задержки, выход которого соединен с третьим входом четвертого элемента ИЛИ, первый и второй входы пятого элемента И соединены соответственно с выходом седьмого элемента задержки и разрешающим входом блока управления, а выход - с единичным входом триггера, прямой выход которого соединен с вторым входом четвертого элемента И, а инверсный выход - с вторьм входом шестого элемента И, выход которого соединен с первым входом четвертого элемента ИЛИ, второй вход которого подключен к входу начальной установки блока управления, а выход соединен с нулевым входом триггера и с четвертым выходом блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1983 |

|

SU1104521A1 |

| Устройство для отладки программ | 1984 |

|

SU1166122A1 |

| Устройство для отладки программно-аппаратных блоков | 1983 |

|

SU1242965A1 |

| Устройство для отладки программ | 1988 |

|

SU1624461A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1315984A1 |

| Устройство для отладки микропроцессорных систем | 1986 |

|

SU1462326A1 |

| Устройство для модификации адреса зон памяти при отладке программ | 1987 |

|

SU1465887A1 |

| Устройство для отладки программ | 1986 |

|

SU1410038A1 |

| Устройство для отладки программ | 1985 |

|

SU1251087A1 |

Изобретение относится к вычислительной технике и может быть использовано при отладке программ специализированных цифровых вычислительных систем реального времени. Целью изобретения является расширение функциональных возможностей за счет автоматического накопления статистической информации об отлаживаемой программе в процессе ее выполнения. Устройство содержит три блока памяти, два коммутатора, счетчик, блок блокировки, блок управления, регистр. 3 нп.

| Устройство для обработки цифровых данных | 1976 |

|

SU613326A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для управления памятью | 1979 |

|

SU834704A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-15—Публикация

1984-09-24—Подача