1

СП

О)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство адресации памяти | 1989 |

|

SU1689956A1 |

| Устройство для адресации памяти | 1990 |

|

SU1741142A1 |

| Микропроцессор | 1985 |

|

SU1330634A1 |

| Устройство для синтаксического контроля программ микропроцессорной системы | 1985 |

|

SU1260960A1 |

| Устройство для сопряжения ЦВМ и накопителя информации | 1985 |

|

SU1265780A1 |

| Запоминающее устройство с произвольной выборкой | 1988 |

|

SU1548790A1 |

| Микропроцессор для вводавывода данных | 1976 |

|

SU618733A1 |

| Комбинированный канал | 1986 |

|

SU1405067A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1985 |

|

SU1307462A1 |

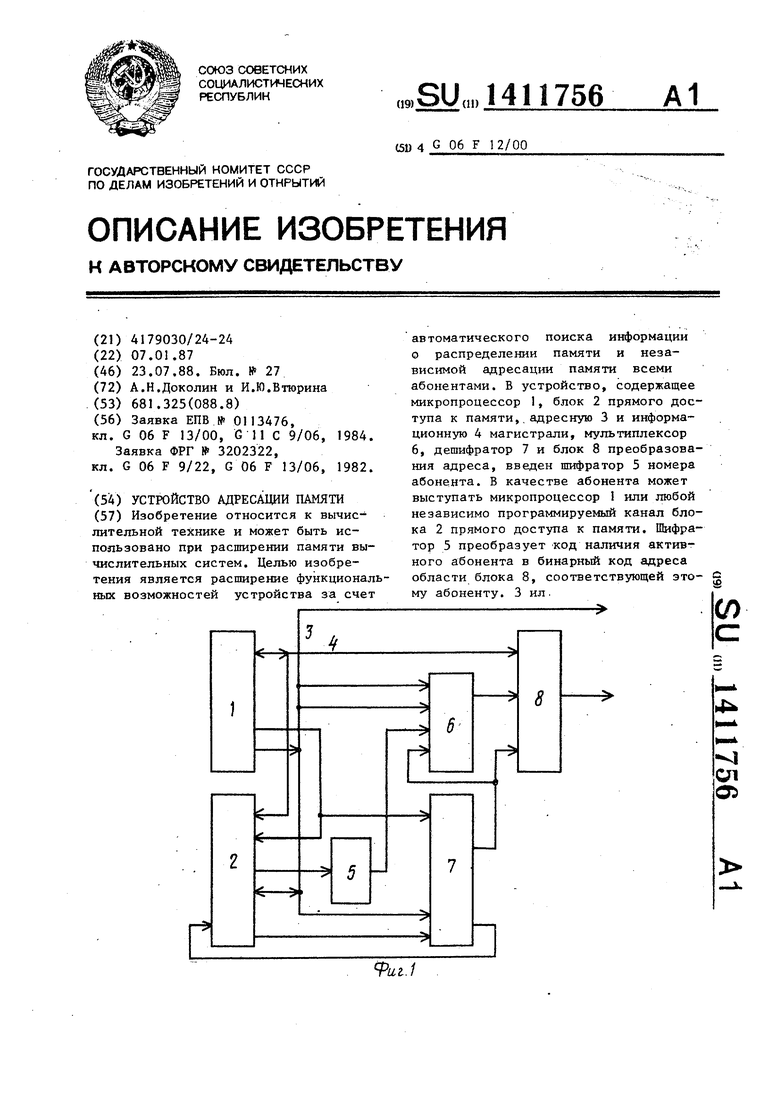

Изобретение относится к вычислительной технике и может быть использовано при расширении памяти вычислительных систем. Целью изобретения является расширение функциональных возможностей устройства за счет автоматического поиска информации о распределении памяти и независимой адресации памяти всеми абонентами. В устройство, содержащее микропроцессор 1, блок 2 прямого доступа к памяти,, адресную 3 и информационную 4 магистрали, мультиплексор 6, дешифратор 7 и блок 8 преобразования адреса, введен шифратор 5 номера абонента. В качестве абонента может выступать микропроцессор 1 или любой независимо программируемый канал блока 2 прямого доступа к памяти. Шифратор 5 преобразует код наличия активного абонента в бинарный код адреса области блока 8, соответствующей это- с му абоненту. 3 ил. (Л

%г./

Изобретение относится к вычислительной технике и может быть использовано при расширении памяти вычислительных систем.

Цель изобретения - расширение функциональных возможностей устройства за счет автоматического поиска информации о распределении памяти и независимой адресации памяти всеми абонентами.

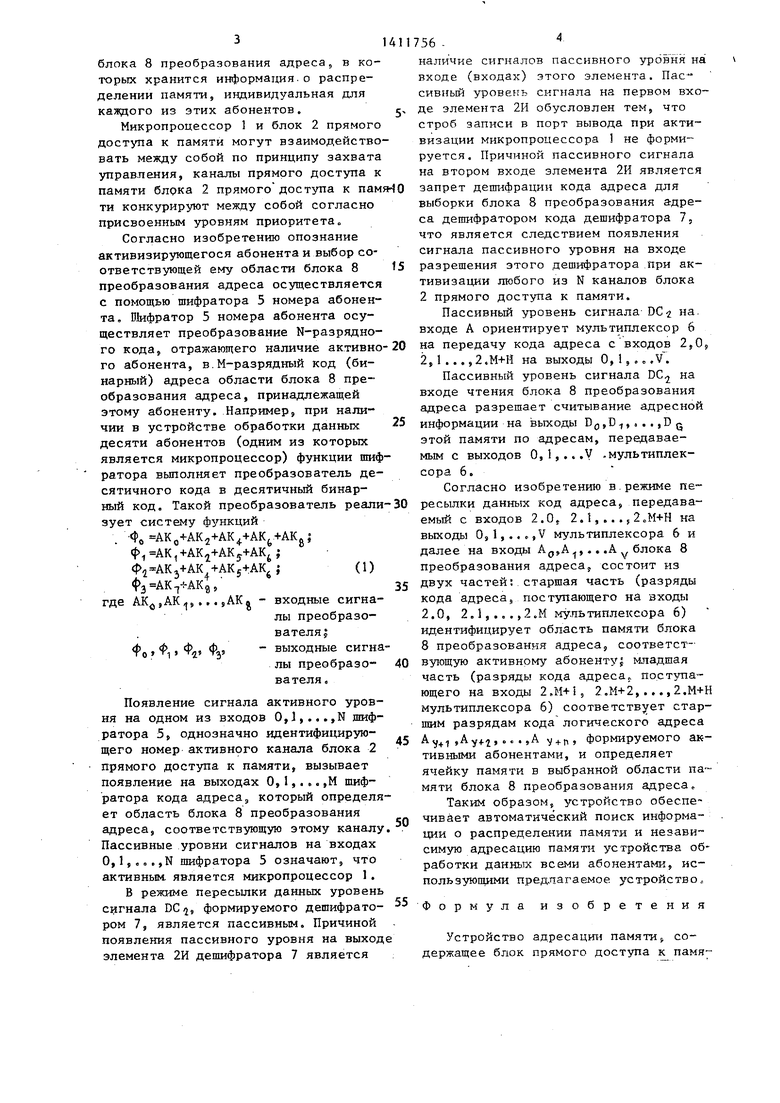

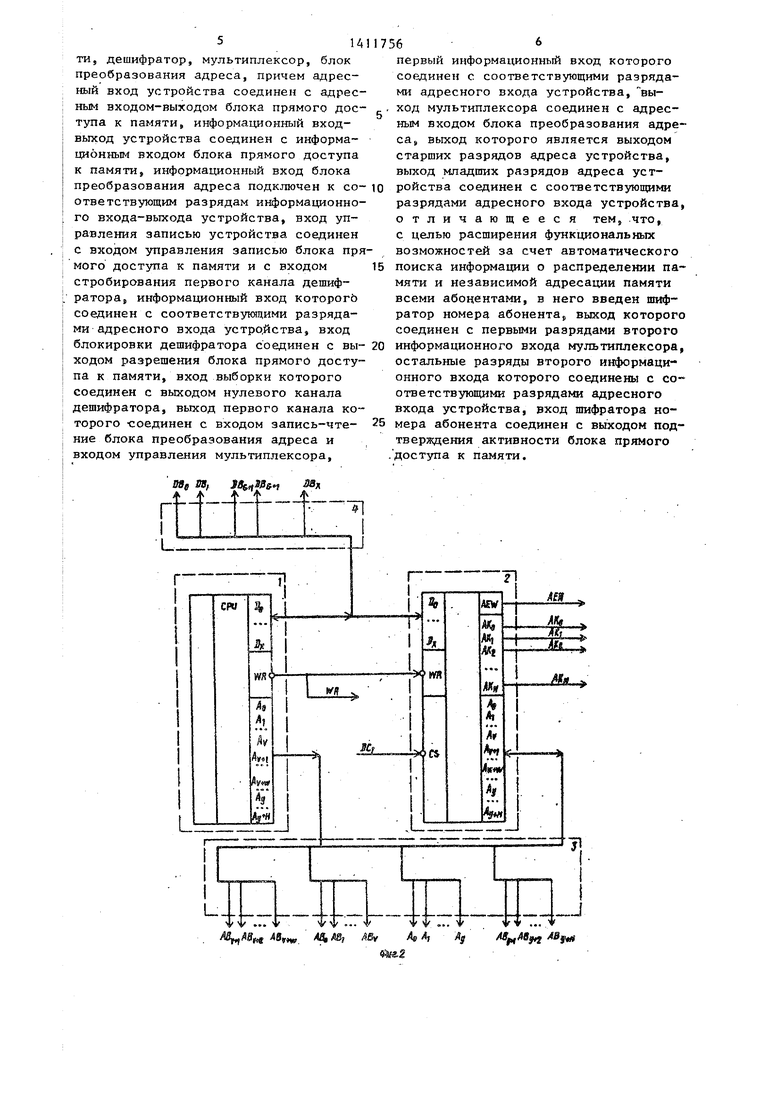

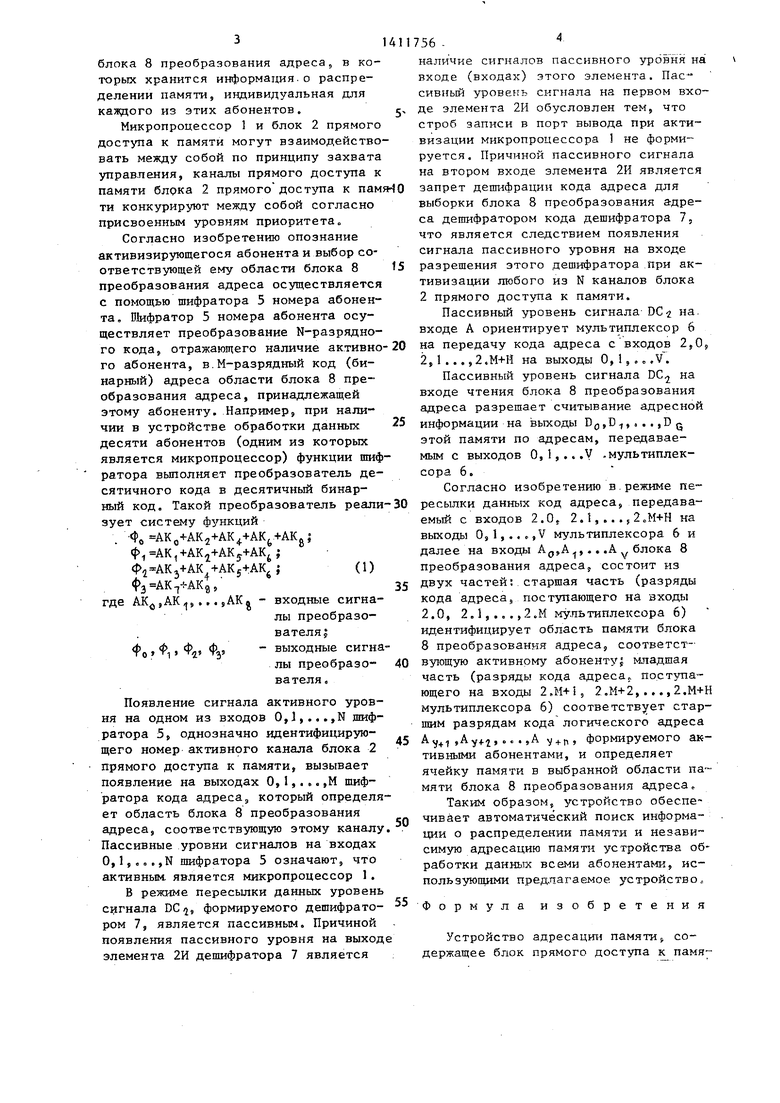

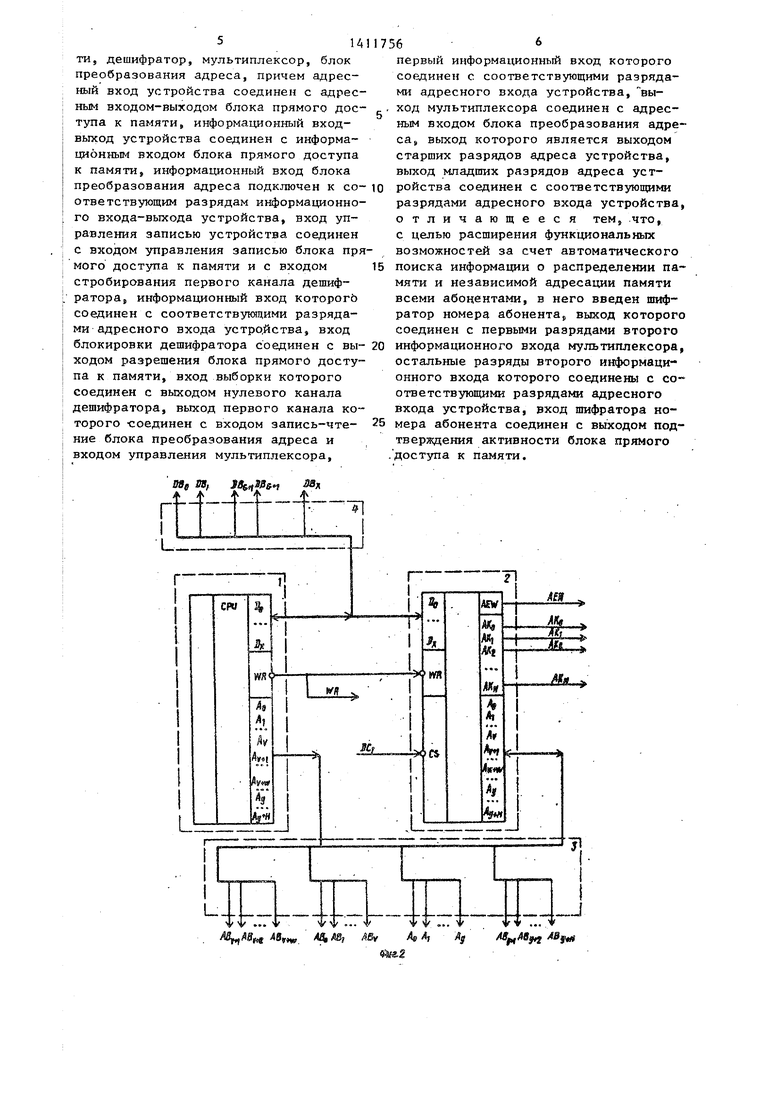

На фиг.1 приведена функциональная схема, устройства адресации памяти; на фиг,2 и 3 - распределение адресных и информационных линий связи устройства адресации памяти

Устройство содержит микропроцессор 15 блок 2 прямого доступа к памяти, адресную 3 и информационную 4 ма- гистрали5 шифратор 5 номера абонента5 мультиплексор 6, дешифратор 7 и блок 8 преобразования адреса.

Устройство работает следующим образом,

В резкиме программирования микропроцессор 1 заносит во внутренние регистры блока 2 прямого доступа к памяти индивидуальную для каждого из каналов этого блока информаи ию, Эта информация определяет начальнь й ап- рес-з по которому осуществляется п.е ресылка данных, объем пересылаемого массива данных (количество циклов пе ресьшки)J режим работы и уровень приоритета канала. Благодаря индивидуальной программной настройке каналов блока 2 прямого доступа к памяти каж- дьш из этих каналов является самостоятельным абонентом и может претендовать на независимое распределение памяти,

Запись данных с входов ,,.,., Dy. во внутренние регистры блока 2 прямого доступа к памяти (фиг,2) осу- ш;ествляется по стробу записи, посту- паюш,ему на вход записи этого блока, при наличии активного уровня сигнала DC на входе CS Адресg который поступает на входы A(j3 А 5 , о, s ./ блока 2 прямого доступа к памяти, не требует преобразования и является физическим адресом внутренних регистров блок а,

Согласно изобретению блок 8 преобразования адреса осуществляет хранение индивидуальной для кажд,ого из абонентов (микропроцессора 1 или каналов блока 2 прямого доступа к памяти) информации о распределении памя

117562

ти, Изменение этой информации может осуществлять микропроцессор 1 в режиме программирования, В этом режиме

все ячейки блока 8 преобразования адреса рассматриваются как порты вывода.

Запись данных с входов Dg,D,,,,, Dg в ячейки (порты вывода) блока ,8

10 преобразования адреса (фиг,3) осуществляется .по адресам, определяемым кодом на входах AQ, А,,,,,А, при наличии сигнала активного уровня ВС„ на входе, В режиме программирования

15 код адреса на входах А, А,...,Ау блока 8 является физическим„

Условием возникновения активного уровня сигнала DC-2 на выходе элемента 2И дешифратора 7 является наличие

20 строба записи на первом входе этого элемента и сигнала активного уровня, поступающего с выхода 1 дешифратора кода DC дешифратора 7, на втором его входе, Активный сигнал на выходе 1

25 дешифратора кода DC дешифратора 7 появляется в случае, если на входах 1,2,,,,,W этого дешифратора присутствует код адреса для выборки блока 8 преобразования ад,реса, а на входе

30 EN-активный уровень сигнала разрешения, поступаюшего с выхода блока 2 прямого доступа к памяти. Сигнал разрешения является активным в режиме программирования и приобретает пас35 сивный уровень при активизации любого канала блока 2 прямого доступа к памяти.

При наличии активного уровня сигнала DC -на входе А мультиплексора 6

40 (фиг.З) последний ориентирован на передачу кода адреса ячейки (порта вьгоода) блока 8 преобразования адреса с входов 1.0, 1 о 1J ..,,1,V на выходы О,I,...,V.

45 Шина 3 адреса является общей для микропроцессора 1 и блока 2 прямого доступа к памяти, который содержит N каналов. По этой-шине в режиме пересылки данных осзществляется переда20 ча логического адреса памяти устройства обработки данных. Независимость адресации памяти устройства обработки данных в этом режиме достигается благодаря тому, что каждый и:з або55 нентов (микропроцессор 1 ил1. каналы блока 2 прямого доступа к памяти) при формировании физического адреса памяти устройства обработки данных обра- . щается к собственньП областям памяти

3

блока 8 преобразования адреса, в которых хранится информация.о распределении памяти, индивидуальная для каждого из этих абонентов.

Микропроцессор 1 и блок 2 прямого доступа к памяти могут взаимодействовать между собой по принципу захвата управления, каналы прямого доступа к памяти блока 2 прямого дост ша к пам ти конкурируют между собой согласно присвоенным уровням приоритета.

Согласно изобретению опознание активизирующегося абонента и выбор соответствующей ему области блока 8 преобразования адреса осуществляется с помощью шифратора 5 номера абонента, В1ифратор 5 номера абонента осуществляет преобразование N-разрядно- го кода, отражающего наличие активно го абонента, в.М-разрядный код (бинарный) адреса области блока В преобразования адреса, принадлежащей этому абоненту. Например, при наличии в устройстве обработки данных десяти абонентов (одним из которых является микропроцессор) функции шифратора выполняет преобразователь десятичного кода в десятичный бинарный код. Такой преобразователь реали зует систему функций

. -(fo AKo-f-AK2+AK +AK +AKg|

АК, ч-АК +АКу+АК }

Ф -АКз+АК +АК5+АК ; (1)

Фз АКт -АКа/

где .,.jAK. - входные сигналы преобразователя;

о 1 у выходные сигналы преобразо вателя.

Появление сигнала активного уровня на одном из входов 0,J1,.,.,N шифратора 5j однозначно идентифицирующего номер активного канала блока 2 прямого доступа к памяти, вызывает появление на выходах О,1,.,.,М шифратора кода адресаэ который определяет область блока 8 преобразования адреса, соответствующую этому каналу Пассивные уровни сигналов на входах О,l5,..,N шифратора 5 означают, что активным, является микропроцессор 1 .

В режиме пересылки данных уровень сигнала DC;, формируемого дешифрато- ром 7, является пассивным. Причиной появления пассивного уровня на выход элемента 2И дешифратора 7 является

4

,

О

5 0 5 0

5

0

5

0

наличие сигналов пассивного уровня на входе (входах) этого элемента. Пассивный уровень сигнала на первом входе элемента 2И обусловлен тем, что строб записи в порт вывода при активизации микропроцессора 1 не формируется. Причиной пассивного сигнала на втором входе элемента 2И является запрет дешифрации кода адреса для выборки блока 8 преобразования адреса дешифратором кода дешифратора 7, что является следствием появления сигнала пассивного уровня на входе разрешения этого дешифратора при активизации любого из N каналов блока 2 прямого доступа к памяти.

Пассивный уровень сигнала DCi на. входе А ориентирует мультиплексор 6 на передачу кода адреса с входов 2,0, 2j, 1 ... ,2.М+Н на выходы 0,1,.,,V.

Пассивный уровень сигнала DC на входе чтения блока 8 преобразования адреса разрешает считывание адресной информации на выходы D(,,D, . . . ,D Q этой памяти по адресам, передаваемым с выходов О,1,.. .у .мультиплексора 6.

Согласно изобретению в режиме пересылки данных код адреса, передаваемый с входов 2.0 2.i,...S2„М+Н на выходы Ojl,.,.,V мультиплексора 6 и далее на входы Ад,А,.,.А блока 8 преобразования адреса, состоит из двух частей; старшая часть (разряды кода адреса5 поступающего на входы 2.0, 2,1,...,2.М му.пьтиплексора 6) идентифицирует область памяти блока 8 преобразования адреса, соответствующую активному абоненту младшая часть (разряды кода адреса поступающего на входы 2,М+55 2,М+2,...,2.М+Н мультиплексора 6) соответствует старшим разрядам кода логического адреса AV,, ,Ау, о. . ,А v + n формируемого активными абонентами, и определяет ячейку памяти в выбранной области памяти блока 8 преобразования адреса.

Таким образом, устройство обеспе чивает автоматический поиск информации о распределении памяти и независимую адресацию памяти устройства обработки данных всеми абонентами, использующими пред.пагаемое. ус тройство,

Формула изобретения

Устройство адресации памяти, содержащее блок прямого доступа к памя™

514

ти, дешифратор, мультиплексор, блок преобразования адреса, причем адресный вход устройства соединен с адресным входом-выходом блока прямого доступа к памяти, информационный вход- выход устройства соединен с информационным входом блока прямого доступа к памяти, информационный вход блока преобразования адреса подключен к соответствующим разрядам информационного входа-выхода устройства, вход управления записью устройства соединен с входом управления записью блока прямого доступа к памяти и с входом стробирования первого канала дешифратора, информационный вход которогЬ соединен с соответствукяцими разрядами адресного входа устройства, вход блокировки дешифратора соединен с выходом разрешения блока прямого доступа к памяти, вход выборки которого соединен с выходом нулевого канала дешифратора, выход первого канала которого соединен с входом запись-чтение блока преобразования адреса и входом управления мультиплексора.

MS щ лзл

АВ, №,

17566

первый информационный вход которого соединен с соответствующими разрядами адресного входа устройства, выg . ход мультиплексора соединен с адресным входом блока преобразования адреса вьпсод которого является выходом старших разрядов адреса устройства, выход младших разрядов адреса уст0 ройства соединен с соответствующими разрядами адресного входа устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет автоматического

15 поиска информации о распределении памяти и независимой адресации памяти всеми абонентами, в него введен шифратор номера абонента, выход которого соединен с первыми разрядами второго

0 информационного входа мультиплексора, остальные разряды второго информационного входа которого соединены с со ответствующими разрядами адресного входа устройства, вход шифратора нс5 мера абонента соединен с выходом подтверждения активности блока прямого . доступа к памяти.

АЗ Ву

Г

Т|

| Припой медно-цинковый | 1957 |

|

SU113476A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Заявка ФРГ № 3202322, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-07-23—Публикация

1987-01-07—Подача