11 t

мГ

Изобретение относится к автоматике и вычислительной технике и предназначено для вычисления систем булевых функций.

Цель изобретения - сокращение аппаратурных затрат.

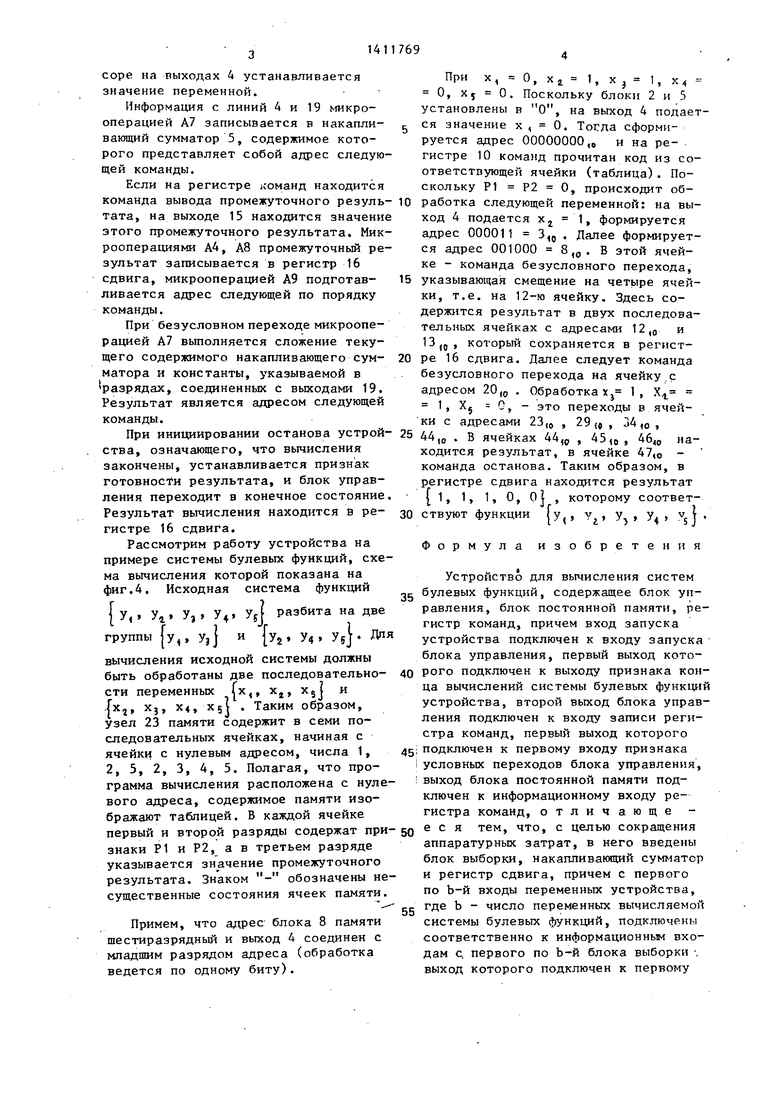

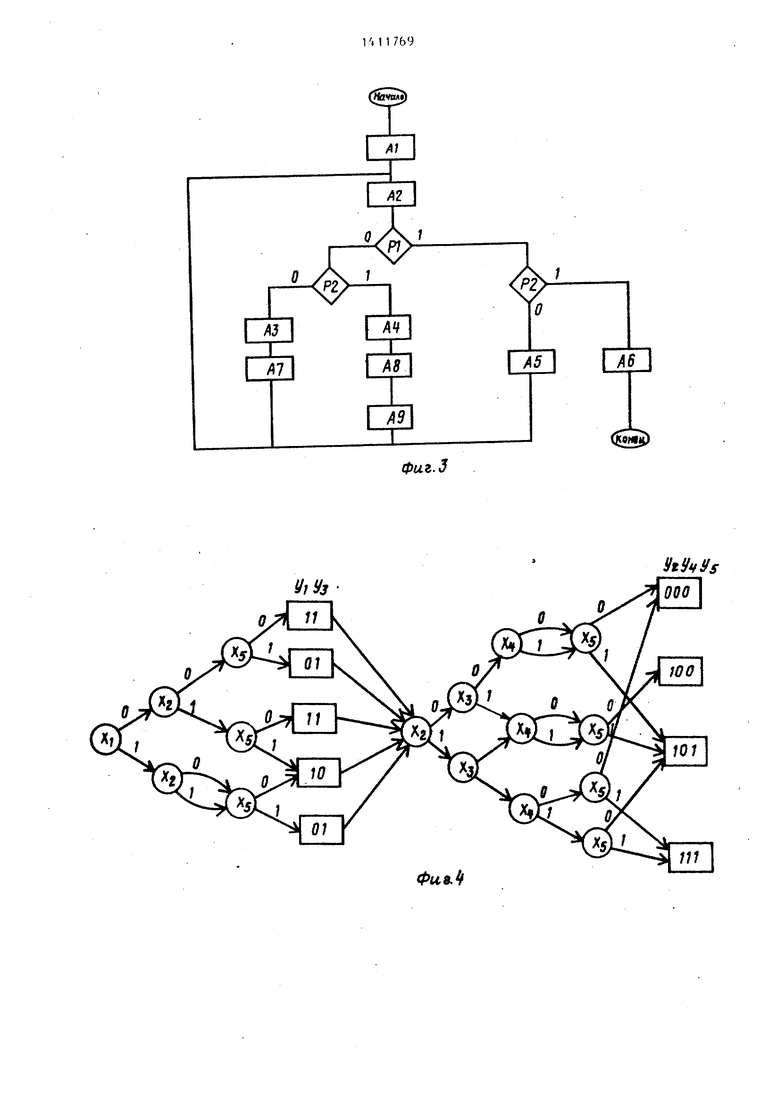

На фиг.1 изображена схема устройства; на фиг.2 - схема блока выбоки; на фиг.З - схема алгоритма работ блока управления; на фиг.4 - схема вычисления системы булевых функций. Устройство содержит с первого по Ь-й входы переменных вычисляемой системы булевых функций, блок 2 выбор- ки, информационные входы 3 блока выборки, выход 4 блока выборки, накапливающий сумматор 5, управляющий вхо 6 накапливающего сумматора, выход 7 накапливающего сумматора, блок 8 по- стоянной памяти, выход 9 блока постоянной памяти, регистр 10 команд, первый 11 и второй 12 выходы регистра команд, блок 13 управления, вход 14 записи регистра команд, третий вы ход 15 регистра команд, регистр 16 сдвига, входы записи 17 и сдвига 18 регистра сдвига,четвертый выход 19 регистра команд, вход 20 запуска устройства, выход 21 признака конца вы- числений системы булевых функций.Бло 2 выборки содержит счетчик 22, узел 23 постоянной памяти и мультиплексор 24.

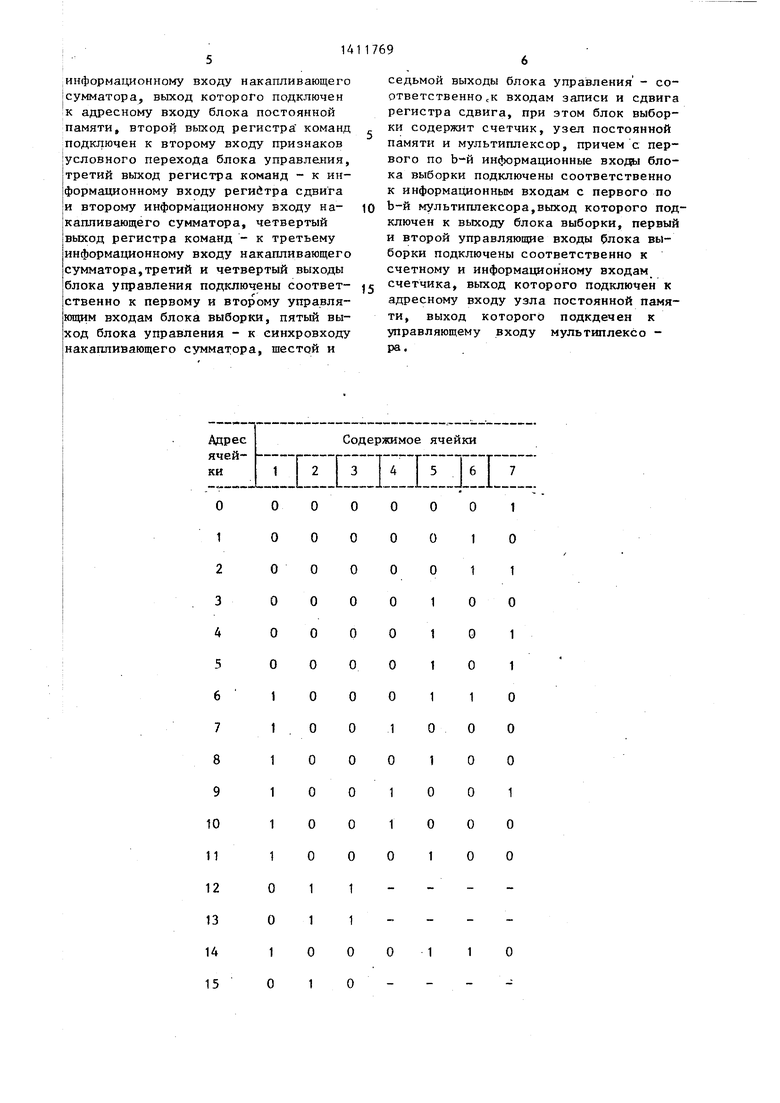

На ;хеме работы блока управления обозначены следующие микрооперации и признаки:. Р1 - содержимое разряда регистра 10 команд, соединенного с выходом 11; Р2 содержимое разряда ргистра 10 команд, соединенного с выходом 12; А1 - микрооперация установки в начальное состояние блока 2, сумматора 5 и установка признака отсутствия результата на выходе 21; А2 - микрооперация записи содержимо- го блока 8 памяти в регистр 10 команд; A3 - микрооперация выбора очередной обрабатываемой переменной и подачи ее на выход 4; А4 - микрооперация записи в регистр 16 сдвига; А5 - микрооперация суммирования текущего содержимого накапливающего сумматора и числа, указываемого на выходах 19 регистра 10 команд; А6 - микрооперация установки признака готовности результата на выходе 21; А7 - микрооперация записи информации в накапливающий сумматор 5; АЗ - микрооперация сдвига регистра 16 сдви

с

о5 0 5 о

5

0

5

га; А9 - микрооперация увеличения на единицу содержимого накагшив,ающе- го сумматора.

Устройство работает следующим образом.

В исходном состоянии на входы 1 поданы значения входных переменных (например, от внешних регистров). Работа устройства начинается с подачи импульса запу.ка на вход 20, по которому блок управления устанавливается в начальное состояние, начиная затем обработку алгоритма управления. В соответствии со схемой алгоритма (4ЯГ.З) на соответствующие входы 3 и 6 подаются сигналы начальной установки блоков 2 и 5, устанавливается признак отсутствия результата на выходе 21. Блок В памяти используется только в режиме считывания, поэтому через время, необходимое для установки значений на выходах 7 и 9, выдается сигнал записи в регистр 10 команд. Пара разрядов Р1 и Р2, соединенных с выходами 11 и 12,интерпре-. тируется следуклдим образом:если Р1( Р2 0, то выполняется обработка следующей переменной; если Р1 0, Р2 1, то выводится промежуточный результат вычисления; если Р1 1, Р2 О, то выполняется безусловный переход; если Р1 1, Р2 1, то инициируется останов устройства.

1 .

При обработке следующей переменной, в регистре 10 команд содержится информация для формирования адреса условного перехода по значению следующей переменной (в разрядах, соединенных с выходами 19). Микрооперация A3, инициирует подачу на выходы 4 значения обрабатываемой переменной. В общем случае логические переменные могут быть многозначными, т.е. блок

2имеет в общем случае более одного выхода. Поясним его работу. Счетчик 22 предназначен для последовательного воспроизведения адресов -узла 23 памяти (работающего только на считывание) , содержимое соответствующих ячеек которого равно номеру входов, которые с помощью мультиплексора 24 подключаются на выходы 4.. При подаче управляющего сигнала на счетный вход счетчика 22 (начальное состояние установлено по второму управляющему входу) после окончания переходных процессов в узле памяти и мультиплексоре на выходах 4 устанавливается значение переменной.

Информация с линий 4 и 19 микрооперацией А7 записывается в накапливающий сумматор 5, содержимое которого представляет собой адрес следующей команды.

Если на регистре команд находится команда вывода промежуточного результата, на выходе 15 находится значение этого промежуточного результата. Микрооперациями А4, А8 промежуточньй результат записывается в регистр 16 сдвига, микрооперацией А9 подготавливается адрес следующей по порядку команды.

При безусловном переходе микрооперацией А7 выполняется сложение текущего содержимого накапливающего сумматора и константы, указываемой в разрядах, соединенных с выходами 19. Результат является адресом следующей команды.

При инициировании останова устройства, означающего, что вычисления закончены, устанавливается признак готовности результата, и блок управления переходит в конечное состояние Результат вычисления находится в регистре 16 сдвига.

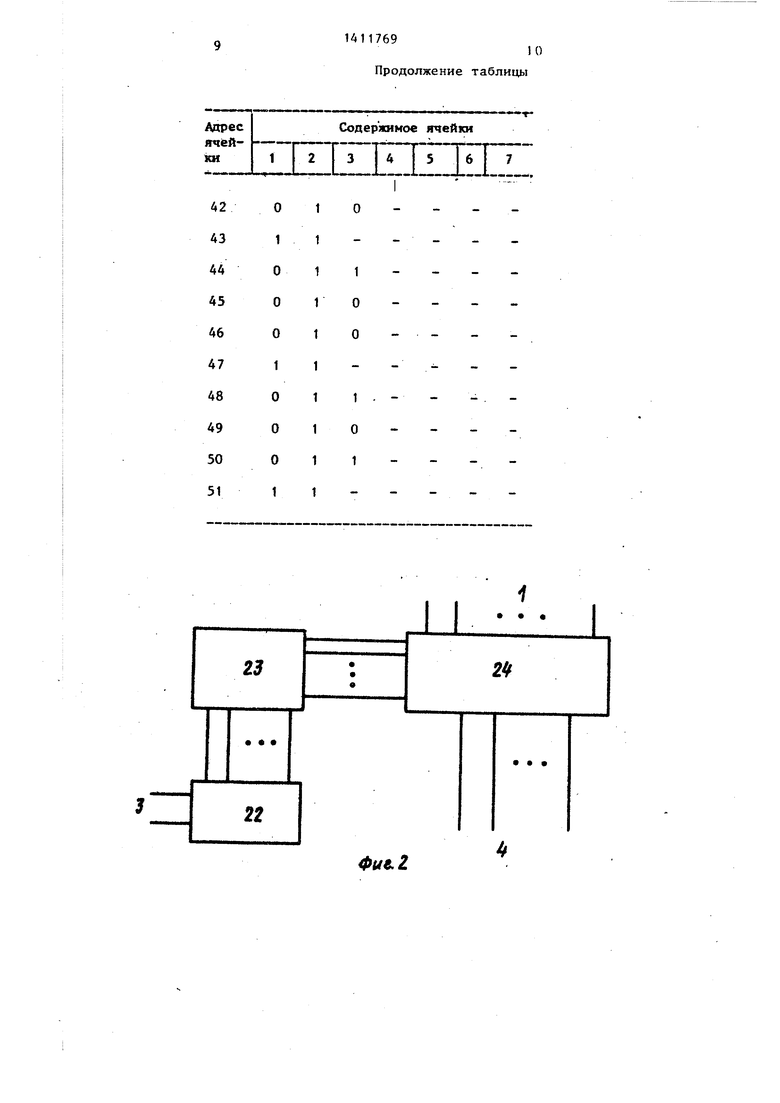

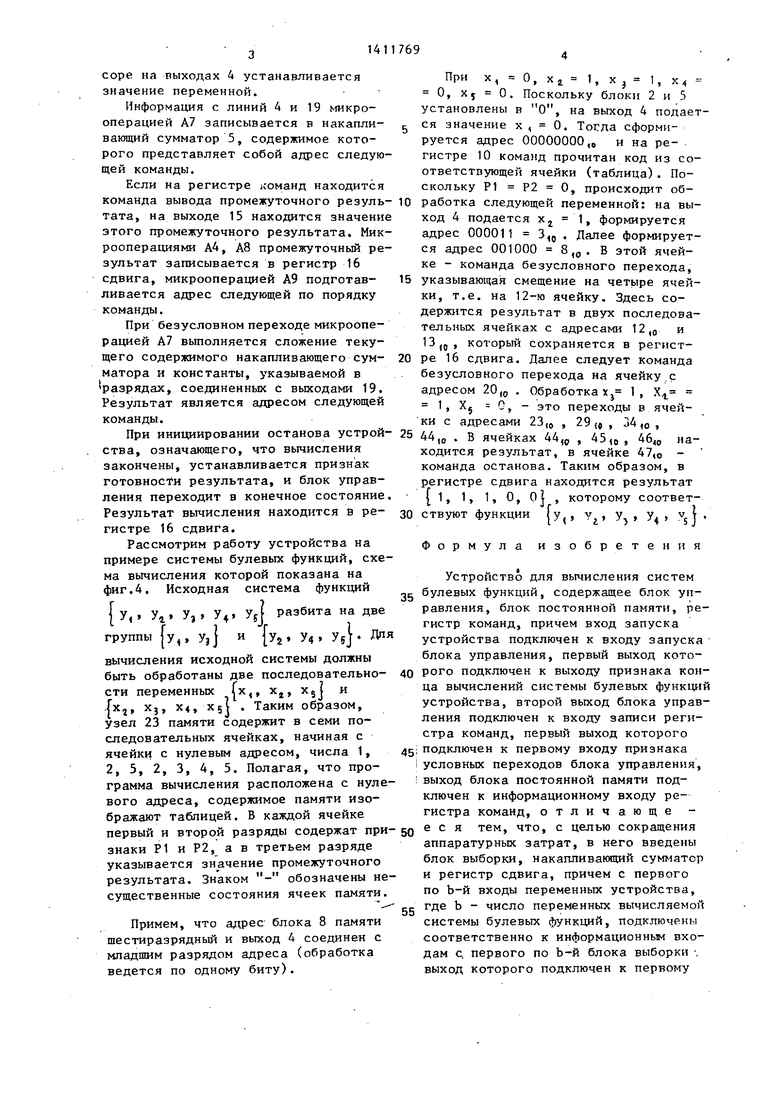

Рассмотрим работу устройства на примере системы булевых функций, схема вычисления которой показана на фиг.4. Исходная система функций

у,, Уг, У,, У4. У разбита на две группы у,, yj и yj,, у,, yjj. Для

вычисления исходной системы должны быть обработаны две последовательности переменных ,, х, Xjj и .fxj, X,, Х4, xg . Таким образом, узел 23 памяти содержит в семи последовательных ячейках, начиная с ячейки с нулевым адресом, числа 1, 2, 5, 2, 3, 4, 5. Полагая, что программа вычисления расположена с нулевого адреса, содержимое памяти изображают таблицей. В каждой ячейке первый и второй разряды содержат признаки Р1 и Р2, а в третьем разряде указывается значение промежуточного результата. Знаком - обозначены несущественные состояния ячеек памяти.

Примем, что адрес блока 8 памяти щестиразрядньв и выход 4 соединен с младшим разрядом адреса (обработка ведется по одному биту).

При X, 0, Xj 1, Xj 1, Х4

О, Xj 0. Поскольку блоки 2 и 5 установлены в О, на выход 4 подается значение х, 0. Тогда сформируется адрес 00000000,0 и на ре- гистре 10 команд прочитан код из соответствующей ячейки (таблица). Поскольку Р1 Р2 О, происходит обработка следующей переменной: на выход 4 подается х 1, формируется адрес 000011 3, . Далее формируется адрес 001000 8,о. В этой ячейке - команда безусловного перехода,

указывающая смещение на четыре ячейки, т.е. на 12-ю ячейку. Здесь содержится результат в двух последовательных ячейках с адресами 12,о и 13,j, который сохраняется в регистре 16 сдвига. Далее следует команда безусловного перехода на ячейку.с адресом 20,5 Обработка х 1, X 1 Xj О, - это переходы в ячейки с адресами 23,9 , 29 , , 34 ,о ,

44,0 . В ячейках 44,р , 45,о , 46,(, находится результат, в ячейке 47,о - команда останова. Таким образом, в регистре сдвига находится результат l, 1, 1, О, 0{ , которому соответствуют функции у, у.,, у , у , Vjj .

Формула изобретения

Устройство для вычисления систем

булевых функций, содержащее блок управления, блок постоянной памяти, регистр команд, причем вход запуска устройства подключен к входу запуска блока управления, первый выход которого подключен к выходу признака конца вычислений системы булевых функций устройства, второй выход блока управления подключен к входу записи регистра команд, первый выход которого

подключен к первому входу признака условных переходов блока управления, ВЫХОД блока постоянной памяти подключен к информационному входу регистра команд, отличающе

е с я тем, что, с целью сокращения аппаратурных затрат, в него введены блок выборки, накапливающий сумматор и регистр сдвига, причем с первого по Ь-й входы переменных устройства,

где b - число переменных вычисляемой системы булевых функций, подключены соответственно к информационные входам с. первого по Ь-й блока выборки , выход которого подключен к первому

информагдионному входу накапливающего сумматора, выход которого подключен к адресному входу блока постоянной памяти, второй выход регистра команд подключен к второму входу признаков условного перехода блока управления, третий выход регистра команд - к информационному входу регистра сдвига и второму информационному входу на- капливающего сумматора, четвертый вькод регистра команд - к третьему информационному входу накапливающего сумматора,третий и четвертый выходы блока управления подключены соответ- ственно к первому и второму управляющим входам блока выборки, пятый выход блока управления - к синхровходу накагшивающего сумматора, шестой и

седьмой выходы блока упра вления - соответственно к входам записи и сдвига регистра сдвига, при этом блок выборки содержит счетчик, узел постоянной памяти и мультиплексор, причем с первого по Ь-й информационные входы блока выборки подключены соответственно к информационным входам с первого по Ь-й мультиплексора,выход которого подключен к выходу блока выборки, первый и второй управляющие входы блока выборки подключены соответственно к счетному и информационному входам счетчика, выход которого подключен к адресному входу узла постоянной памяти, выход которого подкдечен к управляющему входу мультиплексо - ра. ,

Продолжение таблицы

Продолжение таблицы

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления систем булевых функций | 1986 |

|

SU1424005A1 |

| Устройство для вычисления систем булевых функций | 1987 |

|

SU1424007A1 |

| Устройство для вычисления систем булевых функций | 1987 |

|

SU1509865A1 |

| Устройство для вычисления систем булевых функций | 1988 |

|

SU1532912A1 |

| Устройство для вычисления систем булевых функций | 1988 |

|

SU1631537A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Микропрограммный процессор | 1987 |

|

SU1517034A1 |

| Устройство для обработки структур данных | 1990 |

|

SU1709328A1 |

| Устройство для реализации временных булевых функций | 1985 |

|

SU1290346A1 |

| Устройство для вычисления булевых функций | 1980 |

|

SU955027A1 |

Изобретение относится к автоматике и вычислительной технике и - предназначено для вычисления значений систем булевых функций на наборе двоичных переменных. Целью изобретения является сокращение аппаратурных затрат за счет сокращения объема программной памяти. Поставленная цель достигается тем, что устройство для вычисления систем булевых функций содержит с первого по Ь-й входы 1 переменных, где b - число переменных вычисляемой системы булевых функций, блок 2 выборки, информационные входы 3 блока выборки, выход 4 блока выборки, накапливающий- сумматор 5, управляющий вход 6 накапливающего сумматора, выход 7 накапливающего сумматора, блок 8 постоянной памяти, выход 9 блока постоянной памяти, регистр 10 команд, первый 11 и в горой 12 выходы регистра команд, блок 13 управления,вход 14 записи регистра команд, третий выход 15 регистра команд, регистр 16 сдвига, входы записи 17 и сдвига 18 регистра сдвига, четвертый выход 19 регистра команд, вход 20 запуска устройства, выход 21 признака конца вычислений системы булевых функций. 4 ил., 1 табл . € (Л

23

1

2ff

Фие.2

У1Уз

I AS I Щ

Фаг. J

Uti/ifys

Фив,

| Амбарцумян А.А., Потехин А.И | |||

| и Запольский Е.Н | |||

| Программируемые логические контроллеры и их применение | |||

| - Измерение, контроль, автоматизация, 1979, № 40 (20), с.25-33 | |||

| Информационные системы: Табличная обработка информации | |||

| / Под ред | |||

| Е.П.Балашова и В.Б.Смолова | |||

| Л.: Энер- гоатомиздат, Ленингр | |||

| отд | |||

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

Авторы

Даты

1988-07-23—Публикация

1986-11-13—Подача