f ю

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления систем булевых функций | 1986 |

|

SU1411769A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

| Микропрограммное устройство управления | 1990 |

|

SU1798781A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

Изобретение относится к автоматике и вьгчислител1,нор1 технике и предназначено для вьгтислеттия знлчснтгй систем булевых функций нп наборе двоичных цеременньк. Целько изобретения является сокращение аппаратурных затрат. Поставленная целГ) достигается тем, что устройство содержит вход 1 переменных, сдвигопьй регистр 2 данных, первьй мультиплексор 3, регистр 4 команд, регистр адреса 5, шинный формирователь 6. льтиплeк- сор 7, блок 8 памяти, nepiifcn i регис1 р 9, второй регистр 10, блок 11 стековой памяти, сумматор 12, блок 13 управления. 3 ил.

о -vl

11Д240

Изобретение относится к автоматике I) вьгчислител1)НоУ1 технике и предназначено для ньршслеиия систем булевых функций.

Целью изобретения является сокращение аппаратурных затрат,

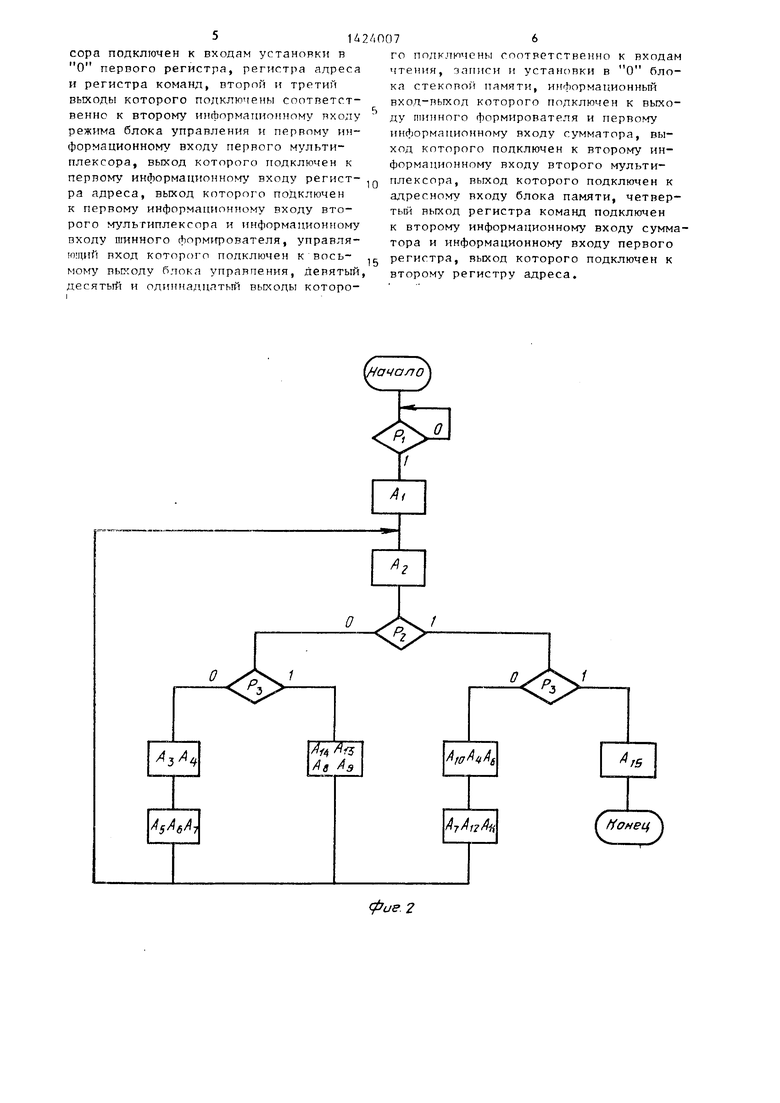

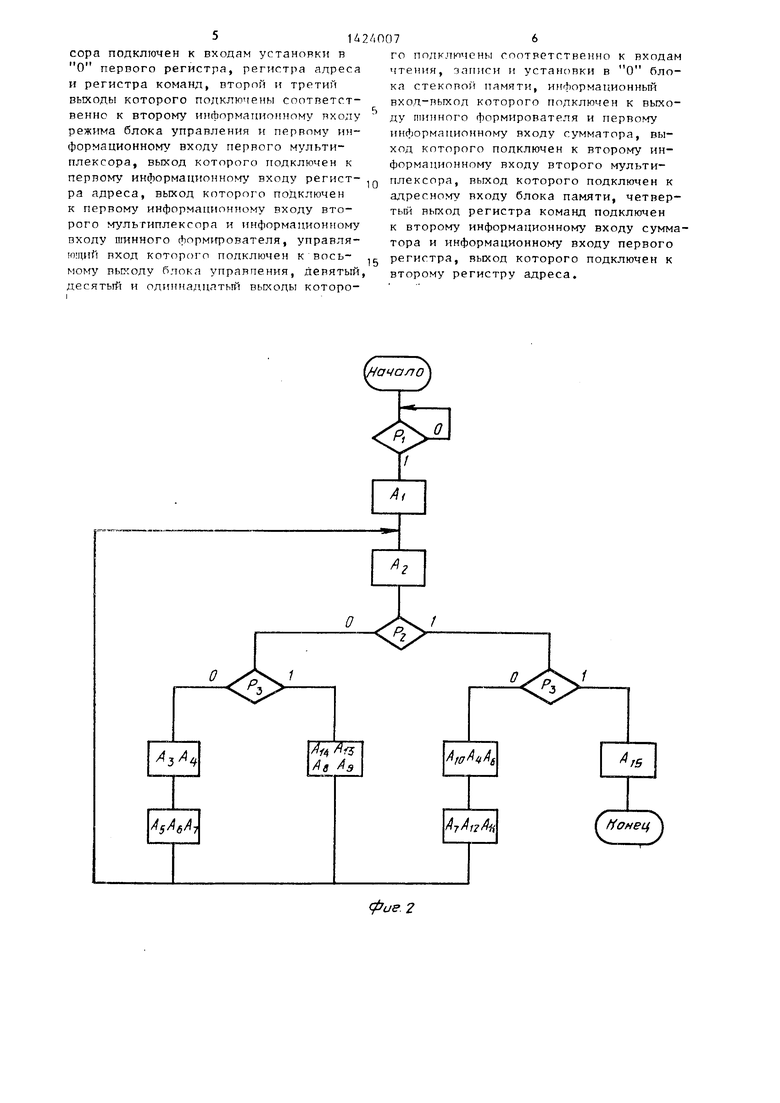

На фиг.1 представлена схема уст- ройства на фиг.2 - микропрограмма работы блока управления; на фиг.З - JQ пример организации подпрограммы для одинаковых участков программы.

Устройство содержит вход 1 переменных, сдвиговый регистр 2, первый мультиплексор 3, регистр 4 команд, регистр 5 адреса, шинный формирователь 6, второй мульт1шлексор 7, блок 8 памяти, первьп 9 и второй 10 реги15

стры, блок 11 стековой памяти, сумматор 12, блок 13 управления, с перво- го по одинна/ииттьп выходы 14-24 блока 13 управления, вход 25 запуска устройства, первьгй 26 и второй 27 входы режима блока 13

25

Обобшеиняя микропрограмма работы лока упрапления содержит следующие боэначеиип микроопераций и призна- о Г г

Р - знлчоьпс рхода 25 запуска, 30 связанного с блоком 13 управления ;

Р,, - содержимое разряда регистра 4 команд, сосд1 1спного с входом 26 блока 13 управленияJ 35

- содержимое разряда регистра

4 команд, соединенного с вхо- 27 блока 13 управления

Л - микрооперация установки в начальное состояние регистров 0 2 и 5, установка признака отсутствия результата на выхо- де 14;

Л 2 I кpooпepaцIш записи содержимого блока 8 памяти в регистр дс 4 команд-,

Aj - микрооперация выбора очередной обрабатываемой перемеьиюй и подача ее на вход мультиплексора 3;

Л, микрооперация записи в регистр 9 значений с выходов регистра

4команд,

A.g - микрооперация настройки 1 гуль- Т1шлексора 3 па прием значений с выхода регистра 2

А(; - микрооперация записи в регистр

5адреса с выхода мультиплексора 3 и выходов регистра 9;

50

55

JQ

АГ 15

20

25

30

35

0

дс

0

5

А, АО А«

45

4

45

микрооперация настройки мультиплексора на прием значений с выходов регистра 5 адреса/ мшсрооперация суммирования в сумматоре 12 значений, поступающих с выходов блока 11, и значений, поступающих с входов регистра 4 команд; микрооперация настройки мультиплексора 7 на прием значений с выходов сумматора 12, микрооперация настройки мультиплексора 3 на прием значений с выхода регистра 2 сдвига;

-микрооперация настройки шинных формирователей 6 на передачу значе} ий из регистра 5 адреса в блок 11;

2 - микрооперация настройки блока

I1 на режим записи;

-микрооперация установки шинных формирователей 6 в состояние импеданса-,

-микрооперация настройки блока

I1на режим считывания;

-микрооперация установки признака готовности на выходе 14.

Устройство работает следующим образом.

Перед началом работы блок 13 управления устанавливается в исходное состояние. На вход 1 подаются значения входных переменных. При подаче импульса запуска на вход 25 блока 13 управления с его выходов выдаются сигналы начальной установки регистров и один из сигналов начальной установки стека, а на выходе 14 устанавливается признак отсутствия результата. Кроме того, на регистр 2 подается сигнал записи в регистр 2 значений входных переменных с входов 1.

Пара разрядов Р и Р регистра 4 интерпретируч тся следующим образом:

если Pj 0, 0, то выполняется обработка следующей переме;1ной;

если Рг 0, Pj 1, то выполняется выход из подпрограммы;

если PZ 1, Ij 0 то вьтолняется переход к подпрограмме;

если , то инициируется останов устройства.

Рассмотрим все эти случаи. При обработке следующей переменной блок 13 управления вырабатывает сигнал, которьпЧ поступает на вход управления

10

1А2Д007

сдвигом регистра 2. Происходит сдвиг

содержимого регистра 2 влево на один разряд. С начение этого разряда поступает на вход мудьтипдексора 3. Из мультипдексора 3 это значение передается на вход регистра 5 адреса (в младший разряд). В регистр 9 записывается информация, поступающая из регистра А команд. В шинные формирова- теди 6 из блока 13 управдения подается сигнал, KOTopbDi устанавливает шинные формирователи 6 в состояние и теданса, при этом блок 11 отключен от выхода регистра 5 адреса (режим считывания из стека). Мультиплексор 7 настраивается на передачу значений из регистра 9. С выхода мультиплексора 7 значения поступают на адресные входы блока 8 памяти, откуда информация заносится в регистр 4 команд. 20 При переходе к выполнению подпрограммы происходит настройка мультиплеАсо- ра 3 по управляющим сигналам, поступающим в регистр 10, которые затем передаются на управляющие входы мультиплексора 3, на прием значений, поступающих из регистра А. В регистр 9 поступают значения с выходов регистра

4(эти значения являются адресом начала подпрограммы). С регистра 9 эти значения поступают на входы регистра 5. Блок 11 устанавливается в режим записи, шинные формирователи 12 - в режим передачи информации от регистра 5 адреса к блоку 11. Мультиплексор 7 настроен на прием информации из регистра адреса. Происходит передача адреса подпрограммы из регистра

5адреса и одновременная запись этого адреса в блоке 11. Через мультиплексор 7 адрес передается на адресные входы блока 8 памяти. Информация из блока 8 памяти передается в регистр

Пример. Пусть имеются два фрагмента программы: а) с переменными Х и Xj и б) с переменными , и X;,, . Эти участки программы одинаковы В и отличаются лишь значениями функций. Их можно представить в виде подпрограммы, в которой вместо значений функций содержится смещение, так как оно одинаково для случая а) и б).

Рассмотрим вьтолнение подпрограммы для случая б).

Значения смещения следующие: А 3, , . Пусть , а )Сц 1. До вершины программа выполняется обычным способом, а с нее начинается вьтолнение Подпрограммы. Значение адреса вершины 10 заносится в стек. С регистра 2 считывается 0, осуществляется переход к верпшне Х , Считывается ее значение ( 1. Далее следует команда возврата из подпрограммы. Формируется адрес возврата 10 + и осуществляется переход к вершине 14.

25

Формула изобретения

30

Устройство для вычисления систем булевых функций,содержащее сдвиговый регистр,регистр адреса,регистр команд, блок памяти и блок управления,вход переменных устройства подключен к информационному входу сдвигового регистра, вход запуска устройства под35 ключен к входу запуска блока управления, первый выход которого подключен к выходу признака готовности устройства, выход блока памяти подключен к информапионному входу регистра

40 команд, вход записи которого подключен к второму выходу блока управления, первый вход режима которого подключен к первому выходу регистра ко- команд. Подпрограмма продолжает свою манд, отличающееся тем, работу до тех пор, пока не встретится 45 что, с целью сокращен11Я аппаратурных команда возврата из подпрограммы, при затрат, устройство содержит первый и этом шинные формирователи 6 устанавливаются в состояние импеданса, блок

11 - в режим считывания. Информация

второй мультиплексоры, первый и второй регистры, блок стековой памяти, шинный формирователь и сумматор, при

из блока 11 поступает на первый вход gp этом с третьего по шестой выходы блосумматора 12, а на второй вход сумма- ка управления подключены соответсттора поступает значение смещения из

регистра 4 команд. Р результате сложения адреса, записанного в стеке, и

венно к входам записи сдвигового регистра, разрешения сдвига, регистра сдвига, записи первого регистра и к смещения полут гится адрес возврата. gg информационному входу второго регист- Мультиплексор 7 настроен на прием ад- ра, первый и второй выходы которого реса из сумматора 1 2 . По окончании работы подключены к управляющим входам соот- устройства формируется признак готов- ветственно первого и второго мульти- ности результата и происходит останов. плексоров, седьмой выход мультиплек

7

Пример. Пусть имеются два фрагмента программы: а) с переменными Х и Xj и б) с переменными , и X;,, . Эти участки программы одинаковы и отличаются лишь значениями функций. Их можно представить в виде подпрограммы, в которой вместо значений функций содержится смещение, так как оно одинаково для случая а) и б).

Рассмотрим вьтолнение подпрограммы для случая б).

Значения смещения следующие: А 3, , . Пусть , а )Сц 1. До вершины программа выполняется обычным способом, а с нее начинается вьтолнение Подпрограммы. Значение адреса вершины 10 заносится в стек. С регистра 2 считывается 0, осуществляется переход к верпшне Х , Считывается ее значение ( 1. Далее следует команда возврата из подпрограммы. Формируется адрес возврата 10 + и осуществляется переход к вершине 14.

Формула изобретения

Устройство для вычисления систем булевых функций,содержащее сдвиговый регистр,регистр адреса,регистр команд, блок памяти и блок управления,вход переменных устройства подключен к информационному входу сдвигового регистра, вход запуска устройства подключен к входу запуска блока управления, первый выход которого подключен к выходу признака готовности устройства, выход блока памяти подключен к информапионному входу регистра

команд, вход записи которого подключен к второму выходу блока управления, первый вход режима которого подсора подключен к входам установки в О первого регистра, регистра адреса и регистра команд, второй и третий выходы которого подключены соответственно к второму информационному входу режима блока управления и первому информационному входу первого мультиплексора, выход которого подключен к первому информационному входу регистра адреса, выход которого подключен к первому информационному входу второго мультиплексора и информационному входу шинного Лорм фователя, управляющий вход которого подключен к восьмому вьс:оду блока управпения, девятый десятый и одиннадцатый вькоды которо

го подключены соответстве,нно к входам чтения, загтиси и установки в О блока стековоГ памяти, информа1 ионный вход-выход которого подключен к выходу тинного формирователя и первому информационному входу сумматора, выход которого подключен к второму информационному входу второго мультиплексора, выход которого подключен к адресно гу входу блока памяти, четвертый выход регистра команд подключен к второму информационному входу сумматора и информационному входу первого регистра, выход которого подключен к второму регистру адреса.

f//fff/eifj

фие. 2

фиг

| Приспособление для останова мюля Dobson аnd Barlow при отработке съема | 1919 |

|

SU108A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Амбруцумян.А.А., Потехин А.И., Запольский Е.Н | |||

| Программные логические контроллеры и их применение | |||

| - Изменение, контроль, автоматизация, 19797 40(20), с.25-30. | |||

Авторы

Даты

1988-09-15—Публикация

1987-02-17—Подача