00

а

СП

31

Изобретение относится к автоматике и вычислительной технике и предназначено для вычисления системы булевых функций.

Цель изобретения - сокращение времени, повьшение производительности устройства.

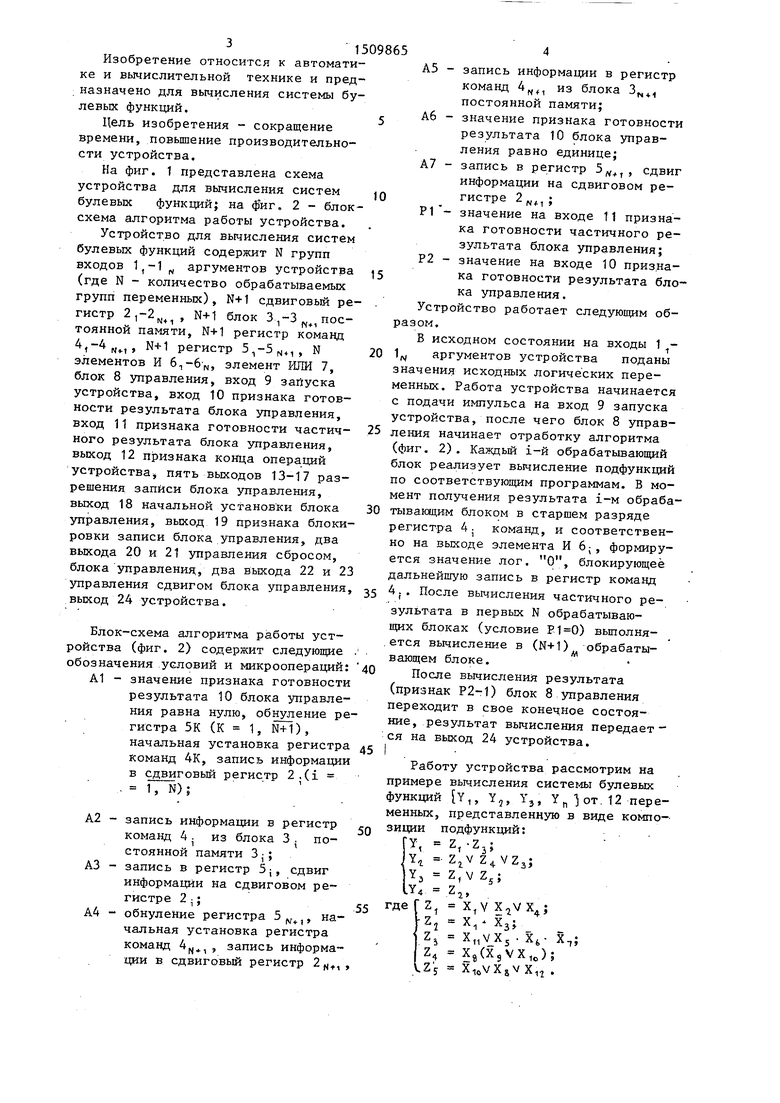

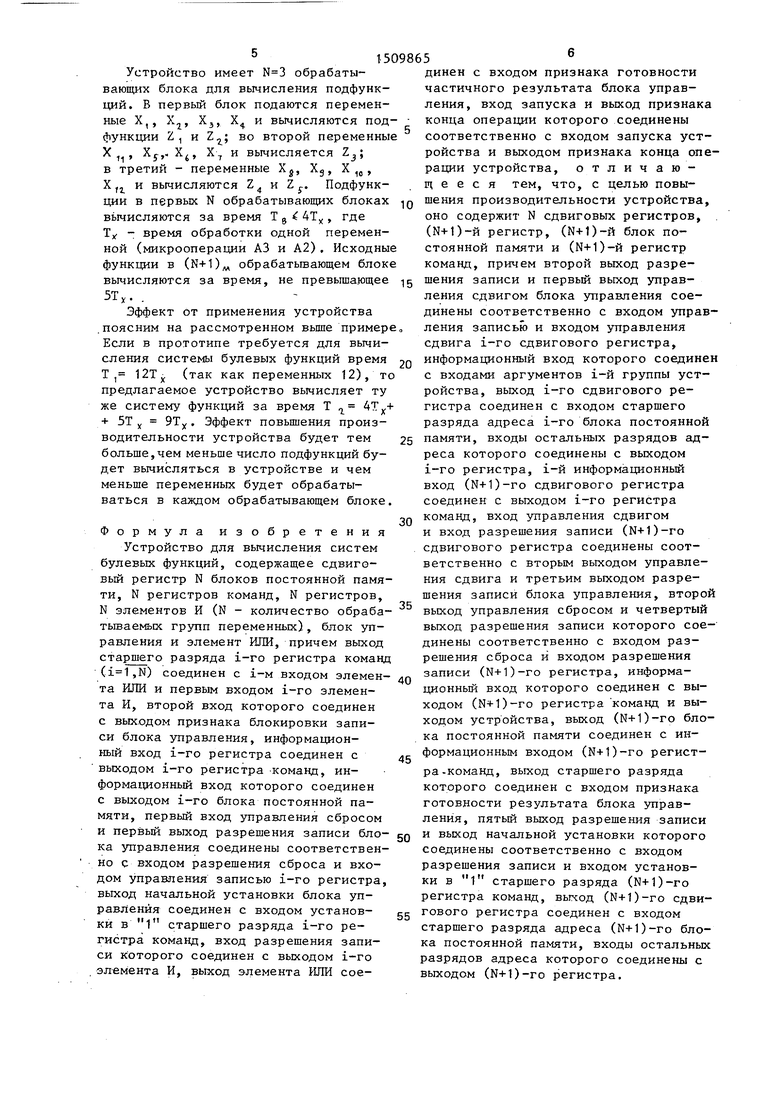

На фиг. 1 представлена схема устройства для вычисления систем булевых функций; на кг, 2 - блок схема алгоритма работы устройства.

Устройство для вычисления систем булевых функций содержит N групп входов 1,-1 1 аргументов устройства (где N - количество обрабатываемых групп переменных), N+1 сдвиговый ре гистр 2,-2, N+1 блок 3,-3, постоянной памяти, N+1 регистр команд N регистр ,, N элементов И бт-б, элемент ИЛИ 7, блок 8 управления, вход 9 зайуска устройства, вход 10 признака готовности результата блока управления, вход 11 признака готовности частичного результата блока управления, выход 12 признака конца операций устройства пять выходов 13-17 разрешения записи блока управления, выход 18 начальной установки блока управления, выход 19 признака блокировки записи блока управления, два выхода 20 и 21 управления сбросом, блока управленид, два выхода 22 и 2 управления сдвигом блока управления выход 24 устройства.

Блок-схема алгоритма работы устройства (фиг. 2) содержит следующие обозначения условий и микроопераций: А1 - значение признака готовности результата 10 блока управления равна нулю, обнуление регистра 5К (К 1, N+1), начальная установка регистра команд 4К, запись информации в сдвиговьй регистр 2.(i , 1, N);

запись информации в регистр команд А j из блока 3 j постоянной памяти 3 j;

запись в регистр 5;, сдвиг информации на сдвиговом регистре 2 ;

обнуление регистра 5

чальная установка регистра

накоманд 4

9.

запись информа™

ции в сдвиговый регистр 2

N + 1

1,

А5 - запись информации в регистр команд 4, из блока 3 постоянной памяти;

Аб - значение признака готовности результата 10 блока управления равно единице;

А7 - запись в регистр 5, сдвиг информации на сдвиговом регистре 2„,, ;

Р1 - значение на входе 11 признака готовности частичного результата блока управления;

Р2 - значение на входе 10 признака готовности результата блока управления.

Устройство работает следующим образом.

В исходном состоянии на входы 1 аргументов устройства поданы

5 .

5

0

0

значения исходных логических переменных. Работа устройства начинается с подачи импульса на вход 9 запуска устройства, после чего блок 8 управ- 5 ления начинает отработку алгоритма (фиг. 2). Каждый i-и обрабатывающий блок реализует вычисление подфункций по соответствующим программам. В момент получения результата i-м обрабатывающим блоком в старшем разряде регистра 4j команд, и соответственно на выходе элемента И 6;, формируется значение лог. О, блокирующее дальнейшую запись в регистр команд 4j. После вычисления частичного результата в первых N обрабатывающих блоках (условие ) вьшолня- ется вычисление в вающем блоке.

После вычислений результата (признак Р2-1) блок 8 управления переходит в свое конечное состояние, результат вычисления передается на выход 24 устройства.

(N+1),. обрабатылЛ

Работу устройства рассмотрим на примере вычисления систегл. булевых функций Y,, У,, УЗ, У„ IOT. 12 переменных, представленную в виде компо-- зиции подфункций: . .

т

Устройство имеет обрабатывающих блока для вычисления подфункций. В первый блок подаются переменные X., Xj, X,, Х и вычисляются под Z , и

1 функции i. , п с.,

X.,, Хг,. X,, Х- и

3 Z.

4 ВО

11 ( т

В третий - переменные Х,г

второй переменны вычисляется Z

Xл, X

Ч

X

3

вычисляются Z. и Z

sЭ 10 Подфункции в первых N обрабатывающих блоках вьгчисляются за время Т g 4Т , где Ту - время обработки одной переменной (микрооперации A3 и А2), Исходны функции в (N+1) обрабатьшающем блок вычисляются за время, не превьппающее 5Т,. .

Эффект от применения устройства .поясним на рассмотренном выше пример Если в прототипе требуется для вычисления системы булевых функций время Т , 12Tj (так как переменных 12), то предлагаемое устройство вычисляет ту же систему функций за время Т + 5Т 9Ту. Эффект повьшения производительности устройства будет тем больше,чем меньше число подфункций будет вычисляться в устройстве и чем меньше переменных будет обрабатываться в каждом обрабатывающем блоке

Формула изобретения

Устройство для вычисления систем булевых функций, содержащее сдвиговый регистр N блоков постоянной памяти, N регистров команд, N регистров.

динен с входом признака готовности частичного результата блока управления, вход запуска и выход признака конца операции которого соединены соответственно с входом запуска устройства и выходом признака конца операции устройства, отличающееся тем, что, с целью повышения производительности устройства, оно содержит N сдвиговых регистров, (Н+1)-й регистр, (Ы+1)-й блок постоянной памяти и (N+1)-й регистр команд, причем второй выход разрешения записи и первый выход управления сдвигом блока управления соединены соответственно с входом управления записью и входом управления сдвига i-ro сдвигового регистра, информационный вход которого соединен с входами аргументов i-й группы устройства, выход i-ro сдвигового регистра соединен с входом старшего разряда адреса i-ro блока постоянной памяти, входы остальных разрядов адреса которого соединены с выходом i-ro регистра, i-й информационный вход (N+1)-ro сдвигового регистра соединен с выходом i-ro регистра команд, вход управления сдвигом и вход разрешения записи (N+1)-ro сдвигового регистра соединены соответственно с вторым выходом управления сдвига и третьим выходом разрешения записи блока управления, второй

30

f f -7 od

N элементов И (N - количество обраба- выход управления сбросом и четвертый

IQ15

2п

9865°

динен с входом признака готовности частичного результата блока управления, вход запуска и выход признака конца операции которого соединены соответственно с входом запуска устройства и выходом признака конца операции устройства, отличающееся тем, что, с целью повышения производительности устройства, оно содержит N сдвиговых регистров, . (Н+1)-й регистр, (Ы+1)-й блок постоянной памяти и (N+1)-й регистр команд, причем второй выход разрешения записи и первый выход управления сдвигом блока управления соединены соответственно с входом управления записью и входом управления сдвига i-ro сдвигового регистра, информационный вход которого соединен с входами аргументов i-й группы устройства, выход i-ro сдвигового регистра соединен с входом старшего разряда адреса i-ro блока постоянной памяти, входы остальных разрядов адреса которого соединены с выходом i-ro регистра, i-й информационный вход (N+1)-ro сдвигового регистра соединен с выходом i-ro регистра команд, вход управления сдвигом и вход разрешения записи (N+1)-ro сдвигового регистра соединены соответственно с вторым выходом управления сдвига и третьим выходом разрешения записи блока управления, второй

25

30

od

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления систем булевых функций | 1988 |

|

SU1532912A1 |

| Устройство для вычисления систем булевых функций | 1988 |

|

SU1631537A1 |

| Программируемый контроллер | 1989 |

|

SU1647594A1 |

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| Устройство для обнаружения ошибок в кодовой последовательности | 1988 |

|

SU1569996A1 |

| Модуль для вычисления булевых функций | 1989 |

|

SU1803908A1 |

| Устройство для вычисления систем булевых функций | 1987 |

|

SU1424007A1 |

| Устройство для вычисления порядковых статистик | 1987 |

|

SU1444822A1 |

| Устройство для вычисления булевых производных | 1987 |

|

SU1481793A1 |

| Устройство для вычисления систем булевых функций | 1986 |

|

SU1411769A1 |

Изобретение относится к автоматике и вычислительной технике и предназначено для вычисления систем булевых функций. Цель изобретения - увеличение производительности устройства. Устройство содержит N+1 сдвиговый регистр 21-2N+1, N+1 блок постоянной памяти 31-3N+1, N+1 регистр команд 41-4N+1, N+1 регистр 51-5N+1, N элементов И 61-6N, элемент ИЛИ 7 и блок управления 8. В первых N обрабатывающих блоках устройства обеспечивается вычисление подфункций заданной системы булевых функций, конечный результат которой вычислится в (N+1)-м обрабатывающем блоке. 2 ил.

тьшаемых групп переменных), блок управления и элемент ИЛИ, причем выход старшего разряда i-ro регистра команд (,N) соединен с i-м входом элемента ИЛИ и первым входом i-ro элемента И, второй вход которого соединен с выходом признака блокировки записи блока управления, информационный вход i-ro регистра соединен с выходом i-ro регистра команд, ин- формагщонный вход которого соединен с выходом i-ro блока постоянной памяти, первый вход управления сбросом и первый выход разрешения записи блока управления соединены соответственно с входом разрешения сброса и входом управления записью i-ro регистра, выход начальной установки блока управления соединен с входом установки в 1 старшего разряда i-ro регистра команд, вход разрешения записи которого соединен с выходом i-ro элемента И, выход элемента ИЛИ сое0

5

0

5

выход разрешения записи которого соединены соответственно с входом разрешения сброса и входом разрешения записи (N+1)-ro регистра, информа- здионный вход которого соединен с выходом ()-ro регистра команд и выходом устройства, выход (N+1)-ro блока постоянной памяти соединен с информационным входом (N+1)-ro регистра -команд, выход старшего разряда которого соединен с входом признака готовности результата блока управления, пятый выход разрешения записи и выход начальной установки которого соединены соответственно с входом разрешения записи и входом установки в 1 старшего разряда (N+1)-ro регистра команд, выход (N+1)-ro сдвигового регистра соединен с входом старшего разряда адреса (N+l)-ro блока постоянной памяти, входы остальных разрядов адреса которого соединены с выходом (N+1)-ro регистра.

tdD

/4

Фие.2

| Информационные системы | |||

| Таб- личная обработка информации./Под | |||

| ред | |||

| Е.П | |||

| Балашова и В.Б | |||

| Смолова.- Л.: Энергоатомиздат, 1985, с | |||

| Приспособление в центрифугах для регулирования количества жидкости или газа, оставляемых в обрабатываемом в формах материале, в особенности при пробеливании рафинада | 0 |

|

SU74A1 |

| Устройство для вычисления систем булевых функций | 1986 |

|

SU1424005A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-09-23—Публикация

1987-11-19—Подача