Изобретение относится к вычислительной технике,а именно к схемам адресации цифровых накопителей, и может быть применено в запоминающих устройствах с резервированием.

Цель изобретения - снижение энергопотребления и повышение надежности формирователя.

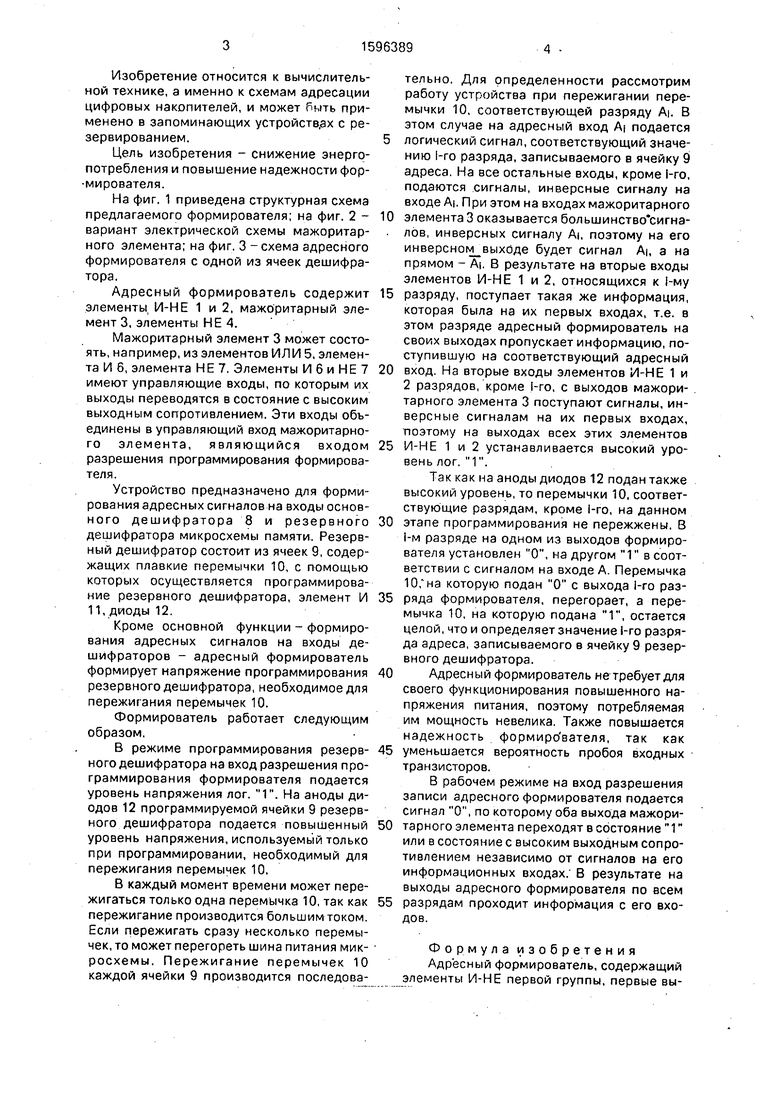

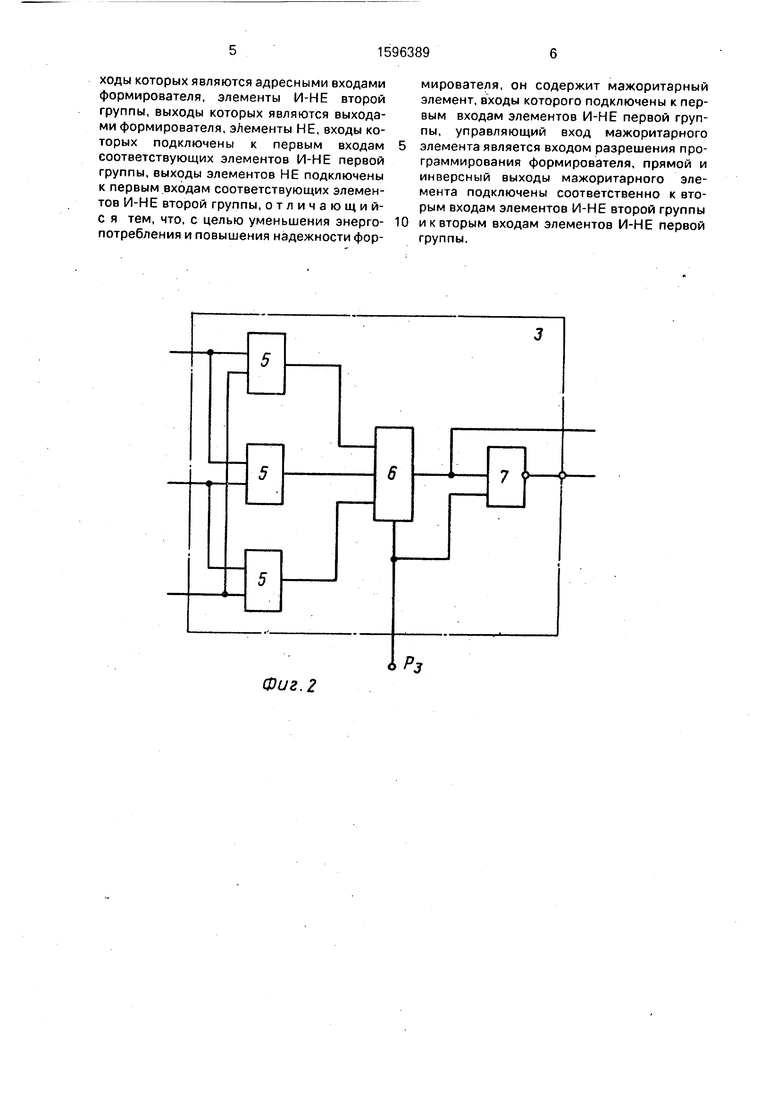

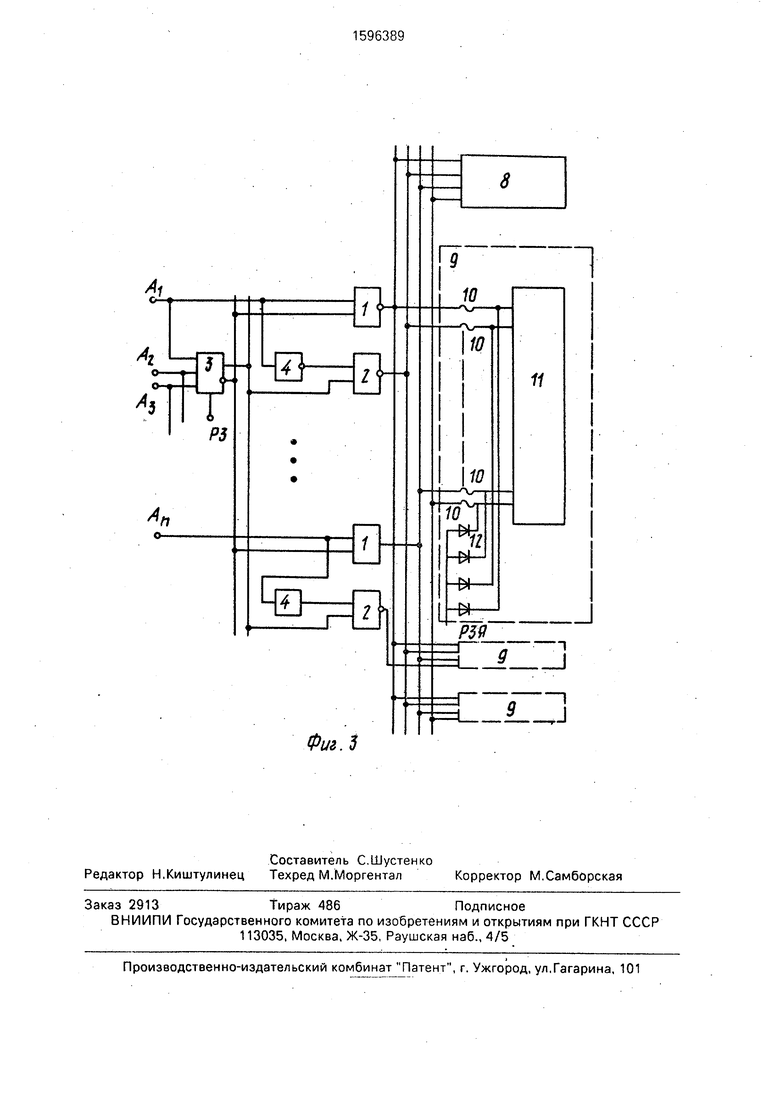

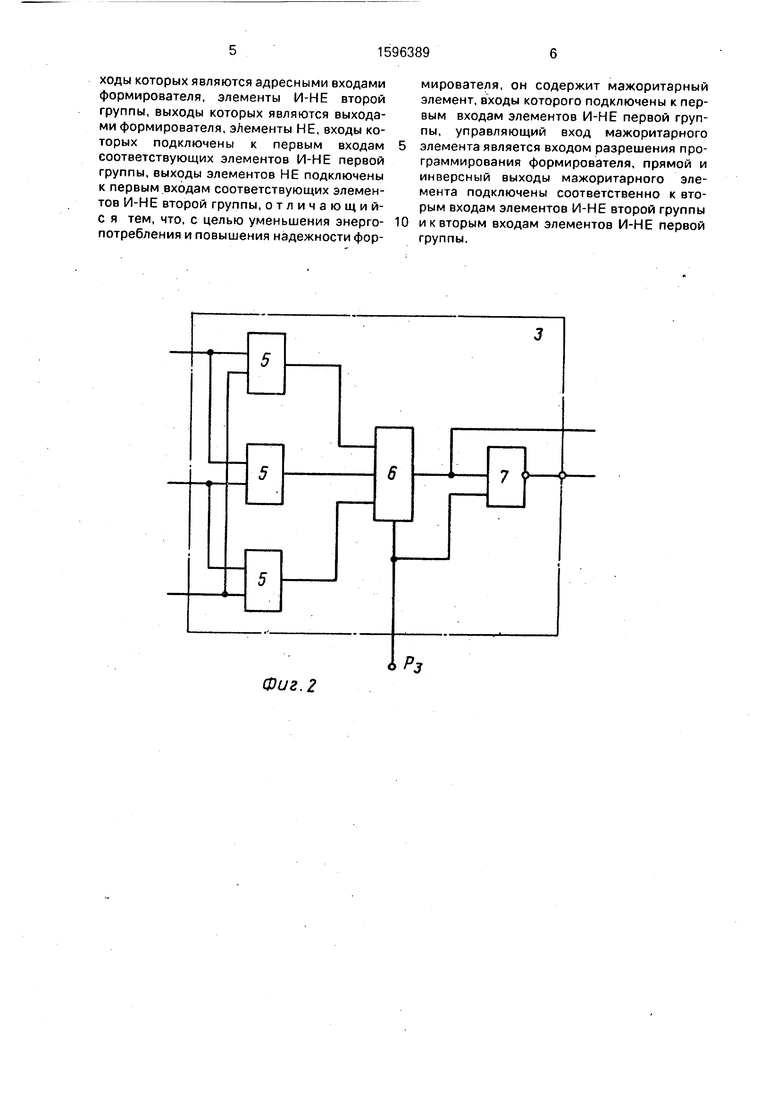

На фиг. 1 приведена структурная схема предлагаемого формирователя; на фиг. 2 вариант электрической схемы мажоритарного элемента; на фиг. 3 -схема адресного формирователя с одной из ячеек дешифратора.

Адресный формирователь содержит элементы, И-НЕ 1 и 2, мажоритарный элемент 3, элементы НЕ 4.

Мажоритарный элемент 3 может состоять, например, из элементов ИЛ И 5, элемента И б, элемента НЕ 7. Элементы И 6 и НЕ 7 имеют управляющие входы, по которым их выходы переводятся в состояние с высоким выходным сопротивлением. Эти входы объединены в управляющий вход мажоритарного элемента, являющийся входом разрешения программирования формирователя.

Устройство предназначено для формирования адресных сигналов на входы основного дешифратора 8 и резервного дешифратора микросхемы памяти. Резервный дешифратор состоит из ячеек 9, содержащих плавкие перемычки 10, с помощью которых осуществляется программирование резервного дешифратора, элемент И 11, диоды 12.

Кроме основной функции - формирования адресных сигналов на входы дешифраторов - адресный формирователь формирует напряжение программирования резервного дешифратора, необходимое для пережигания перемычек 10.

Формирователь работает следующим образом.

В режиме программирования резервного дешифратора на вход разрешения программирования формирователя подается уровень напряжения лог. 1. На аноды диодов 12 программируемой ячейки 9 резервного дешифратора подается повышенный уровень напряжения, используемый только при программировании, необходимый для пережигания перемычек 10.

В каждый момент времени может пережигаться только одна перемычка 10, так как пережигание производится большим током. Если пережигать сразу несколько перемычек, то может перегореть шина питания микросхемы. Пережигание перемычек 10 каждой ячейки 9 производится последовательно. Для определенности рассмотрим работу устройства при пережигании перемычки 10, соответствующей разряду Ai. В этом случае на адресный вход А| подается

логический сигнал, соответствующий значению 1-го разряда, записываемого в ячейку 9 адреса. На все остальные входы, кроме i-ro, подаются сигналы, инверсные сигналу на входе А|. При этом на входах мажоритарного

элемента 3 оказывается большинствосигналов, инверсных сигналу Ai, поэтому на его

инверсном выходе будет сигнал Ai, а на

прямом - Ai. В результате на вторые входы

элементов И-НЕ 1 и 2, относящихся к 1-му

разряду, поступает такая же информация, которая была на их первых входах, т.е. в этом разряде адресный формирователь на своих выходах пропускает информацию, поступившую на соответствующий адресный

вход. На вторые входы элементов И-НЕ 1 и 2 разрядов, кроме 1-го, с выходов мажоритарного элемента 3 поступают сигналы, инверсные сигналам на их первых входах, тюэтому на выходах всех этих элементов

И-НЕ 1 и 2 устанавливается высокий уровень лог. 1.

Так как на аноды диодов 12 подан также высокий уровень, то перемычки 10, соответствующие разрядам, кроме 1-го, на данном

этапе программирования не пережжены. В i-M разряде на одном из выходов формирователя установлен О, на другом 1 в соответствии с сигналом на входе А. Перемычка 10,на которую подан О с выхода 1-го разряда формирователя, перегорает, а перемычка 10, на которую подана 1, остается целой, что и определяет значение 1-го разряда адреса, записываемого в ячейку 9 резервного дешифратора.

Адресный формирователь не требует для своего функционирования повышенного напряжения питания, поэтому потребляемая им мощность невелика. Также повышается надежность формирователя, так как

уменьшается вероятность пробоя входных транзисторов.

В рабочем режиме на вход разрешения записи адресного формирователя подается сигнал О, по которому оба выхода мажоритарного элемента переходят в состояние Г или в состояние с высоким выходным сопротивлением независимо от сигналов на его информационных входах. В результате на выходы адресного формирователя по всем

разрядам проходит информация с его входов.

Формула изобретения Адресный формирователь, содержащий элементы И-НЕ первой группы, первые выходы которых являются адресными входами формирователя, элементы И-НЕ второй группы, выходы которых являются выходами формирователя, элементы НЕ, входы которых подключены к первым входам соответствующих элементов И-НЕ первой группы, выходы элементов НЕ подключены к первым входам соответствующих элементов И-НЕ второй группы, отличающийс я тем, что, с целью уменьшения энергопотребления и повышения надежности формирователя, он содержит мажоритарный элемент, входы которого подключены к первым входам элементов И-НЕ первой группы, управляющий вход мажоритарного элемента является входом разрешения программирования формирователя, прямой и инверсный выходы мажоритарного элемента подключены соответственно к вторым входам элементов И-НЕ второй группы

0 и к вторым входам элементов И-НЕ первой группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор | 1988 |

|

SU1596393A1 |

| Адресный формирователь | 1988 |

|

SU1596388A1 |

| Программируемый дешифратор | 1986 |

|

SU1399816A1 |

| Дешифратор | 1988 |

|

SU1594605A1 |

| Запоминающее устройство с резервированием | 1987 |

|

SU1411824A1 |

| Дешифратор | 1986 |

|

SU1399817A1 |

| Постоянное запоминающее устройство | 1987 |

|

SU1439684A1 |

| Устройство для программирования дешифратора | 1987 |

|

SU1531165A1 |

| Программатор для записи информации в полупроводниковые элементы памяти | 1985 |

|

SU1280449A2 |

| Программируемое постоянное запоминающее устройство | 1986 |

|

SU1372358A1 |

Изобретение относится к вычислительной технике, а именно к блока адресации накопителей информации, и может быть применено в запоминающих устройствах с резервированием. Цель изобретения - снижение энергопотребления и повышение надежности формирователя. Формирователь содержит элементы И-НЕ 1 и 2, мажоритарный элемент 3, элементы НЕ 4. Поставленная цель достигается за счет использования мажоритарного элемента 3, обеспечивающего необходимую для программирования адресных дешифраторов разность напряжений. При этом отпадает необходимость в повышенном питании элементов адресного формирователя. 3 ил.

Фиг.

| Патент США N; 4250570, кл | |||

| Станок для нарезания зубьев на гребнях | 1921 |

|

SU365A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-09-30—Публикация

1988-11-09—Подача