00

со со

Об

Изобретение относится к вычислительной технике и может быть использовано в микросхемах памяти с резервированием,

Цель изобретения - расширение области применения за счет возможности использования дешифратора в схемах памяти с резервированием.

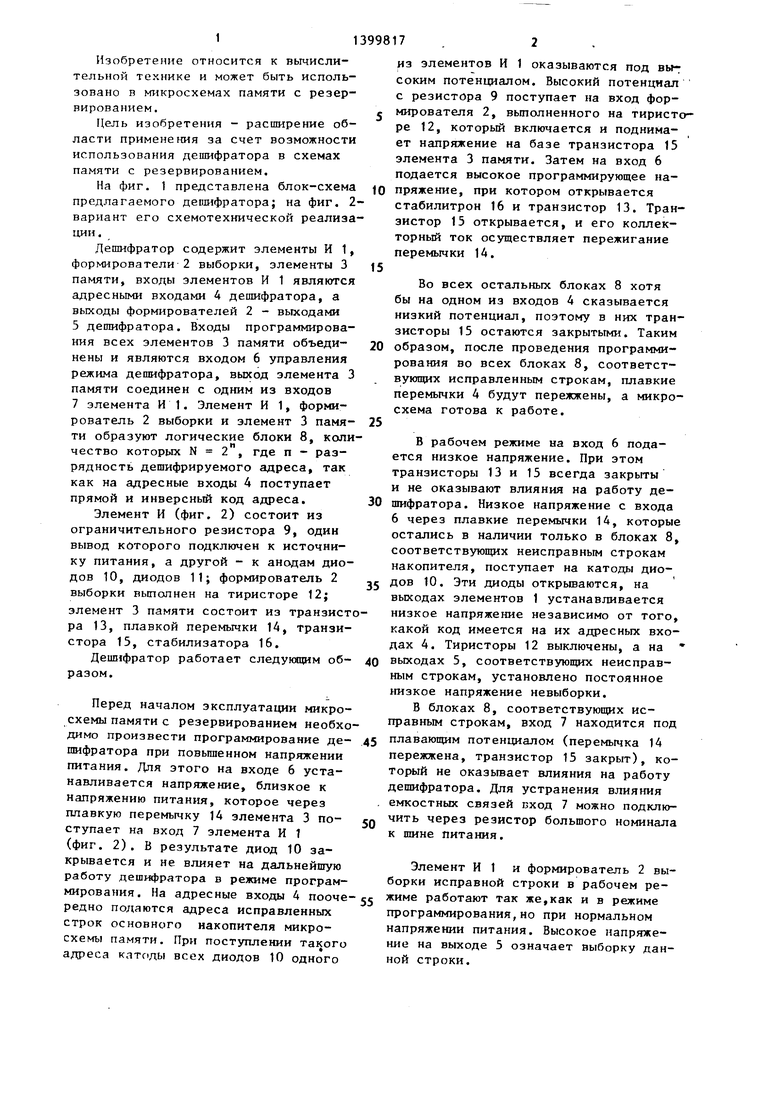

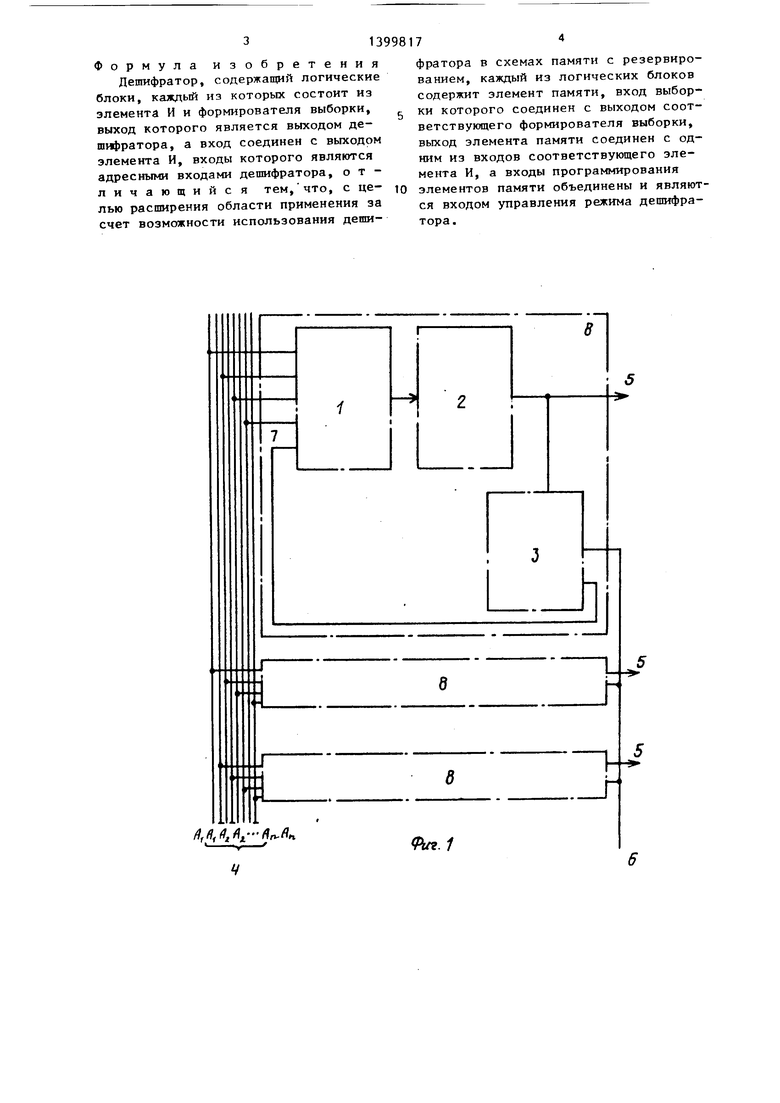

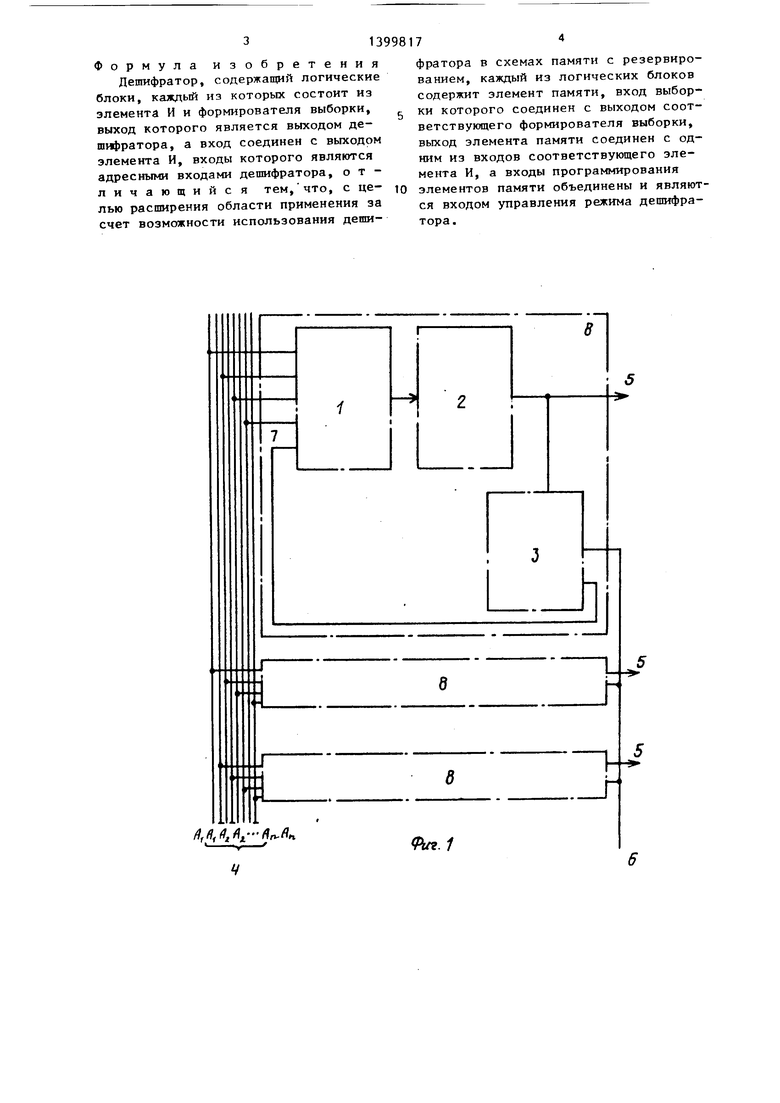

На фиг. 1 представлена блок-схема предлагаемого дешифратора; на фиг. 2 вариант его схемотехнической реализации,

Депшфратор содержит элементы И 1, формирователи 2 выборки, элементы 3 памяти, входы элементов И 1 являются адресными входами 4 дешифратора, а выходы формирователей 2 - выходами 5 депшфратора. Входы программирования всех элементов 3 памяти объеди- нены и являются входом 6 управления режима дешифратора, выход элемента 3 памяти соединен с одним из входов 7 элемента И 1. Элемент И 1, формирователь 2 выборки и элемент 3 памя- ти образуют логические блоки 8, количество которых N 2 , где п - разрядность дешифрируемого адреса, так как на адресные входы А поступает прямой и инверсный код адреса.

Элемент И (фиг. 2) состоит из ограничительного резистора 9, один вывод которого подключен к источнику питания, а другой - к анодам диодов 10, диодов 11; формирователь 2 выборки выполнен на тиристоре 12; элемент 3 памяти состоит из транзистра 13, плавкой перемычки 14, транзистора 15, стабилизатора 16.

Дешифратор работает следующим об- разом.

Перед началом эксплуатации микросхемы памяти с резервированием необходимо произвести программирование де- шифратора при повьштенном напряжении питания. Цля этого на входе 6 устанавливается напряжение, близкое к напряжению питания, которое через плавкую перемычку 14 элемента 3 по- ступает на вход 7 элемента И 1 (фиг. 2). В результате диод 10 закрывается и не влияет на дальнейшую работу дешифратора в режиме программирования. На адресные входы 4 пооче редно подаются адреса исправленных строк основного накопителя микросхемы памяти. При поступлении такого адреса клтоды всех диодов 10 одного

из элементов И 1 оказываются под вы-: соким потенциалом. Высокий потенциал с резистора 9 поступает на вход формирователя 2, вьшолненного на тиристоре 12, который включается и поднимает напряжение на базе транзистора 15 элемента 3 памяти. Затем на вход 6 подается высокое программирующее напряжение, при котором открывается стабилитрон 16 и транзистор 13. Транзистор 15 открывается, и его коллекторный ток осуществляет пережигание перемычки 14.

Во всех остальных блоках 8 хотя бы на одном из входов 4 сказывается низкий потенциал, поэтому в них транзисторы 15 остаются закрытыми. Таким образом, после проведения программирования во всех блоках 8, соответствующих исправленным строкам, плавкие перемычки 4 будут пережжены, а микросхема готова к работе.

В рабочем режиме на вход 6 подается низкое напряжение. При этом транзисторы 13 и 15 всегда закрыты и не оказывают влияния на работу дешифратора. Низкое напряжение с входа 6 через плавкие перемычки 14, которые остались в наличии только в блоках 8, соответствующих неисправным строкам накопителя, поступает на катоды диодов 10. Эти диоды открьшаются, на выходах элементов 1 устанавливается низкое напряжение независимо от того, какой код имеется на их адресных входах 4. Тиристоры 12 выключены, а на выходах 5, соответствующих неисправным строкам, установлено постоянное низкое напряжение невыборки.

В блоках 8, соответствующих исправным строкам, вход 7 находится под

плавающим потенциалом (перемычка 14 пережжена, транзистор 15 закрыт), который не оказьшает влияния на работу дешифратора. Для устранения влияния емкостных связей сход 7 можно подключить через резистор большого номинала к щине питания.

Элемент И 1 и формирователь 2 выборки исправной строки в рабочем режиме работают так же,как и в режиме программирования,но при нормальном напряжении питания. Высокое напряжение на выходе 5 означает выборку данной строки.

313998

Формула изобретения Дешифратор, содержащий логические блоки, каждый из которых состоит из элемента И и формирователя выборки, выход которого является выходом дешифратора, а вход соединен с выходом элемента И, входы которого являются адресными входами дешифратора, отличающийся тем, что, с це- ю лью расширения области применения за счет возможности использования деши74

фратора в схемах памяти с резервированием, каждый из логических блоков содержит элемент памяти, вход выборки которого соединен с выходом соответствующего формирователя выборки, выход элемента памяти соединен с одним из входов соответствующего элемента И, а входы программирования элементов памяти объединены и являются входом управления режима дешифратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор | 1988 |

|

SU1596393A1 |

| Адресный формирователь | 1988 |

|

SU1596388A1 |

| Дешифратор | 1988 |

|

SU1594605A1 |

| Адресный формирователь | 1988 |

|

SU1596389A1 |

| Программируемый дешифратор | 1986 |

|

SU1399816A1 |

| Запоминающее устройство с резервированием | 1987 |

|

SU1411824A1 |

| Программируемое постоянное запоминающее устройство | 1988 |

|

SU1635218A1 |

| Постоянное запоминающее устройство | 1985 |

|

SU1305775A1 |

| Оперативное запоминающее устройство с резервированием строк | 1986 |

|

SU1462426A1 |

| Постоянное запоминающее устройство | 1987 |

|

SU1439684A1 |

Изобретение относится к вычислительной технике и может быть использовано в микросхемах памяти с резервированием. Цель изобретения - расширение области применения за счет использования дешифраторов в схемах памяти с резервированием. Поставленная цель достигается за счет введения в каждый логический блок элемента памяти (ЭП). Использование дешифратора в ППЗУ позволяет осуществить постоянную блокировку части формирователей выборки, выходы которых связаны со строками или разрядами с дефектными ЭП. Информация будет считываться из резервных частей накопителя. 2 ил.

г 1 t

6

ff.i

.AjAiAnAn

| Патент США 4365319, кл | |||

| Станок для нарезания зубьев на гребнях | 1921 |

|

SU365A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| Патент США N 4130889, кл | |||

| Станок для нарезания зубьев на гребнях | 1921 |

|

SU365A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

Авторы

Даты

1988-05-30—Публикация

1986-12-01—Подача