(21)4618100/24

(22)09.11.88

(46) 15.03.91. Бюл. № 10 (72) С.А.Фастов, А.А.Львович и Ю.И.Щетинин

(53)681.327.6 (088.8)

(56)Авторское свидетельство СССР № 1305775, кл. СПС 17/00, 1985.

Bipolar Memory Generic PROM series Amd Inc., 1980, c. 5-9.

(54)ПРОГРАММИРУЕМОЕ ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

(57)Изобретение относится к вычислительной технике и может быть использовано при построении БИС программируемых постоянных запоминающих . устройств (ПИЗУ). Целью изобретения является повышение достоверности контроля устройства. Поставленная цель достигается за счет того, что входы блокировки дешифраторов слов и разрядов являются первым и вторым входами контроля устройства соответственно, а последний выход блока программирования соединен с входами блокировки формирователей выборки слов. Устройство позволяет с высокой точностью и достоверностью контролировать токи утечки накопителя ППЗУ в реальном режиме работы накопителя, 1 ил .

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1985 |

|

SU1305775A1 |

| Запоминающее устройство с резервированием | 1987 |

|

SU1411824A1 |

| Дешифратор | 1986 |

|

SU1399817A1 |

| Программируемое постоянное запоминающее устройство | 1986 |

|

SU1372358A1 |

| Постоянное запоминающее устройство | 1987 |

|

SU1439684A1 |

| Программируемый дешифратор | 1986 |

|

SU1399816A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ ИНФОРМАЦИИ В ПРОГРАММИРУЕМОЕ ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1988 |

|

SU1554646A1 |

| ПРОГРАММИРУЕМОЕ УСТРОЙСТВО СОПРЯЖЕНИЯ С ПОВЫШЕННОЙ НАГРУЗОЧНОЙ СПОСОБНОСТЬЮ | 1992 |

|

RU2039374C1 |

| НАКОПИТЕЛЬ ЭЛЕКТРИЧЕСКИ ПРОГРАММИРУЕМОГО ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1991 |

|

RU2028676C1 |

| Дешифратор | 1988 |

|

SU1596393A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении БИС программируемых постоянных запоминающих устройств (ППЗУ).

Цель изобретения - повышение достоверности контроля устройства.

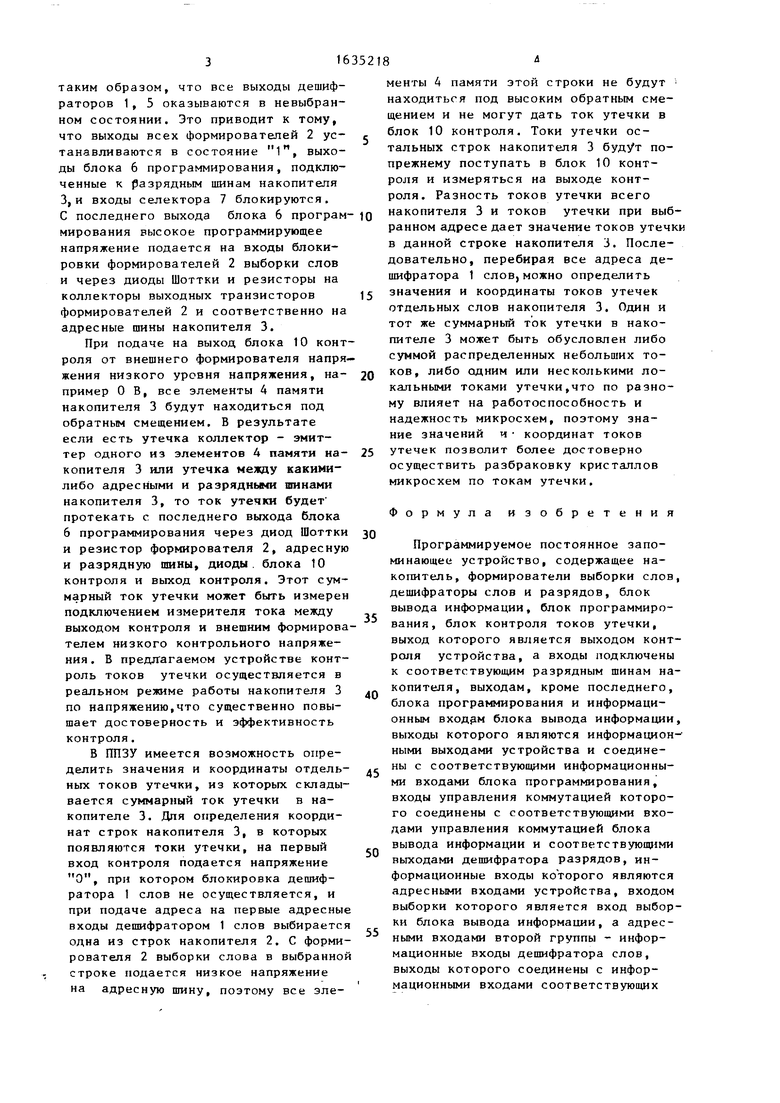

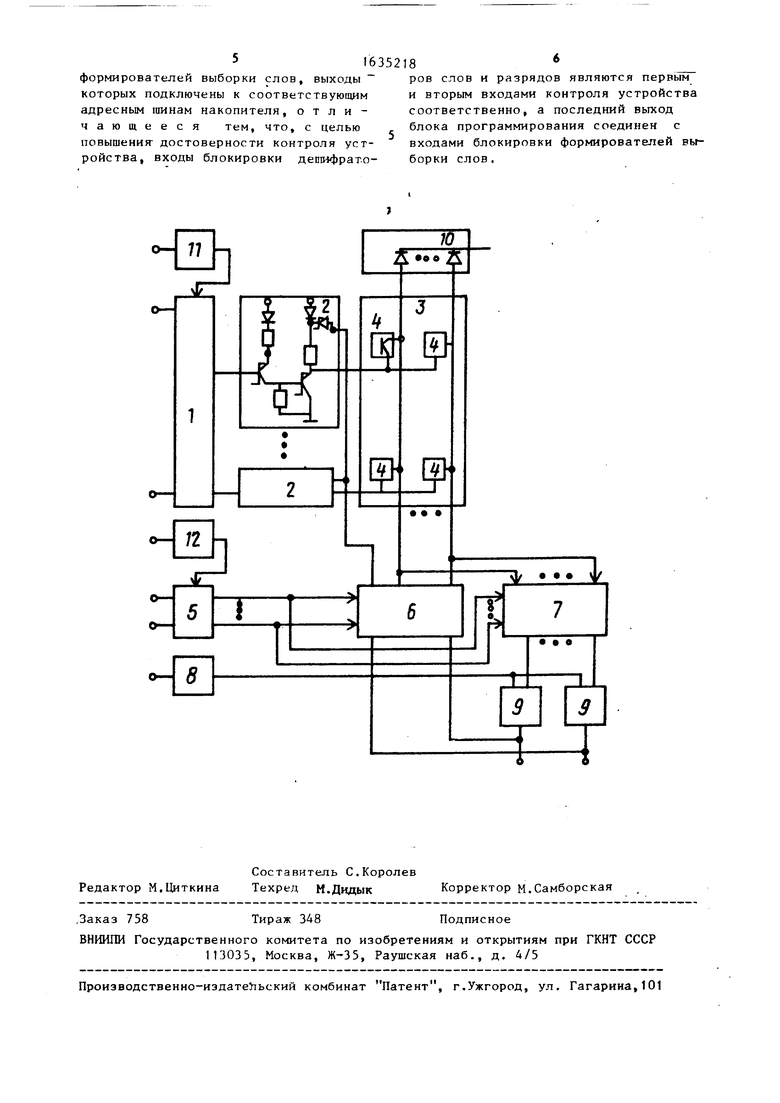

На чертеже представлена схема программируемого постоянного запоминающего устройства.

Программируемое постоянное запоминающее устройство содержит дешифратор 1 слов, формирователи 2 выборки слов, накопитель 3, состоящий из элементов 4 памяти, дешифратор 5 разрядов, блок 6 программирования, блок вывода информации, состоящий из се-) лектора 7, формирователя 8 выборки

и выходных усилителей 9, блок 10 контроля токов утечки. На чертеже также показаны формирователи 11, 12 блокировки дешифраторов 1, 5.

Устройство работает следующим образом.

Для измерения токов утечки матрицы на ППЗУ задают режим программирования, заключающийся в подаче высокого напряжения питания (8 В) и высоких программируемых напряжений (20 В) на вход формирователя 8 выборки и соответствующий выход устройства, а на первый и второй входы контроля подают напряжение 1. При наличии на входе формирователей 11, 12 блокировки дешифраторов 1 , 5 слов и разрядов напряжения 1 они блокируют их работу

рт

|к

00

таким образом, что все выходы дешифраторов 1, 5 оказываются в невыбранном состоянии. Это приводит к тому, что выходы всех формирователей 2 ус- танавливаются в состояние 1, выходы блока 6 программирования, подключенные к разрядным шинам накопителя 3,и входы селектора 7 блокируются. С последнего выхода блока 6 програм- мирования высокое программирующее напряжение подается на входы блокировки формирователей 2 выборки слов и через диоды Шоттки и резисторы на коллекторы выходных транзисторов формирователей 2 и соответственно на адресные шины накопителя 3.

При подаче на выход блока 10 контроля от внешнего формирователя напряжения низкого уровня напряжения, на- пример О В, все элементы 4 памяти накопителя 3 будут находиться под обратным смещением. В результате если есть утечка коллектор - эмиттер одного из элементов 4 памяти накопителя 3 или утечка между какими- либо адресными и разрядными шинами накопителя 3, то ток утечки будет протекать с последнего выхода блока 6 программирования через диод Шоттки и резистор формирователя 2, адресную и разрядную шины, диоды, блока 10 контроля и выход контроля. Этот суммарный ток утечки может быть измерен подключением измерителя тока между выходом контроля и внешним формирователем низкого контрольного напряжения. В предлагаемом устройстве контроль токов утечки осуществляется в реальном режиме работы накопителя 3 по напряжению,что существенно повышает достоверность и эффективность контроля.

В ППЗУ имеется возможность определить значения и координаты отдельных токов утечки, из которых складывается суммарный ток утечки в накопителе 3. Для определения координат строк накопителя 3, в которых появляются токи утечки, на первый вход контроля подается напряжение О, при котором блокировка дешифратора 1 слов не осуществляется, и при подаче адреса на первые адресные входы дешифратором 1 слов выбирается одна из строк накопителя 2. С формирователя 2 выборки слова в выбранной строке подается низкое напряжение на адресную шину, поэтому все эле

5

5

0

0

5

0

5

0

5

менты 4 памяти этой строки не будут находиться под высоким обратным смещением и не могут дать ток утечки в блок 10 контроля. Токи утечки остальных строк накопителя 3 будУт по- прежнему поступать в блок 10 контроля и измеряться на выходе контроля. Разность токов утечки всего накопителя 3 и токов утечки при выбранном адресе дает значение токов утечки в данной строке накопителя 3. Последовательно, перебирая все адреса дешифратора 1 слов,можно определить значения и координаты токов утечек отдельных слов накопителя 3. Один и тот же суммарный ток утечки в накопителе 3 может быть обусловлен либо суммой распределенных небольших токов, либо одним или несколькими локальными токами утечки,что по разному влияет на работоспособность и надежность микросхем, поэтому знание значений ч координат токов утечек позволит более достоверно осуществить разбраковку кристаллов микросхем по токам утечки.

Формула изобретения

Программируемое постоянное запоминающее устройство, содержащее накопитель, формирователи выборки слов, дешифраторы слов и разрядов, блок вывода информации, блок программирования, блок контроля токов утечки, выход которого является выходом контроля устройства, а входы подключены к соответствующим разрядным шинам накопителя, выходам, кроме последнего, блока программирования и информационным входам блока вывода информации, выходы которого являются информацией-1 ными выходами устройства и соединены с соответствующими информационными входами блока программирования, входы управления коммутацией которого соединены с соответствующими входами управления коммутацией блока вывода информации и соответствующими выходами дешифратора разрядов, информационные входы которого являются адресными входами устройства, входом выборки которого является вход выборки блока вывода информации, а адресными входами второй группы - информационные входы дешифратора слов, выходы которого соединены с информационными входами соответствующих

формирователей выборки слов, выходы которых подключены к соответствующим адресным шинам накопителя, отличающееся тем, что, с целью повышения- достоверности контроля устройства, входы блокировки дешифрато1635218

ров слов и разрядов являются первым и вторым входами контроля устройства соответственно, а последний выход блока программирования соединен с входами блокировки формирователей выборки слов .

Авторы

Даты

1991-03-15—Публикация

1988-11-09—Подача