Аа

(R/zf

(Л

Изобретение относится к вьтисли- тельной технике, а именно к дешифраторам адреса микросхем памяти, и может быть использовано при проектировании микросхем памяти с резервированием.

Цель изобретения - повьппение надежности устройства и быстродействия при программировании дешифратора.

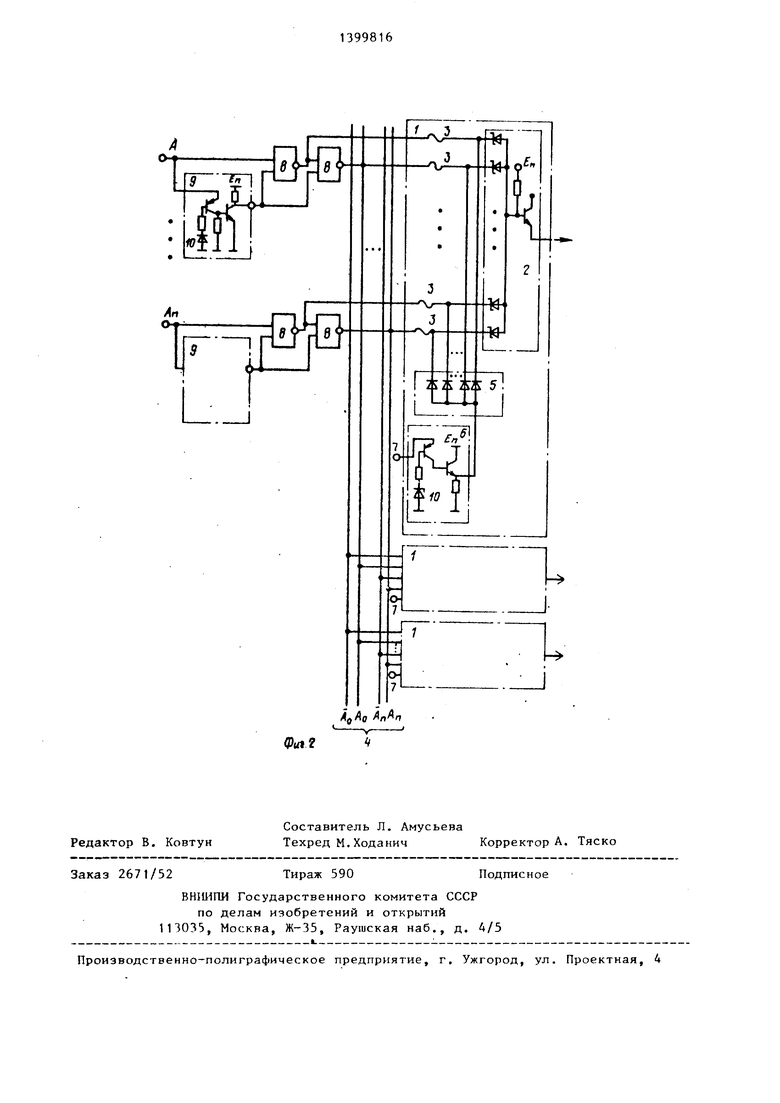

На фиг. 1 представлена блок-схема программируемого дешифратора; на фиг. 2 - вариант ее схемотехнической реализации.

Дешифратор содержит логические ячейки 1, каждая из которых состоит из элемента 2 И, элементов 3 памяти (плавкие перемычки), одни выводы которых подключены к соответствующим адресным шинам А, развязывающего элемента 5, формирователя 6 напряжения программирования, вход которого является входом 7 разрешения программирования ячейки 1. Дешифратор также содержит группы элементов И-НЕ 8 и элементы НЕ 9.

В микросхеме памяти с резервированием при поступлении на адресные входы адреса неисправной в основном накопителе строки основной дешифратор не должен выбирать строку по данному адресу. Вместо этого резервный программируемый дешифратор должен выбрать из резервного накопителя строку, соответствующую неисправной в основном накопителе. Для того, что бы осуществить эти операции, резервный дешифратор должен быть предварительно запрограммирован, т.е. в его ячейке 1 записаны адреса неисправных строк основного накопителя. Запись адресов производится путем пережигания плавких перемычек 3 при повышенном напряжении питания. Только в это случае могут быть включены элементы НЕ 9 и формирователи 6, так как стабилитроны 10 на их входах рассчитаны на напряжение, превьпиающее напряжени питания рабочего режима.

Каждому адресному входу соответствуют две перемычки 3 - прямая и

,,„0 ДJJд того, чтобы записать

О

инверсная в данном разряде

надо пережечь

прямую перемычку 3 и наоборот. При появлении О на адресном входе данного разряда на выходе первого эле- , мента И-НЕ 8 данной группы устацоптгг- ся 1, а на 1П.ГХОДО второго - О, что ознлч.чот 11 феч ;иг;111ие прямой

0

5

0

5

0

5

0

5

0

5

перемычки 3, связанной с вторым элементом И-НЕ 8. При наличии 1 на адресном входе пережигается перемычка 3, связанная с первым элементом И-НЕ 8 группы. На всех перемычках 3, относящихся к другим разрядам адреса, должен быть устаноапен высокий потенциал, так как в один момент времени может пережигаться только одна перемычка 3 для ограничения рассеиваемой мощности. Для этого на остальные адресные входы подается напряжение, значительно превышающее уровень 1. В результате на выходах элементов 9 этих разрядов устанавливается уровень О, переводящий и первые, и вторые элементы И-НЕ 8 в состояние 1 на выходе.

Пережигание перемычки 3, у которой установлен низкий потенциал на втором выводе, производится по сигналу разрешения пережигания ячейки 1, который подается на вход 7 той ячейки 1, в которой производится пережигание перемычки 3. При этом формтфователь 6, через элемент 5 задает высокие напряжения на первых выводах всех перемычек 3 данной ячейки 1. На вторых выводах перемычек 3, кроме пережигаемой, элементами И-НЕ б также установлен высокий потенциал, поэтому сгорит только одна перемычка 3.

В предлагаемом дешифраторе снижены требования к пробивному напряжению выходного каскада, формирующего уровень 1 на выходе элемента И-НЕ, так как в режиме пережигания выходы всех невыбранных для пережигания элементов И-НЕ 8 переводятся в состояние с высоким потенциалом. Это исключает возможность пробоя выходных элементов в каскаде, формирующем уровень 1 на выходе элемента И-НЕ, благодаря чему повышается надежность дешифратора. По окончании пережигания перемычек первой группы И-НЕ аналогичным образом пережигается одна из перемычек 3 следующей группы и т.д. до тех пор, пока во всех ячейках 1 на каждый адресный вход не останется по одной перемычке 3. I

В рабочем режиме дешифратор функционирует при напряжении питания, обеспечивающем закрытое состояние стабилитронов 10, поэтому состояние входов 7 может быть произвольным. На вторых входах DCPX элементов 8 ус- таиаплип/ается 1, а на пходе элемрнта 5 - О. Элементы 5, 6, 9 в дальнейшей работе дешифратора не участвуют. Входы элементов И 2 оказываются подключенными через плавкие пере- мычки 3 к адресным шинам 4 в соответствии с кодами адресов, при появлении которых на адресных входах возбуждается один из выходов -программируемого дешифратора. Остальные входы элементов И 2 оказываются неподключенными, что эквивалентно установлению на них 1, поэтому они не окажут влияния на дальнейшую работу дешифратора.

При появлении на адресных входах кода адреса, записанного в одной из ячеек 1, на всех входах элемента 2 И подключенных через перемычки 3 к адресным шинам 4, установится 1. На выходе элемента 2 И этой ячейки также установится 1, что означает выборку

Входы элементов И 2 и остальных ячеек подключены перемычками 3 к адресным шинам А в соответствии с дру- гим кодом. Поэтому хотя бы один из входов каждого оставшегося элемента И 2 будет иметь низкий потенциал, На выходах этих элементов И 2 также установится низкий потенциал, означа- кщий невыборку.

Таким образом, программируемый дешифратор производит выборку адресной строки из нескольких в соответствии с записанным в нем кодом и кодом по-

ступающего адреса.

Преимуществом предлагаемого программируемого дешифратора является повьш1енная надежность и скорость программирования, получаемая за счет вве

денмя групп двухвходовых элементов ч-НЕ 8 и элементов НЕ 9.

Формула изобретения

Программируемый дешифратор, содер- жапцп логические ячейки, каждая из которых состоит из элемента И, выход которого является выходом дешифратора элементов памяти, выполненных на плавких перемычках, первые выводы которых соединены с соответствующими входами элемента И, а вторые вьгеоды соединены с информационными входами логических ячеек и подключены к адресным шинам дешифратора развязывающего элемента, выходы которого соединены с соответствующими входами элемента И, формирователя напряжения программирования, выход которого соединен с входом развязывающего элемента, а вход является входом разрешения программирования логической ячейки дешифратора, отличающий с я тем, что, с целью повьппения надежности и быстродействия дешифратора, в него введены элементы НЕ и группы элементов И-НЕ, выходы которых подключены к соответствующим информационным входам логических ячеек, первые входы первых элементов И-НЕ каждой группы соединены с входом элемента НЕ и являются адресными входами дешифратора, а первые входы вторых элементов И-НЕ каждой группы соединены с выходами первых элементов И-НЕ данной группы, вторые входы элементов И-НЕ каждой группы соединены с выходом соответствующего элемента НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор | 1988 |

|

SU1596393A1 |

| Адресный формирователь | 1988 |

|

SU1596388A1 |

| Дешифратор | 1988 |

|

SU1594605A1 |

| Запоминающее устройство с резервированием | 1987 |

|

SU1411824A1 |

| Адресный формирователь | 1988 |

|

SU1596389A1 |

| Постоянное запоминающее устройство | 1987 |

|

SU1439684A1 |

| Дешифратор | 1986 |

|

SU1399817A1 |

| Устройство для программирования дешифратора | 1987 |

|

SU1531165A1 |

| Резервированное запоминающее устройство с самоконтролем | 1982 |

|

SU1070609A1 |

| Программируемое постоянное запоминающее устройство | 1981 |

|

SU999111A1 |

Изобретение относится к вычислительной технике, а именно к дешифраторам адреса микросхем памяти, и может быть использовано при проектировании микросхем памяти с резервированием. Целью изобретения является повышение надежности и быстродействия дешифратора. Поставленная цель достигается за счет введения элементов НЕ 9 и группы элементов И-НЕ 8. В предложенном дешифраторе паразитная емкость каждой шины перезаряжается с соответствующим элементом И-НЕ 8, поэтому повышение напряжения на первых выводах перемычек 3 происходит быстрее. 2 ил.

An

L.

Х,,Ло

Редактор В. Ковтун

Составитель Л. Амусьева

Техред М.Ходанич Корректор А. Тяско

Заказ 2671/52

Тираж 590

ВН1ШГШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

| Аппарат для фотографического копирования | 1931 |

|

SU27285A1 |

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

| Патент США № 4250570, кл | |||

| Станок для нарезания зубьев на гребнях | 1921 |

|

SU365A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

Авторы

Даты

1988-05-30—Публикация

1986-12-01—Подача