Изобретение относится к вычислительной технике, а именно к дешифраторам для запоминалощих устройств с р ез ервированием.

Цель изобретения - снижение потребляемой мощности дешифратора.

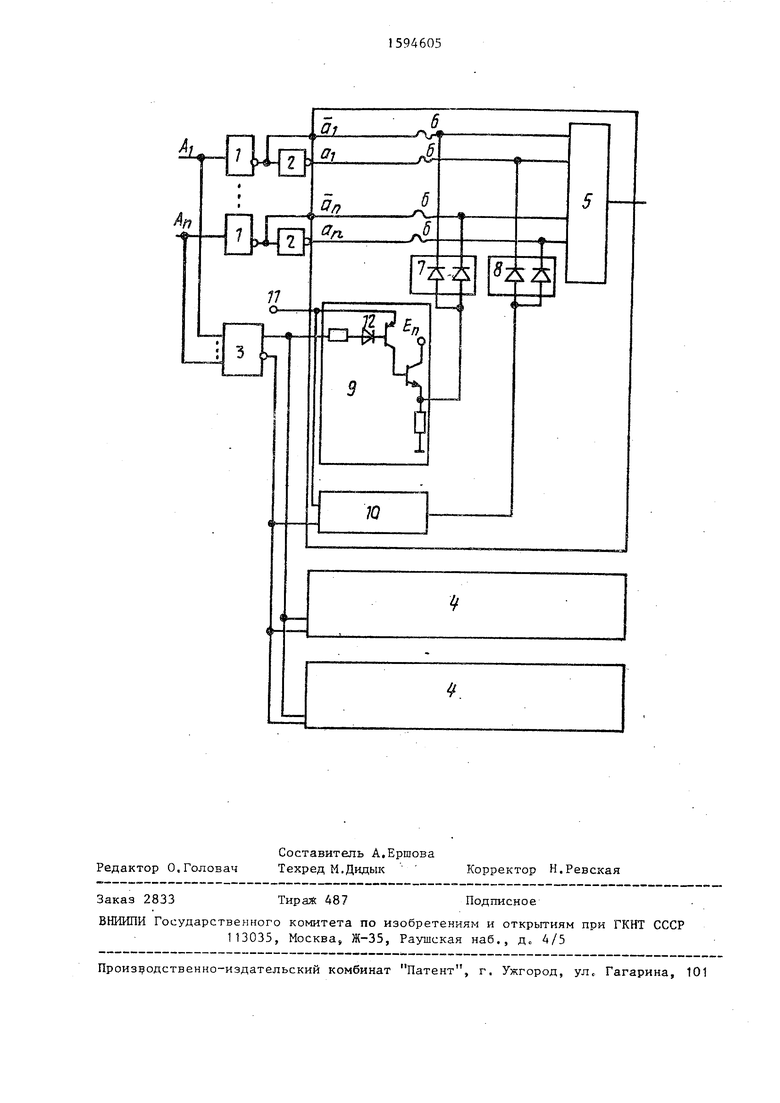

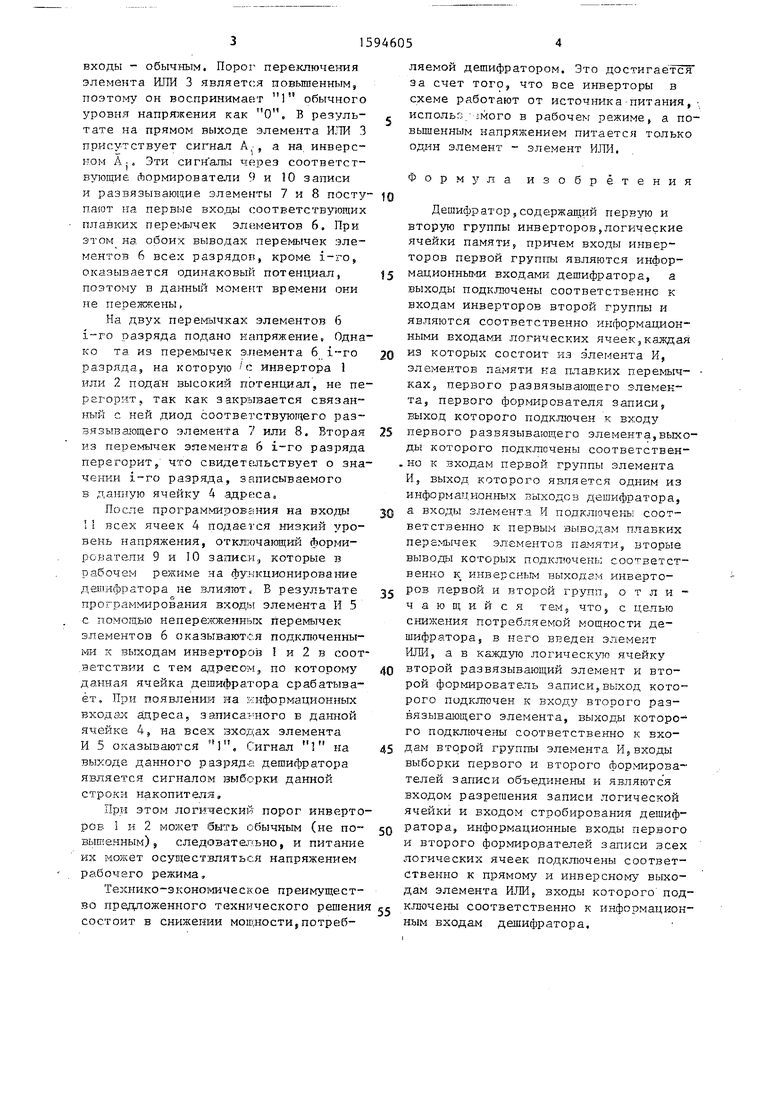

На чертеже приведена структурная схема дешифратора.

Дешифратор содержит первые 1 и вторые 2 инверторы, элемент ИЛИ 3 и логические ячейки 4. Каждая логическая ячейка 4 состоит из элемента И 5, элементов 6 памяти на плавких перемычках, двух развязывающих элементов 7 и 8, двух формирователей 9 и 10 записи и имеет вход 11 разрешения записи ячейки. Формирователи 9 и 10 содержат стабилитрон 12.

Предложенный дешифратор является резервным дешифратором микросхемы памяти и предназначен для выборки из резервного накопителя строк или столбцов. Для установления соответствия между адресом неисправной строки основного накопителя и выбираемой резервной строкой в соответствующую логическую ячейку 4 дешифратора необходимо записать адре- неисправной строки основного накопителя путем пережигания плавких перемычек элементов 6. Перемычки элементов 6 пережигаются большим током, поэтом в каждый момент времени может пережигат-ься только одна из них. Пережигание перемычек элементов 6 каж,дой ячейки 4 производится последовательно, например, начиная с разряда А, и кончая разрядом А. Для определенности рассмотрим работу устройства при пережигании перемычек 6, соответствующей разряду А.. В Э.ТОМ случае на Информационный вход .А. подается логический сигнал,соответствующий значению i-ro разряда записываемого в ячейку 4 адреса. На все остальные входы, кроме i-ro,подаются сигналы, инверсные сигналу на входе А.. Уровень напряжения лог.

1, подаваемый на вход А., должен быть повьш1енным, а на все остальные

с S

сд

4 05 О СЛ

входы - обычным. Порог переключе1Ч ия элемента ИЛИ 3 является повышенным, поэтому он воспринимакт 1 обычного уровня напрюкения как О. В результате на прямом выходе элемента ИЛИ 3 присутствует сигнап А,, а на инверсном AJ, Эти сигн ал1 1 через соответствующие Лормироватепи 9 и 10 записи и развязывающие элементы 7 и 8 поступают на первые входа соответствующих плавких перемычек элвментов 6, При этом на обоих выводах перемычек элементов 6 всех разрядов, кроме i-ro, оказывается одинаковый потенциал, поэтому в данньй момент времени они не пережжены,

На двух перемычках элементов 6 i--ro разряда подано напряжение. Однако та из пере1Ф1чек элемента б i-ro разряда, на которую - с инвертора 1 или 2 пода н высокий потенциал, не перегорит, так как закрывается связанный с ней диод соответствующего развязывающего элемента 7 или 8, Вторая из перемычек эпемента 6 i-ro разряда перегоритS что свидвтЕ льствует о значении разряда, записываемого в данную ячейку 4 адреса.

После программироЕ ания на входы 11 всех ячеек 4 подается низкий уровень напряжения, отключающий формирователи 9 и 10 записи, которые в рабочем режиме на функционирование дешифратора не влияют В результате программирования входы элемента И 5 с помощью непережженных перемычек элементов 6 оказываются подключенны- м-и к выходам инверторо з и 2 в соответствии с тем a;qpenoM, по которому данная ячейка дешифратора срабатывает. При появлении на информационных входэ:; адреса, записанного в данной ячейке 4, на всех входах элемента И 5 оказываются 1. Сигнал 1 на выходе данного разряда дешифратора является сигналом ззыборки данной строки накопителя.

При этом логический порог инверторов 1 и 2 может быть се)ычным (не повышенным), следовательно, и питание их может осун ествляться напряжением рабочего режима,

Технико эконо1 жческое преимущество предложенного технического решения состоит в снижении мощности,потребляемой дешифратором. Это достигае тЗя за счет того, что все инверторы в схеме работают от источника питания, испольг; шого в рабочем режиме, а по- вьшенным напряжением питается только один элемент - элемент ИЛИ,

Формула изобр

е т е н и я

0

5

5

5

0

5

0

5

Дешифратор5содержащий первую и вторую группы инверторов,логические ячейки памяти} причем входы инверторов первой группы являются инфор- мaциoнны й входами дешифратора, а выходы подключены соответственно к входам инверторов второй группы и являются соответственно информационными входами логических ячеек,каждая из которых состоит из элемента И, элементоБ памяти на плавких перемыч- кахэ первого развязываощего элемента, первого формирователя записи, выход которого подключен к входу первого развязывающего элемента,выходы которого подключены соответствен- .но к входам первой группы элемента И, выход которого якляется одним из информационных выходов дешифратора, а входы элемента И подключены соответственно к первым выводам плавких перемычек элементов памяти, вторые выводы которых подключены соответственно к инверсным выходам инверторов первой и второй групп, отличающийся TEMj что, с целью снижения потребляемой мощности дешифратора, в него внеден элемент ИЛИ, а в каждую логическую ячейку второй развязывающий элемент и второй формирователь записи,выход которого подключен к входу второго раз- вязывшощего элемента, выходы которого подключены соответственно к входам второй группы элемента И входы выборки первого и второго формирователей записи объединены и являются входом разрешения записи логической ячейки и входом стробирования дешиф- ратора, информационные входы первого и второго формирователей записи всех логических ячеек подключены соответственно к прямому и инверсному выходам элемента ИЛИ,, входы которого подключены соответственно к информационным входам дешифратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор | 1988 |

|

SU1596393A1 |

| Адресный формирователь | 1988 |

|

SU1596388A1 |

| Программируемый дешифратор | 1986 |

|

SU1399816A1 |

| Адресный формирователь | 1988 |

|

SU1596389A1 |

| Запоминающее устройство с резервированием | 1987 |

|

SU1411824A1 |

| Постоянное запоминающее устройство | 1987 |

|

SU1439684A1 |

| Дешифратор | 1986 |

|

SU1399817A1 |

| Устройство для программирования дешифратора | 1987 |

|

SU1531165A1 |

| Запоминающее устройство | 1983 |

|

SU1112412A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

Изобретение относится к вычислительной технике, а именно к дешифраторам для запоминающих устройств с резервированием. Цель изобретения - снижение потребляемой мощности дешифратора. Все инверторы в схеме работают от источника питания, используемого в рабочем режиме, а повышенным напряжением питается только один элемент - элемент ИЛИ. 1 ил.

| Программируемый дешифратор | 1986 |

|

SU1399816A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Патент США № 4250570, кл | |||

| Станок для нарезания зубьев на гребнях | 1921 |

|

SU365A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

Авторы

Даты

1990-09-23—Публикация

1988-11-09—Подача