Изобретение относится к автоматике и вычислительной технике и может

: быть использовано при проектировании асинхронных регистров сдвига.

I Цель изобретения - упрощение и

повьшение быстродействия регистра.

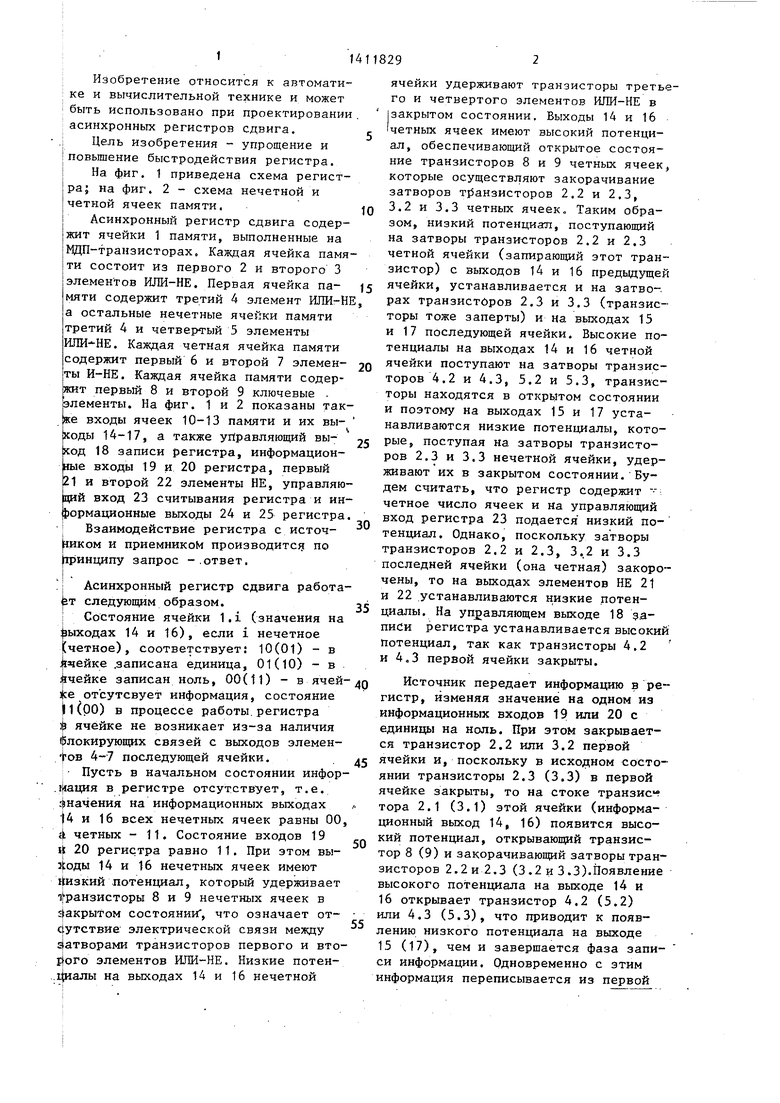

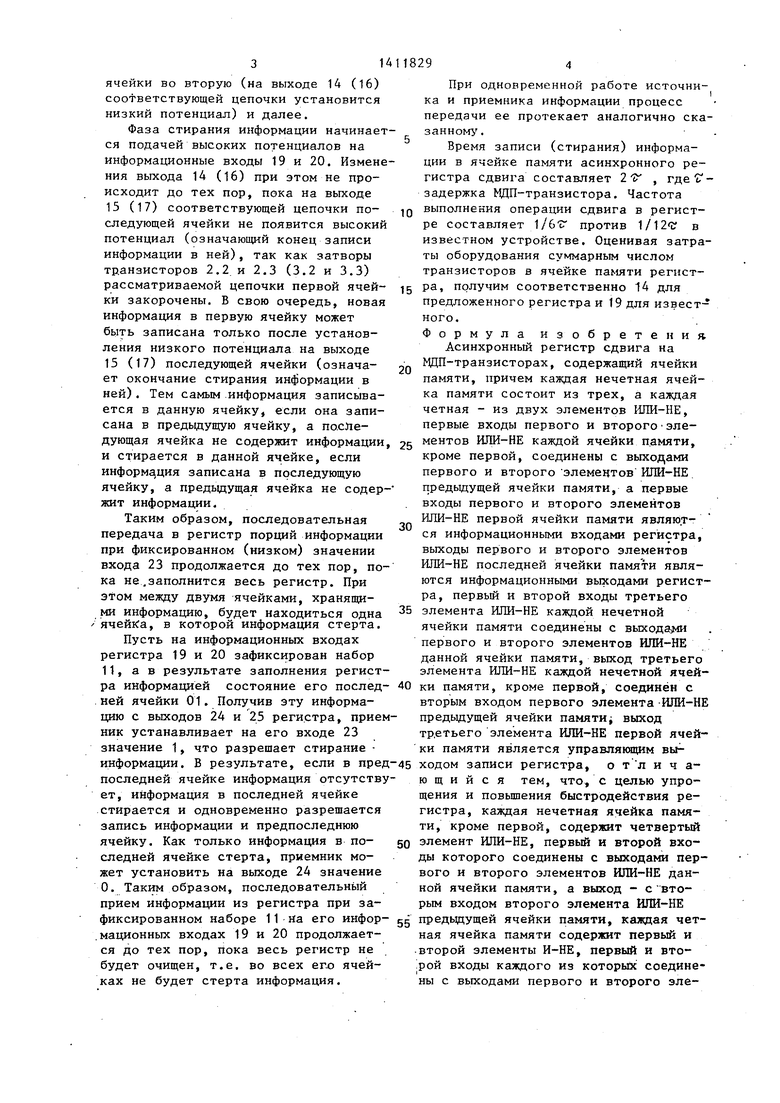

I На фиг. 1 приведена схема регистра; на фиг. 2 - схема нечетной и четной ячеек памяти.

Асинхронный регистр сдвига содержит ячейки 1 памяти, выполненные на МДП-транзисторах. Каждая ячейка памяти состоит из первого 2 и второго 3 элементов ИЛИ-НЕ. Первая ячейка па- мяти содержит третий 4 элемент ИЛИ-Н а остальные нечетные ячейки памяти третий 4 и четвертый 5 элементы ИЛИ-НЕ. Каждая четная ячейка памяти содержит первый 6 и второй 7 элемен- ты И-НЕ. Каждая ячейка памяти содержит первый 8 и второй 9 ключевые . элементы. На фиг. 1 и 2 показаны также входы ячеек 10-13 памяти и их выходы 14-17, а также уйравляющий вы- ход 18 записи регистра, информационные входы 19 и 20 регистра, первый 21 и второй 22 элементы НЕ, управляю- ций вход 23 считывания регистра и ин- ||ормационные выходы 24 и 25 регистра

Взаимодействие регистра с источником и приемником производите по принципу запрос -.ответ.

Г

k

Асинхронный регистр сдвига работа- т следующим образом.

I Состояние ячейки 1.i (значения на :зыходах 14 и 16), если i нечетное четное), соответствует: 10(01) - в ячейке .записана единица, 01(10) - в Ячейке записан ноль, 00(11) - в ячей е отсутсвует информация, состояние || 1 (рО) в процессе работы, регистра 1 ячейке не возникает из-за наличия (локирующих связей с выходов элемен- foB 4-7 последующей ячейки. .

Пусть в начальном состоянии инфор- .1|1ация в регистре отсутствует, т.е. ; начения на информационных выходах (4 и 16 всех нечетных ячеек равны 00 4 четных - 11. Состояние входов 19 1 20 регистра равно 11. При этом вы- зроды 14 и 16 нечетных ячеек имеют 1 изкий потенциал, который удерживает 1 ранзисторы 8 и 9 нечетных ячеек в Закрытом состоянии, что означает от- 4утствие электрической связи между атворами транзисторов первого и вто- pioro элементов ИЛИ-НЕ. Низкие потен- ,4иалы на выходах 14 и 16 нечетной

с

Q

5 0 5

0

5

р д

0

5

ячейки удеряшвают транзисторы третьего и четвертого элементов ИЛИ-НЕ в закрытом состоянии. Выходы 14 и 16 четных ячеек имеют высокий потенциал, обеспечивающий открытое состояние транзисторов 8 и 9 четных ячеек., которые осуществляют закорачивание затворов Т15анзисторов 2.2 и 2.3, 3.2 и 3.3 четных ячеек„ Таким образом, низкий потенциал, поступающий на затворы транзи ;торов 2.2 и 2.3 четной ячейки (запирающий этот транзистор) с выходов 14 и 16 предыдущей ячейки, устанавливается и на затворах транзисторов 2.3 и 3.3 (транзисторы тоже заперты) и на выходах 15 и 17 последующей ячейки. Высокие потенциалы на выходах 14 и 16 четной ячейки поступают на затворы транзисторов 4.2 и 4.3, 5.2 и 5.3, транзисторы находятся в открытом состоянии и поэтому на выходах 15 и 17 устанавливаются низкие потенциалы, которые, поступая на затворы транзисторов 2.3 и 3.3 нечетной ячейки, удерживают их в закрытом состоянии. Будем считать, что регистр содержит - - четное число ячеек и на управляющий вход регистра 23 подается низкий потенциал. Однако, поскольку затворы транзисторов 2.2 и 2.3, 3..2 и 3.3 последней ячейки (она четная) закорочены, то на выходах элементов НЕ 21 и 22 .устанавливаются низкие потенциалы. На управляющем выходе 18 записи регистра устанавливается высокий Потенциал, так как транзисторы 4.2 и 4,3 первой ячейки закрыты.

Источник передает информацию в регистр, изменяя значение на одном из информационных входов 1 или 20 с единицы на ноль. При этом закрывается транзистор 2,2 или 3.2 первой ячейки и, поскольку в исходном состоянии транзисторы 2.3 (3.3) в первой ячейке закрыты, то на стоке транзис тора 2.1 (3.1) этой ячейки (информационный выход 14, 16) появится высокий потенциал, открывающий транзистор 8 (9) и закорачивающий затворы транзисторов 2,2 и 2.3 (3.2 и 3.3).Появление высокого потенциала на выходе 14 и 16 открывает транзистор 4.2 (5.2) или 4.3 (5.3), что приводит к появлению низкого потенциала на выходе 15 (17), чем и завершается фаза записи информации. Одновременно с этим информация переписывается из первой

314

ячейки во вторую (на выходе 14 (16) соответствующей цепочки установится низкий потенциал) и далее.

Фаза стирания информации начинается подачей высоких потенциалов на информационные входы 19 и 20. Изменения выхода 14 (16) при этом не происходит до тех пор, пока на выходе 15 (17) соответствующей цепочки последующей ячейки не появится высокий потенциал (означающий конец записи информации в ней), так как затворы транзисторов 2.2 и 2.3 (3.2 и 3.3) рассматриваемой цепочки первой ячейки закорочены. В свою очередь, новая информация в первую ячейку может быть записана только после установления низкого потенциала на выходе 15 (17) последующей ячейки (означает окончание стирания информации в ней). Тем самым информация записывается в данную ячейку, если она записана в предыдущую ячейку, а последующая ячейка не содержит информации и стирается в данной ячейке, если информа ция записана в последующую ячейку, а предьщущая ячейка не содержит информации.

Таким образом, последовательная передача в регистр порций информации при фиксированном (низком) значении входа 23 продолжается до тех пор, пока не ,заполнится весь регистр. При этом между двумя ячейками, хранящими информацию, будет находиться одна ячейка, в которой информация стерта.

Пусть на информационных входах регистра 19 и 20 зафиксирован набор 11, а в результате заполнения регистра информацией состояние его последней ячейки 01. Получив эту информацию с выходов 24 и 25 регистра, прием ник устанавливает на его входе 23 значение 1, что разрешает стирание - информадаи. В результате, если в пред последней ячейке информация отсутству ет, информация в последней ячейке стирается и одновременно разрешается запись информации и предпоследнюю ячейку. Как только информация в последней ячейке стерта, приемник может установить на выходе 24 значение 0. Таким образом, последовательный прием информации из регистра при зафиксированном наборе 11 на его инфор- .мационных входах 19 и 20 продолжается до тех пор, пока весь регистр не будет очищен, т.е. во всех ег-о ячейках не будет стерта информация.

20

18294

При одновременной работе источника и приемника информации процесс передачи ее протекает аналогично сказанному.

Время записи (стирания) информации в ячейке памяти асинхронного регистра сдвига составляет 2IX , где 2 - задержка ВДП-транзистора. Частота

Q выполнения операции сдвига в регистре составляет 1/6 С против 1/121 в известном устройстве. Оценивая затраты оборудования суммарным числом транзисторов в ячейке памяти регист 5 ра, получим соответственно 14 для предложенного регистра и 19 для известного. Формула изобретения

Асинхронный регистр сдвига на ЩП-транзисторах, содержащий ячейки памяти, причем каждая нечетная ячейка памяти состоит из трех, а каждая четная - из двух элементов ИЛИ-НЕ, первые входы первого и второго эле25 ментов ИЛИ-НЕ каждой ячейки памяти, кроме первой, соединены с выходами первого и второго элементов ИЛИ-НЕ. предыдущей ячейки памяти, а первые входы первого и второго элементов ИЛИ-НЕ первой ячейки памяти являются информационными входами регистра, выходы первого и второго элементов ИЛИ-НЕ последней ячейки памяти являются информационными выходами регистра, первый и второй входы третьего

35 элемента ИЛИ-НЕ каждой нечетной ячейки памяти соединены с выхода ми первого и второго элементов ИПИ-НЕ данной ячейки памяти, выход третьего элемента ИЛИ-НЕ каждой нечетной ячей40 ки памяти, кроме первой, соединён с

вторым входом первого элемента -ИЛИ-НЕ предыдущей ячейки памяти выход

третьего элемента ИЛИ-НЕ первой ячейки памяти является управлякяцим вы- 45 ходом записи регистра, о т л и ч а- ю щ и и с я тем, что, с целью упрощения и повышения быстродействия регистра, каждая нечетная ячейка памяти, кроме первой, содержит четвертый

50 элемент ИЛИ-НЕ, первый и второй входы которого соединены с выходами первого и второго элементов ИЛИ-НЕ данной ячейки памяти, а выход - с вторым входом второго элемента ИЛИ-НЕ

5g предьздущей ячейки памяти, каждая четная ячейка памяти содержит первый и второй элементы И-НЕ, первый и вто- рой входы каждого из которых соединены с выходами первого и второго эле30

iv eHTOB ИЛИ-НЕ данной ячейки памяти, И выходы - с вторыми входами соответ- с|твую цих элементов ИЛИ-НЕ предыдущей чейки памяти, каждая ячейка памяти содержит первый и второй ключевые элементы, каждый из которых выполнен на МДП-транзисторе, сток, исток и атвор которого соединены с первым

и вторым входами и выходом соответствующего элемента ИЛИ-НЕ данной ячейки памяти, первый и второй элементы НЕ, выходы которых соединены с вторыми входами соответствующих элементов ИЛИ-НЕ последней ячейки памяти, а входы являются управляющим входом считывания регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| СДВИГОВЫЙ РЕГИСТР (ВАРИАНТЫ) | 2013 |

|

RU2530271C1 |

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2522306C1 |

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2527188C1 |

| Асинхронный последовательный регистр | 1986 |

|

SU1410103A1 |

| Параллельный асинхронный регистр | 1988 |

|

SU1607016A1 |

| Магазинное запоминающее устройство | 1986 |

|

SU1472947A1 |

| ДВУХТАКТНЫЙ ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2556437C1 |

| Асинхронный регистр сдвига | 1985 |

|

SU1259337A1 |

| ДВУХКАСКАДНЫЙ ДИНАМИЧЕСКИЙ СДВИГОВЫЙ РЕГИСТР | 2014 |

|

RU2542898C1 |

| ДВУХТАКТНЫЙ СДВИГАЮЩИЙ РЕГИСТР | 2014 |

|

RU2549136C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при проектировании асинхронных регистров сдвига. Целью изобретения является упрощение и повьшение быстродействия регистра. Для достижения этой цели нечетные ячейки памяти регистра строятся из четырех элементов ИЛИ-НЕ, а четные - из двух элементов ШШ-НЕ и двух элементов И-НЕ, кроме того, входы первого и второго элементов ИЛИ-НЕ каждой ячейки памяти соединяются- через ключевые элементы, управляемые сигналами с выходов соответствующих элементов ИЛИ-НЕ. Число МДП-транзисто- ров, составляющих ячейку памяти регистра, по сравнению с прототипом уменьшено с 19 до 14, а.быстродейст- вие увеличено в два раза и составляет 1/6 ( f- задержка переключения МДП-транзистора). 2 ил. (б сл

| Ячейка памяти для буферного регистра | 1976 |

|

SU661606A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Апериодические автоматы./Под ред | |||

| В.И, Варшавского | |||

| М.: Наука, 1976, с | |||

| Распределительный механизм для паровых машин | 1921 |

|

SU308A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-07-23—Публикация

1986-07-09—Подача