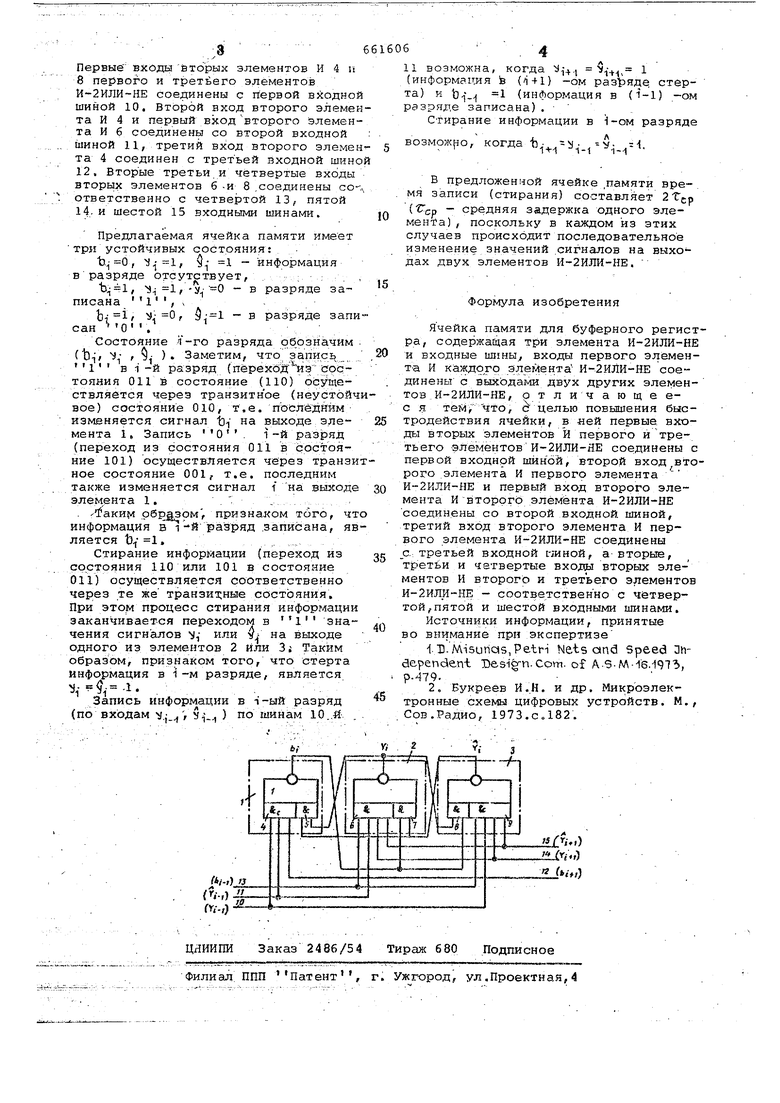

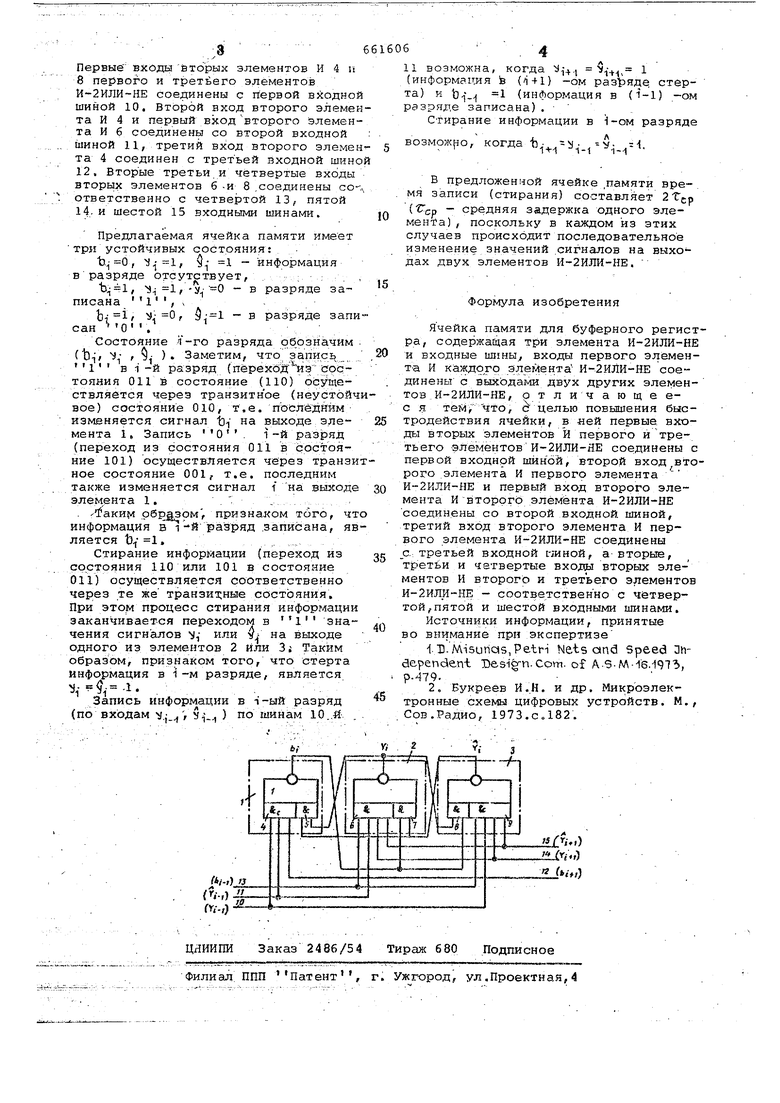

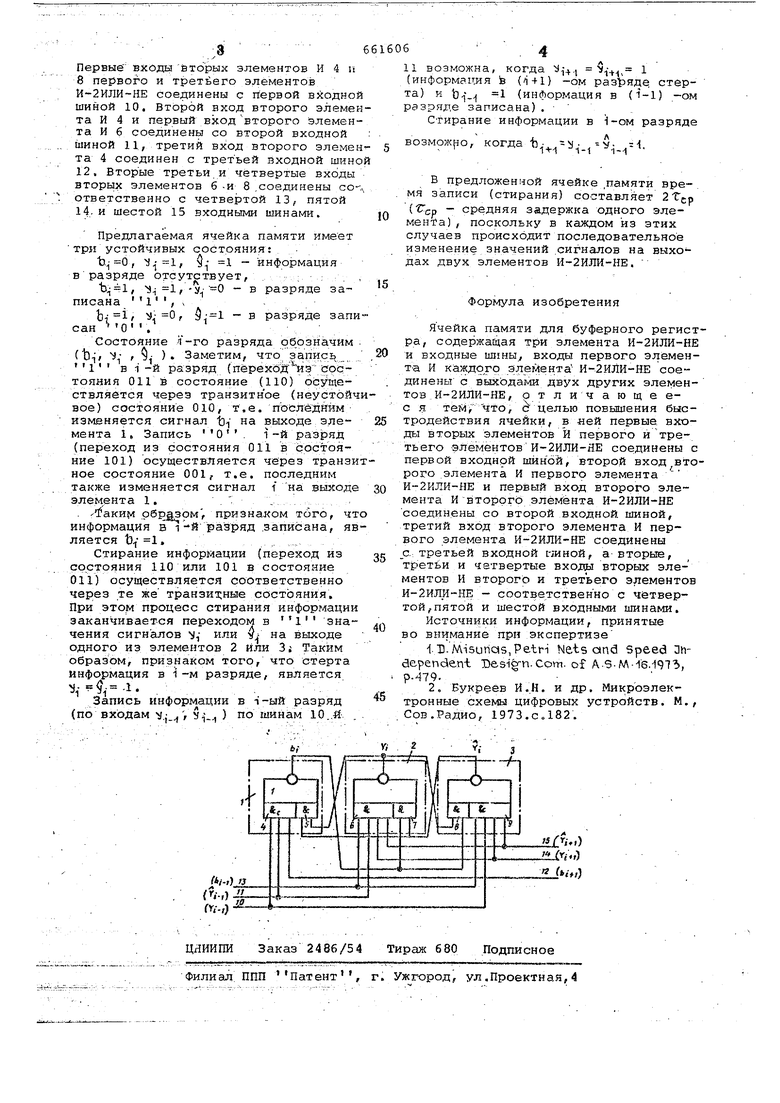

Изобретение относится к области автоматики и вычислительной техники, Известен буферный регистр, каждый разряд которого состоит из двух Сблоков и одного элемента ИЛЙ-НЕ ij , Такие буферные регистры используются, например, в качестве последе-V вательных регистров типа Pipeline. Вводимая в,них порция информации проталкивается к выходу, причем время через которое она появляется на выходе, зависит как от собственных (реальных) задержек элементов регистра, так и от его заполнения. Наиболее близким техническим решением к изобретению является ячейка памяти для буферного регистра, построенная на основе трехстабильяого триггера на элементах И-2ИЛИ-НЕ, причем в этой схеме входы только nep вого элемента И каждого их трех элементов И-2ИЛИ-НЁ соединены с выходами двух других элементов И-2ИЛИ-НЕ 2. Недостатком таких устройств явля ется сравнительно низкое быстродействие. . Цель изобретения - повышение быстродействия ячейки памяти. Поставленная цель достигается .тем, что в ячейке памяти для буферного регистра, содержащей три элемента И-2ИЛИ-НЕ и входные шины. Входы первого элемента И каждого элемента И-2ИЛИ-НЕ соединены с выходами двух других элементов И-2ИЛИ-НЕ. Первые входы вторых элементов И первого и третьего элементов И-2ИЛИ-НЕ соединены с первой входной шиной. Второй вход Второго элемента И первого элемента Й-2ИЛЙ-НЕ и первый вход второго элемента И второго элемента И-2ИЛИЯЕ соединены со второй входной шиной. Третий вход второго элемента И первого .элекента И-2ИЛИ-НЕ соединен с третьей входной шиной, а вторые, третьи и четвертые входы вторахэлементов 11 второго и третьего элементов И-2ИЛИ НЕ - соответгственно с четвертой, пятой и шестой входными шинами. На чертеже представлена схема предложенной ячейки памяти для буферного :регистра., Ячейка памяти содержит элементы И-2ИЛИ-НЕ. 1-3 с элементами И 4-9. Входы первых элементов И 5-9 каждого элемента И-2ИЛИ-НЕ соединены с выходами двух других элементов И-2ИЛИ-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти для буферного регистра | 1980 |

|

SU905860A1 |

| Устройство для сопряжения процессора с памятью | 1986 |

|

SU1363229A1 |

| Устройство для контроля неисправностей | 1987 |

|

SU1564626A1 |

| Вероятностная вычислительная машина | 1986 |

|

SU1455344A1 |

| Устройство управления буферной памятью | 1978 |

|

SU737952A1 |

| Мультипрограммное вычислительное устройство | 1990 |

|

SU1777147A1 |

| ПРОГРАММИРУЕМОЕ УСТРОЙСТВО ДЛЯ ЛОГИЧЕСКОГО УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДАМИ, ЭЛЕКТРОННЫМИ КЛЮЧАМИ И СИГНАЛИЗАЦИЕЙ | 1999 |

|

RU2154852C1 |

| Коммутационное устройство для мультипроцессорной системы | 1976 |

|

SU734697A1 |

| Устройство для сопряжения основной памяти цифровой вычислительной машины с каналами ввода-вывода | 1977 |

|

SU689438A1 |

| Программируемый многоканальный формирователь серий импульсов | 1991 |

|

SU1775846A1 |

Авторы

Даты

1979-05-05—Публикация

1976-02-04—Подача