Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах с магазинной памятью.

Целью изобретения является повышение быстродействия устройства за сче организации его работы по реальным задержкам элементов путем индикации моментов окончания переходных про- цессов в устройстве.

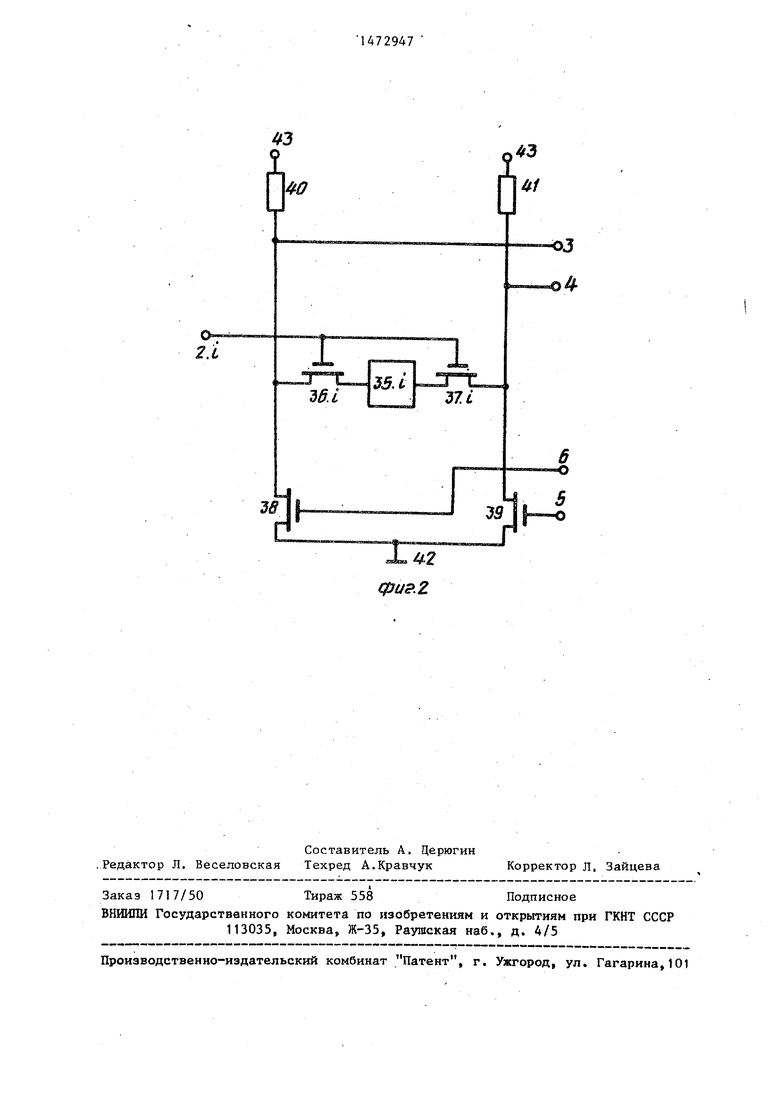

На фиг. 1 приведена схема запоминающего устройства; на фиг. 2 - схем блока памяти.

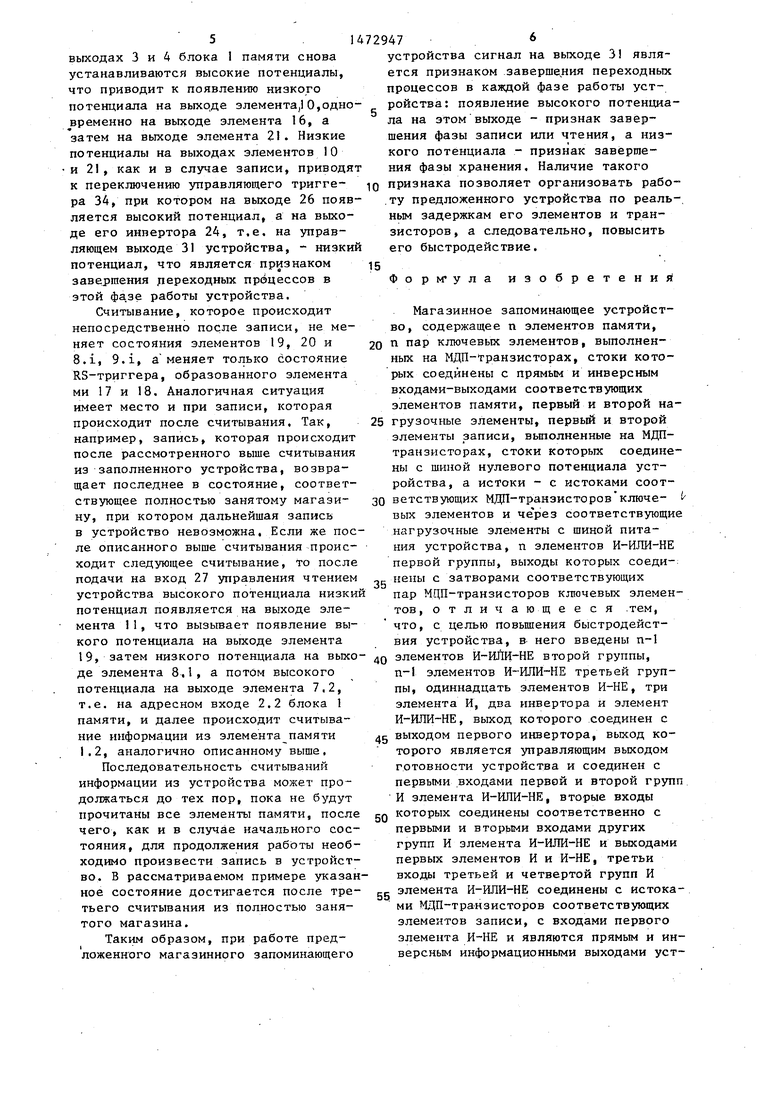

Устройство (фиг.1) содержит блок 1 памяти, имеющий адресные входы 2.1-2.П, нулевой 3 и единичный 4 информационные выходы, прямой 5 и инверсный 6 информационные входы элементов И-ИЛИ-НЕ первой 7.1-7.П, вто- рой 8.1-8,(п-1) и третьей 9.1-9.(пгрупп, одиннадцать элементов И-НЕ 10-20, три элемента И 21-23, два инвертора 24 и 25 и элемент И-ИЛИ-НЕ 26. На фиг, 1 показаны также выходы управления чтением 27 и записью 28, информационный вход 29, вход 30 начальной установки, управляющий выход 31 готовности и информационные выхоа на выходе другого - высокий потенциал, в виду чего в начальном состоянии на выходе одного из элементов 15 или 16 имеется низкий потенциал, который вызывает появление низкого потенциала на выходе элемента 21. Вс перечисленное приводит к тому, что на выходе элемента 26 управляющего триггера 34 в начальном состоянии имеется высокий потенциал, а на выходе его инвертора 24, т.е. на управляющем выходе 31 устройства, - низкий потенциал.

Перед началом работы на вход 30 « начальной установки подается низкий потенциал, который вызывает появление высоких потенциалов на выходах элементов 18,15,19,9.1 и 9.2 и низких потенциалов на выходах элементов 17, 16, 20, 8.1 и 8.2. После этого на входе 30 восстанавливается высокий потенциал. Описанное начальное состояние соответствует пустому магазину. Для продолжения работы необходимо произвести запись в устройство , для чего на его информационный вход 29 выставляется записываемая информация и подается на вход 28 уп

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1987 |

|

SU1465911A1 |

| Запоминающее устройство | 1987 |

|

SU1474738A1 |

| Запоминающее устройство типа "очереди | 1987 |

|

SU1532977A1 |

| ЯЧЕЙКА ПАМЯТИ АССОЦИАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2008 |

|

RU2390860C1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Параллельный асинхронный регистр | 1988 |

|

SU1607016A1 |

| СТАТИЧЕСКАЯ ЗАПОМИНАЮЩАЯ ЯЧЕЙКА С ДВУМЯ АДРЕСНЫМИ ВХОДАМИ | 2011 |

|

RU2470390C1 |

| ЯЧЕЙКА ПАМЯТИ СТАТИЧЕСКОГО ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2012 |

|

RU2507611C1 |

| Запоминающее устройство на МОП-транзисторах | 1986 |

|

SU1336112A1 |

| Блок управления для запоминающего устройства | 1977 |

|

SU723679A1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах с магазинной памятью. Целью изобретения является повышение быстродействия устройства за счет организации его работы по реальным задержакам элементов путем индикации моментов окончания переходных процессов в устройстве. Для достижения этой цели в устройство введены вторая 8 и третья 9 группы элементов И-ИЛИ-НЕ, одинадцать элементов И-НЕ, три элемента И 21-23, два инвертора 24, 25 и элемент И-ИЛИ-НЕ 26, который месте с первым инвертором 24 образуют триггер индикации 34. 2 ил.

ды 32 и 33 устройства. Элемент И-ИЛИ-30 равления записью высокий потенциал,

НЕ 26 и первый инвертор 24 образуют управляющий триггер 34.

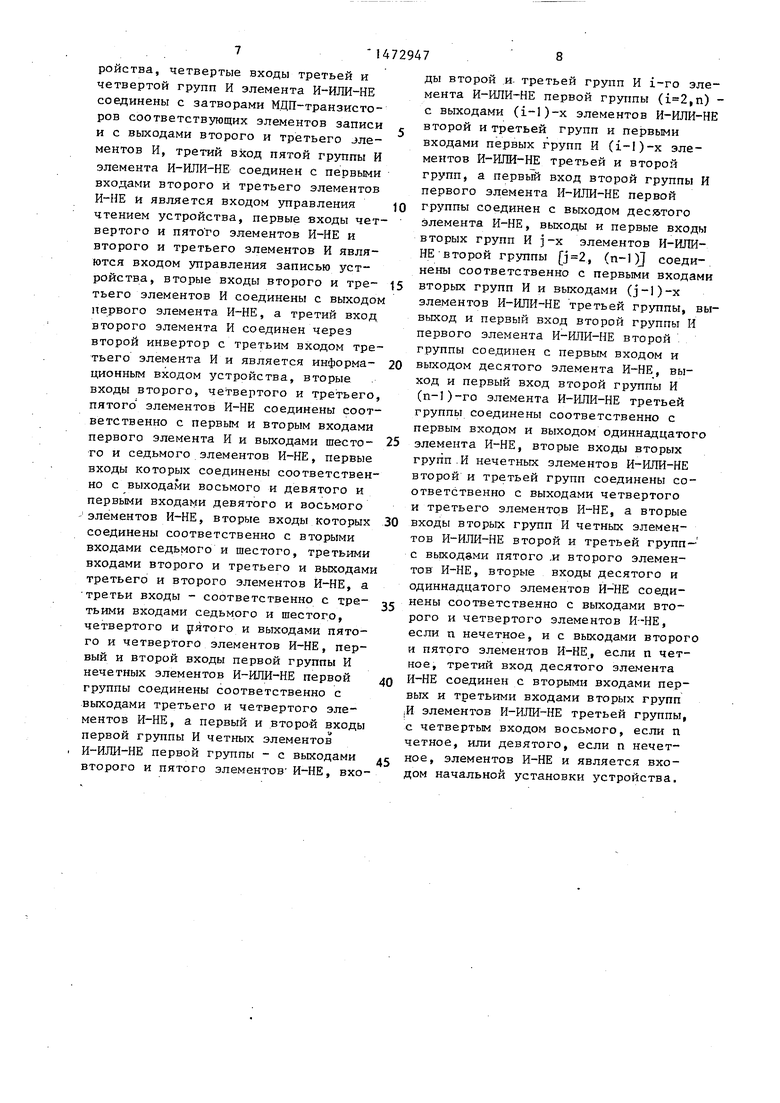

На фиг. 2 показаны блок 1 памяти, срстоя ций из п элементов 351, (,n) памяти, п пар ключевых элементов 36i,( 371, элементов 38 и 39 записи и нагрузочных элементов 40 и 41, выполненных на МДП-транзисторах, а также шины 42 нулевого потенциала и шина 43 питания устройства.

Магазинное запоминающее устройство работает следующим образом,

В начальном состоянии на входы управления 27 чтением и 28 записью

устройства подается низкий потенциал. д§ лы« Появление высокого потенциала В результате на выходах элементов на адресном входе 2.3 открывает соответствующие транзисторы 36,3 и 37.3, и через один из них низкий по- терциал с одного из входов-выходов элемента 35.3 памяти поступает на

11-14 имеются высокие потенциалы, а на выходе элементов 7,1-7.3, т.е. на адресных входах 2.1-2.3 блока 1 памяти - низкие потенциалы, закрываю50

щие транзисторы 361 и 371. Низкие потенциалы на выходах элементов 23 и 22 закрывают транзисторы 38 и 39. Таким образом, на выходах 3 и 4 блока 1 устанавливаются высокие потенциалы, а на выходе элемента 10 - низкий потенциал. Элементы 17 и 18 образуют RS-триггер, и на выходе одного из них имеется низкий потенциал,

5

0

который вызывает появление низкого потенциала на выходе элемента 13. Последнее приводит к установке высокого потенциала на выходе элемента 20, затем низкого потенциала на вы- выходе элемента 9.2 и, наконец, высокого потенциала на выходе элемента 7.3, т.е. на адресном входе 2.3 блока 1 памяти. Одновременно с этим происходит переключение RS-триггера, образованного элементами 17 и 18, , после чего -на выходах обоих элементов 15 и 16, а затем и на. выходе элемента 21 появляются высокие потенциалы« Появление высокого потенциала на адресном входе 2.3 открывает соответствующие транзисторы 36,3 и 37.3, и через один из них низкий по- терциал с одного из входов-выходов элемента 35.3 памяти поступает на

выходы 3 или 4, что, в свою очередь, - вызывает установку высокого потенциала на выходе элемента 10, а потом и на выходе элементов 22 и 23, в результате чего прямое и инверсное значения записываемой информации проходят на входы 6 и 5 блока 1 памяти и, открыв один из транзисторов 38 или 39, записываются через открытые тран

зисторы 36.3 и 37.3 в элемент памяти 35.3. Признаком завершения записи информации в элемент памяти является .совпадение высоких потенциалов на выходе 3 и входе 5 блока 1 или на выходе 4 и входе 6 блока 1. Это совпадение совместно с высокими потенциалами с выходов элементов 10 и 21 вызывает переключение управляющего триггера 34, при котором сначала на выходе его элемента 26 появляется ни низкий потенциал, а потом на выходе его инвертора 24, т.е. на управляющем выходе 31 устройства, - высокий потенциал, что является признаком завершения переходных процессов в этой фазе работы устройства.

После этого на входе 28 управления записью снова устанавливается низкий потенциал, что вызывает появление высоких потенциалов на выходе элементов 13 и 14, затем низких потенциалов на выходах элементов 7,3, 15, 21, 22 и 23. Появление низкого потенциала на выходе элемента 7.3, т.е. на адресном входе 2.3 блока 1 памяти, закрывает транзисторы 36.3 и 37,3 последнего, появление низких потенциалов на выходах элементов 22 и 24, т.е. на входах 6 и 5 блока 1 памяти, - транзисторы 38и 39. Таким образом на обоих выходах 3 и 4 блока 1 памяти устанавливаются высокие дотенциалы, что вызывает появление низкого потенциала на выходе элемента 10. Низкие потенциалы на выходах элементов 10 и 2 приводят к переключению управляющего триггера 34, при котором на выходе его элемента 26 появляется высокий потенциал, а на выходе его инвертора 24, т.е. на управляющем выходе 31 устройства, - низкий потенциал, что является признаком завершения переходных процессов в этой фазе работы устройства.

Теперь в магазине занят один элемент памяти (элемент ,3 ) и возможны как следующая вторая запись, так и первое считывание. Следующая запись происходит аналогично рассмотренной, с той лишь разницей, что при подаче высокого потенциала на вход 28 управления записью устройства низкий потенциал появляется на выходе элемента 14, затем высокий потенциал - на выходе элемента 8.2, потом низкий потенциал - на выходе элемента 9.1 и, наконец, высокий по

JO

0

5

15

0

5

0

5

0

5

тенциал - на выходе элемента 7,2, т.е. на адресном входе 2,2, что вы- . зывает запись информации в элемент 35.2.

Последовательность записей в устройство может продолжаться до тех пор, пока не заполнятся все ячейки памяти, признаком чего является низкий потенциал на выходе элемента 19. В рассматриваемом примере указанное состояние достигается после третьей записи, при этом на выходах элементов 9.1 и 9.2 - низкие потенциалы, а на выходах элементов 8.1, 8.2 и 20 - высокие потенциалы.

Для продолжения работы при полностью занятом магазине необходимо произвести считывание информации, для чего на входе 27 управления чтением устройства выставляется высокий потенциал, который вызывает появление низкого потенциала на выходе элемента 12. Последнее приводит к установке высокого потенциала на выходе элемента 7.1, т.е. на адресном входе 2 . I блока 1 памяти. Одновременно с этим, как и в случае записи, происходит переключение RS-триггера, образованного элементами 17 и 18, после которого на выходах обоих элементов 15 и 16, а затем и на выходе элемента 21 появляются высокие потенциалы. Появление высокого потенциала на адресном входе 2,1 открывает транзисторы 36.1 и 37.1 и через один из них низкий потенциал с одного из входов-выходов элемента памяти 35.1 поступает на вход 3 или 4, что вызывает установку высокого потенциала на выходе элемента 10. 3 режиме чтения высокие потенциалы с выходов элементов 10 и 2 вызывают переключение управляющего триггера 34, при котором на выходе его элемента 26 появляется низкий потенциал, а на выходе его инвертора 24, т.е. на управляющем выходе 31 устройства, - высокий потенциал, что является признаком завершения переходных процессов в этой фазе работы устройства. После этого на входе 27 управления чтением устройства снова устанавливается низкий потенциал, что вызывает появление высоких потенциалов на выходах элементов 1 и 12, затем низкого потенциала на выходе элемента 7.1, в результате чего транзисторы 36.1 и 37,1 закрываются и на

выходах 3 и 4 блока 1 памяти снова устанавливаются высокие потенциалы, что приводит к появлению низкого потенциала на выходе элемента, О,одновременно на выходе элемента 16, а затем на выходе элемента 21. Низкие потенциалы на выходах элементов 10 и 21, как и в случае записи, приводят к переключению управляющего тригге- Q pa 34, при котором на выходе 26 появляется высокий потенциал, а на выходе его инвертора 24, т.е. на управляющем выходе 31 устройства, - низкий потенциал, что является признаком $ завершения переходных процессов в этой фазе работы устройства.

Считывание, которое происходит непосредственно после записи, не меняет состояния элементов 19, 20 и 8.1, 9.1, а меняет только состояние RS-триггера, образованного элемента ми 17 и 18. Аналогичная ситуация имеет место и при записи, которая происходит после считывания. Так, например, запись, которая происходит после рассмотренного выше считывания из заполненного устройства, возвращает последнее в состояние, соответствующее полностью занятому магазину, при котором дальнейшая запись в устройство невозможна, Если же после описанного выше считывания происходит следующее считывание, то после подачи на вход 27 управления чтением устройства высокого потенциала низкий потенциал появляется на выходе элемента 11, что вызывает появление вы- кого потенциала на выходе элемента

2о

25

30

35

19, затем низкого потенциала на выхо- 40 элементов И-ИЛИ-НЕ второй группы, де элемента 8,1, а потом высокого потенциала на выходе элемента 7.2, т.е. на адресном входе 2.2 блока 1 памяти, и далее происходит считывание информации из элемента памяти 1.2, аналогично описанному выше, Последовательность считываний информации из устройства может продолжаться до тех пор, пока не будут

п-1 элементов И-ИЛИ-НЕ третьей гру пы, одиннадцать элементов И-НЕ, тр элемента И, два инвертора и элемен И-ИЛИ-НЕ, выход которого соединен 45 выходом первого инвертора, выход к торого является управляющим выходо готовности устройства и соединен с первыми входами первой и второй гр И элемента И-ИЛИ-НЕ, вторые входы

прочитаны все элементы памяти, после gn которых соединены соответственно с

чего, как и в случае начального состояния, для продолжения работы необходимо произвести запись в устройство. В рассматриваемом примере указанное состояние достигается после тре- 5g элемента И-ИЛИ-НЕ соединены с истоками МДП-транзисторов соответствующих элементов записи, с входами первого элемента И-НЕ и являются прямым и инверсным информационными выходами усттьего считывания из полностью занятого магазина.

Таким образом, при работе предложенного магазинного запоминающего

Q $

29476

устройства сигнал на выходе 3 является признаком завершения переходных процессов в каждой фазе работы устройства: появление высокого потенциала на этом выходе - признак завершения фазы записи или чтения, а низкого потенциала - признак завершения фазы хранения. Наличие такого признака позволяет организовать работу предложенного устройства по реальным задержкам его элементов и транзисторов, а следовательно, повысить его быстродействие.

Ф о р м у л а изобретения

Магазинное запоминающее устройство, содержащее п элементов памяти,

п пар ключевых элементов, выполненных на МДП-транзисторах, стоки которых соединены с прямым и инверсным входами-выходами соответствующих элементов памяти, первый и второй нагрузочные элементы, первый и второй элементы записи, выполненные на МДП- транзисторах, стоки которых соединены с шиной нулевого потенциала устройства, а истоки - с истоками соответствующих МДП-транэисторов ключе- вых элементов и через соответствующие нагрузочные элементы с шиной питания устройства, п элементов И-ИЛИ-НЕ первой группы, выходы которых соединены с затворами соответствующих пар МЦП-транзисторов ключевых элементов, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены п-1

элементов И-ИЛИ-НЕ второй группы,

п-1 элементов И-ИЛИ-НЕ третьей группы, одиннадцать элементов И-НЕ, три элемента И, два инвертора и элемент И-ИЛИ-НЕ, выход которого соединен с выходом первого инвертора, выход которого является управляющим выходом готовности устройства и соединен с первыми входами первой и второй групп И элемента И-ИЛИ-НЕ, вторые входы

первыми и вторыми входами других групп И элемента И-ИЛИ-НЕ и выходами первых элементов И и И-НЕ, третьи входы третьей и четвертой групп И

элемента И-ИЛИ-НЕ соединены с истоками МДП-транзисторов соответствующих элементов записи, с входами первого элемента И-НЕ и являются прямым и инверсным информационными выходами уст

роиства, четвертые входы третьей и четвертой групп И элемента И-ИЛИ-НЕ соединены с затворами МДИ-транзисторов соответствующих элементов записи и с выходами второго и третьего элементов И, третий вход пятой группы И элемента И-ИЛИ-НЕ соединен с первыми входами второго и третьего элементов И-НЕ и является входом управления чтением устройства, первые входы четвертого и пятого элементов И-НЕ и второго и третьего элементов И являются входом управления записью устройства, вторые входы второго и тре- тьего элементов И соединены с выходом первого элемента И-НЕ, а третий вход второго элемента И соединен через второй инвертор с третьим входом третьего элемента И и является информа- ционным входом устройства, вторые входы второго, четвертого и третьего, пятого элементов И-НЕ соединены соответственно с первым и вторым входами

первого элемента И и выходами шесто- 25 элемента И-НЕ, вторые входы вторых

го и седьмого элементов И-НЕ, первые входы которых соединены соответственно с выходами восьмого и девятого и первыми входами девятого и восьмого элементов И-НЕ, вторые входы которых соединены соответственно с вторыми входами седьмого и шестого, третьими входами второго и третьего и выходам третьего и второго элементов И-НЕ, а третьи входы - соответственно с третьими входами седьмого и шестого, четвертого и пятого и выходами пятого и четвертого элементов И-НЕ, первый и второй входы первой группы И нечетных элементов И-ИЛИ-НЕ первой группы соединены соответственно с выходами третьего и четвертого элементов И-НЕ, а первый и второй входы первой группы И четных элементов И-ИЛИ-НЕ первой группы - с выходами второго и пятого элементов И-НЕ, вхо10

1520729478

ды второй и третьей групп И i-ro элемента И-ИЛИ-НЕ первой группы (,n) - с выходами (i-l)-x элементов И-ИЛИ-НЕ второй и третьей групп и первыми входами первых групп И (i-I)-x элементов Й-ИЛИ-НЕ третьей и второй групп, а первый вход второй группы И первого элемента И-ИЛИ-НЕ первой группы соединен с выходом десятого элемента И-НЕ, выходы и первые входы вторых групп И j-х элементов И-ИЛИ- НЕ второй группы , (n-l)J соединены соответственно с первыми входами вторых групп И и выходами (j-l)-x элементов И-ИЛИ-НЕ третьей группы, вы- выход и первый вход второй группы И первого элемента И-ИЛИ-НЕ второй группы соединен с первым входом и выходом десятого элемента И-НЕ, выход и первый вход второй группы И (n-l)-ro элемента И-ИЛИ-НЕ третьей группы соединены соответственно с первым входом и выходом одиннадцатого

0

5

0

5

групп И нечетных элементов И-ИЛИ-НЕ второй и третьей групп соединены соответственно с выходами четвертого и третьего элементов И-НЕ, а вторые входы вторых групп И четных элементов И-ИЛИ-НЕ второй и третьей групп-- с выходами пятого и второго элементов И-НЕ, вторые входы десятого и одиннадцатого элементов И-НЕ соединены соответственно с выходами второго и четвертого элементов И-НЕ, если п нечетное, и с выходами второго и пятого элементов И-НЕ, если п четное, третий вход десятого элемента И-НЕ соединен с вторыми входами первых и третьими входами вторых групп И элементов И-ИЛИ-НЕ третьей группы, с четвертым входом восьмого, если п четное, или девятого, если п нечетное, элементов И-НЕ и является входом начальной установки устройства.

| Реверсивный буферный регистр сдвига | 1978 |

|

SU780045A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Шигин А.Г., Дерюгин А.А | |||

| Цифровые вычислительные машины (Память ЦВМ) | |||

| - М.: Энергия, 1975, с | |||

| Устройство для нахождения генерирующих точек контактного детектора | 1923 |

|

SU472A1 |

Авторы

Даты

1989-04-15—Публикация

1986-11-19—Подача