;о о vj

Изобретение относится к вычислительной технике и может быть использовано в качестве буферного запоминающего устройства (БЗУ) для ввода изображений в цифровом виде.

Известны БЗУ, в которых используется метод перекрестно-последовательного обращения, позволяющий осуществлять двухсторонний обмен информацией и совмещать процессы ввода информации в БЗУ и ее вывода 1.

Недостатком известного устройства является невозможность осуществления перестановки информации, что не позволяет осуществлять геометрическое преобразование изображений.

Наиболее близким по технической сущности к изобретению является буферное запоминающее устройство, содержащее накопитель, информационные выходы и входы которого являются соответственно информационными выходами и первыми информационными в.ходами устройства, адресные входы накопителя являются адресными входами устройства и подключены к выходам мультиплексора, информационные входы которого подключены к выходам первого и второго счетчиков, входы первого и второго счетчиков являются соответственно первым и вторым управляющими входами устройства и подключены ко вxqдaм триггера, выход которого подключен к первым управляющим входам мультиплексора и накопителя 2.

Недостатком известного устройства является невозможность осуществления перестановки информации, что не позволяет осуществлять геометрическое преобразование изображения путем перестановки элементов матрицы изображения в процессе ввода информации. Это сужает область применения.

Цель изобретения - расщирение области применения устройства за счет возможности перестановки информации.

Поставленная цель достигается тем, что в буферное запоминающее устройство,- содержащее первый накопитель, информационные выходы и информационные входы которого являются соответственно информационными выходами и первыми информационными входами устройства, адресные входы первого накопителя являются адресными входами устройства и подключены к выходам мультиплексора, информационные входы которого подключены к выходам первого и второго счетчиков, входы первого и второго счетчиков являются соответственно первым и вторым управляющими входами устройства и подключены к входам триггера, выход которого подключен к первым управляющим входа.м мультиплексора и первого накопителя, дополнительно введены второй накопитель и блок управления, первый выход

которого подключен к второму управляющему входу мультиплексора, второй и третий выходы блока управления подключены соответственно к первому и второму управляющим входам второго накопителя, адресные входы и выходы которого подключены к адресным входам первого накопителя, информационные входы второго накопителя являются вторыми информационными входами устройства, четвертый выход блока управления подключен к второму управляющему входу первого накопителя, управляющий выход которого подключен к первому входу блока управления, второй вход блока управления подключен к управляющему выходу второго накопителя,другие входы блока управления являются соответствующим управляющими входами устройства.

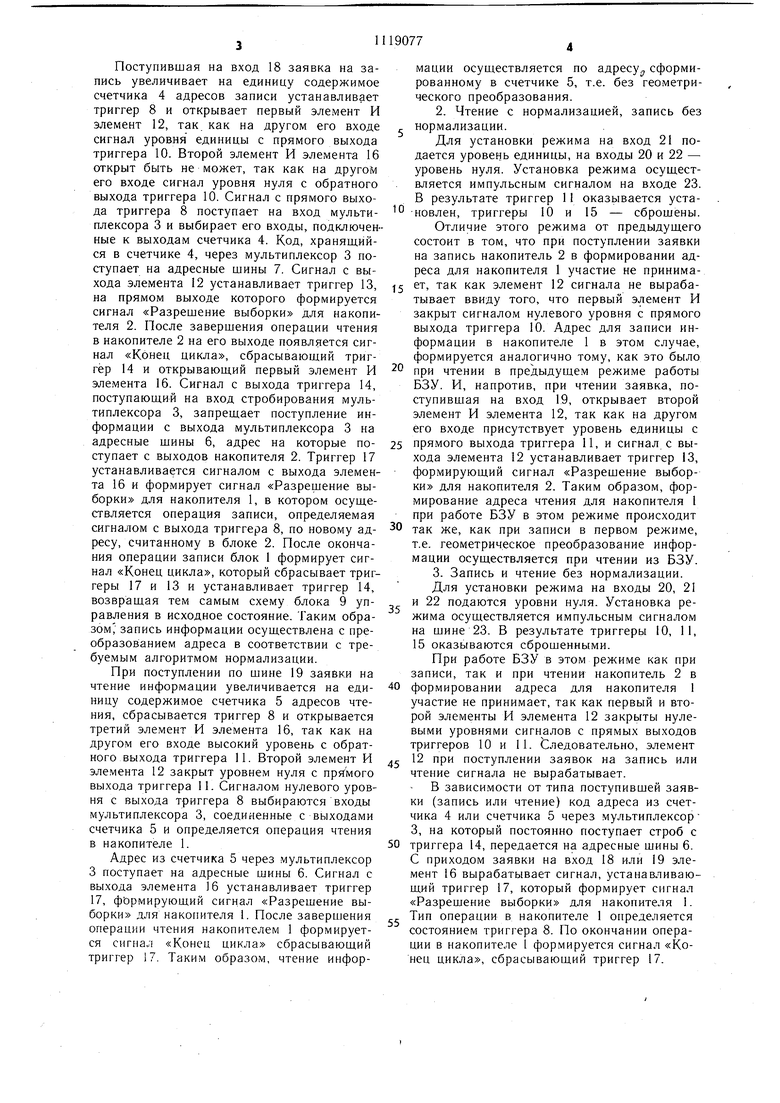

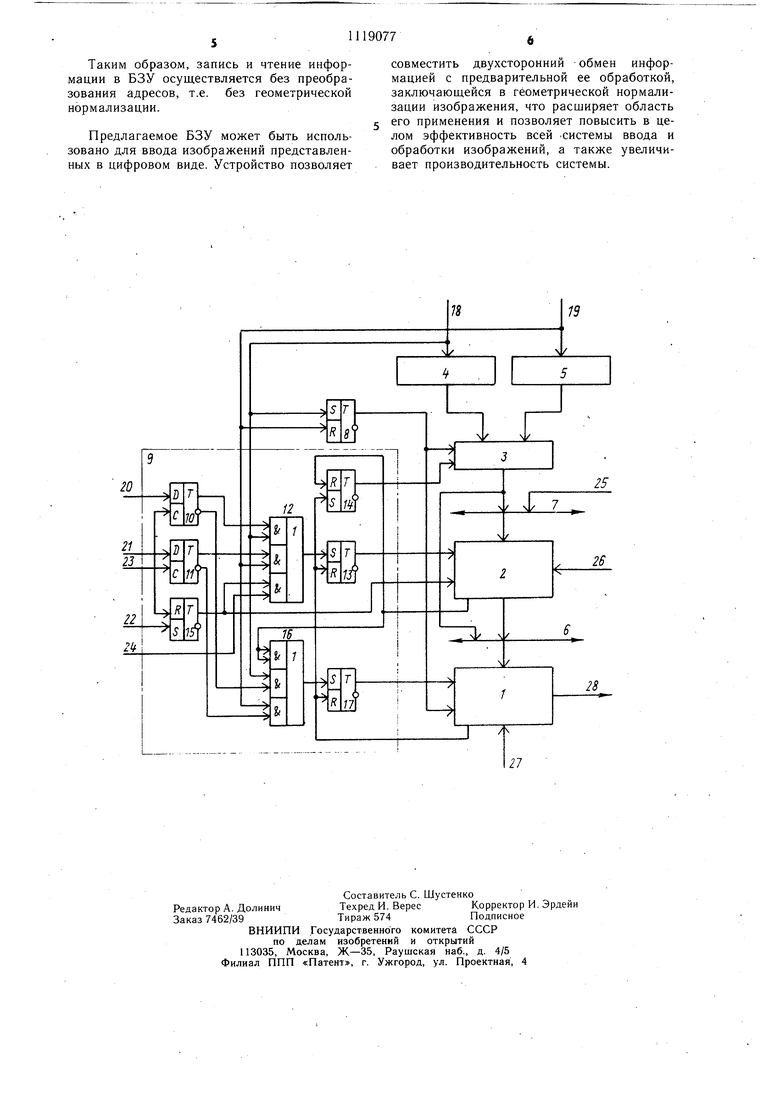

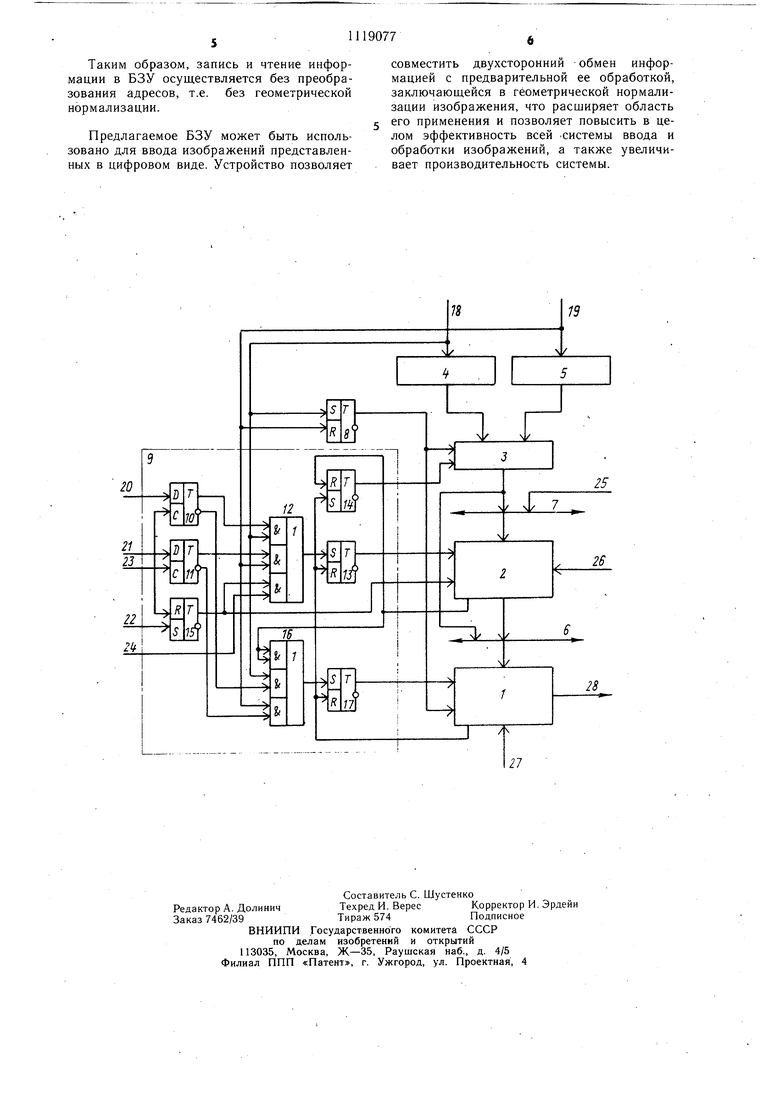

На чертеже представлена схема устройства.

Устройство содержит накопители 1 и 2, мультиплексор 3,счетчики 4 и 5, адресные шины 6 накопителя 1, адресные щины 7 накопителя 2, триггер 8, блок 9 управления. Блок 9 управления содержит триггеры 10 и 11, элемент 12 И-ИЛИ, триггеры 13, 14 и 15, элемент 16 И-ИЛИ, триггер 17 и имеет следующие входы: управляющий вход

18заявки на запись, управляющий вход

19заявки на чтение, управляющий вход 20 режима записи, управляющий вход 21 режима чтения, управляющий вход 22 установки .режима загрузки, накопителя 2, управляющий вход 23 установки режима работы, управляющий вход 24 заявки на загрузку данных в накопитель 2, адресные входы 25, информационные входы 26 и 27, выходы 28.

Устройство работает следующим образом.

Перед началом работы сигналом на входе 22 устанавливается триггер 15, разрещающий операцию записи во втором блоке 2 памяти. По информационным входам 26. адресны.м, входам 25 и входу 24 заявки на за, грузку осуществляется запись информации в накопитель 2. Загружаемая информация представляет собой совокупность адресов на копителя 1, сформированную предварительно в соответствии с требуемым алгоритмом геометрической нормализации вводимой информации.

БЗУ может работать в трех режимах.

1. Запись с нормализацией,чтение без нормализации.

Для установки режима на вход 20 подается уровень единицы, на входы 21 п 22 уровень нуля. Установка режима осуществ пяется импульсным сигналом на входе 23. В результате триггер 10 оказывается установлен, триггеры 11 и 15 - сброшены. Сброшенный триггер 15 разреп1ает операцию чтения в накопителе 2.

Поступившая на вход 18 заявка на запись увеличивает на единицу содержимое счетчика 4 адресов записи устанавливает триггер 8 и открывает первый элемент И элемент 12, так. как на другом его входе сигнал уровня единицы с прямого выхода триггера 10. Второй элемент И элемента 16 открыт быть не может, так как на другом его входе сигнал уровня нуля с обратного выхода триггера 10. Сигнал с прямого выхода триггера 8 поступает на вход мультиплексора 3 и выбирает его входы, подключенные к выходам счетчика 4. Код, хранящийся в счетчике 4, через мультиплексор 3 поступает на адресные шины 7. Сигнал с выхода элемента 12 устанавливает триггер 13, на прямом выходе которого формируется сигнал «Разрешение выборки для накопителя 2. После завершения операции чтения в накопителе 2 на его выходе появляется сигнал «Конец цикла, сбрасывающий триггер 14 и открывающий первый элемент И элемента 16. Сигнал с выхода триггера 14, поступающий на вход стробирования мультиплексора 3, запрещает поступление информации с выхода мультиплексора 3 на адресные щины 6, адрес на которые поступает с выходов накопителя 2. Триггер 17 устанавливается сигналом с выхода элемента 16 и формирует сигнал «Разрещение выборки для накопителя 1, в котором осуществляется операция записи, определяемая сигналом с выхода триггера 8, по новому адресу, считанному в блоке 2. После окончания операции записи блок 1 формирует сигнал «Конец цикла, который сбрасывает триггеры 17 и 13 и устанавливает триггер 14, возвращая тем самым схему блока 9 управления в исходное состояние. Таким образом запись информации осуществлена с преобразованием адреса в соответствии с требуемым алгоритмом нормализации.

При поступлении по шине 19 заявки на чтение информации увеличивается на единицу содержимое счетчика 5 адресов чтения, сбрасывается триггер 8 и открывается третий элемент И элемента 16, так как на другом его входе высокий уровень с обратного выхода триггера 11. Второй элемент И элемента 12 закрыт уровнем нуля с выхода триггера 11. Сигналом нулевого уровня с выхода триггера 8 выбираются входы мультиплексора 3, соединенные с выходами счетчика 5 и определяется операция чтения в накопителе 1.

Адрес из счетчика 5 через мультиплексор 3 поступает на адресные шины 6. Сигнал с выхода элемента 16 устанавливает триггер 17, фьрмирующий сигнал «Разрешение выборки для накопителя 1. После завершения операции чтения накопителем 1 формируется сигнал «Конец цикла сбрасывающий триггер 17. Таким образом, чтение информации осуществляется по адресу, сформированному в счетчике 5, т.е. без геометрического преобразования.

2.Чтение с нормализацией, запись без нормализации.

Для установки режима на вход 21 подается уровень единицы, на входы 20 к 22 - уровень нуля. Установка режима осуществляется импульсным сигналом на входе 23. В результате триггер 11 оказывается уста0 -новлен, триггеры 10 и 15 - сброшены. Отличие этого режима от предыдущего состоит в том, что при поступлении заявки на запись накопитель 2 в формировании адреса для накопителя 1 участие не принима5 ет, так как элемент 12 сигнала не вырабатывает ввиду того, что первый элемент И закрыт сигналом нулевого уровня с прямого выхода триггера 10. Адрес для записи информации в накопителе 1 в этом случае, формируется аналогично тому, как это было

0 при чтении в предыдущем режиме работы БЗУ. И, напротив, при чтении заявка, поступившая на вход 19, открывает второй элемент И элемента 12, так как на другом его входе присутствует уровень единицы с

5 прямого выхода триггера 11, и сигнал с выхода элемента 12 устанавливает триггер 13, формирующий сигнал «Разрешение выборки для накопителя 2. Таким образом, формирование адреса чтения для накопителя 1 при работе БЗУ в этом режиме происходит

0 так же, как при записи в первом режиме, т.е. геометрическое преобразование информации осуществляется при чтении из БЗУ.

3.Запись и чтение без нормализации. Для установки режима на входы 20, 21

и 22 подаются уровни нуля. Установка режима осуществляется импульсным сигналом на шине 23. В результате триггеры 10, 11, 15 оказываются сброшенными.

При работе БЗУ в этом режиме как при записи, так и при чтении накопитель 2 в

0 формировании адреса для накопителя 1 участие не принимает, так как первый и второй элементы И элемента 12 закрыты нулевыми уровнями сигналов с прямых выходов триггеров 10 и II. Следовательно, элемент

j 12 при поступлении заявок на запись или чтение сигнала не вырабатывает.

В зависимости от типа поступившей заявки (запись или чтение) код адреса из счетчика 4 или счетчика 5 через мультиплексор 3, на который постоянно поступает строб с

0 триггера 14, передается на адресные шины 6. С приходом заявки на вход 18 или 19 элемент 16 вырабатывает сигнал, устанавливающий триггер 17, который формирует сигнал «Разрешение выборки для накопителя 1. Тип операции в накопителе 1 определяется состоянием триггера 8. По окончании операции в накопителе 1 формируется сигнал «Конец цикла, сбрасывающий триггер 17.

Таким образом, запись и чтение информации в БЗУ осуществляется без преобразования адресов, т.е. без геометрической нормализации.

Предлагаемое БЗУ может быть использовано для ввода изображений представленных в цифровом виде. Устройство позволяет

совместить двухсторонний обмен информацией с предварительной ее обработкой, заключающейся в геометрической нормализации изображения, что расщиряет область его применения и позволяет повысить в целом эффективность всей .системы ввода и обработки изображений, а также увеличивает производительность системы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1983 |

|

SU1124379A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1261012A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1783581A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1163357A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1257704A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1571679A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1280457A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1297115A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1672527A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1363308A1 |

БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее первый накопитель, информационные выходы и информационные входы которого являются соответственно информационными выходами и первыми информационнлми входами устройства, адресные входы первого накопителя являются адресными входами устройства и подключены к выходам мультиплексора, информационные входы которого подключены к выходам первого и второго счетчиков, входы первого и второго счетчиков являются соответственно первым и вторым управляющими входами устройства и подключены к входам триггера, выход которого подключен к первым управляющим входам мультиплексора и первого накопителя, отличающееся тем, что, с целью расщирения области применения устройства за счет возможности перестановки информации, оно содержит второй накопитель и блок управления, первый выход которого подключен к второму управляющему входу мультиплексора, второй и третий выходы блока управления подключены соответственно к первому и второму управляющим входам второго накопителя, адресные входы и выходы которого подключены к адресньш входам первого накопителя, информационные входы второго накопителя являются вторыми информационт ными входами устройства, четвертый, выход I блока упраэления подключен к второму управляющему входу первого накопителя, упW равляюпдий выход которого подключен к первому входу блока управления, второй вход блока управления подключен к управляющему выходу второго накопителя, д эугие входы блока управления являются соответствующими управляющими входами устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР № 407394, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Буферное запоминающее устройство | 1977 |

|

SU705517A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-10-15—Публикация

1983-06-10—Подача