оо

О)

со

4

Ф/УЯ-/ 22

1

Изобретение относится к вычислительной технике и может быть использовано в ЭВМ для контроля правильности выполнения программы.

Цель изобретения - повышение полноты контроля.

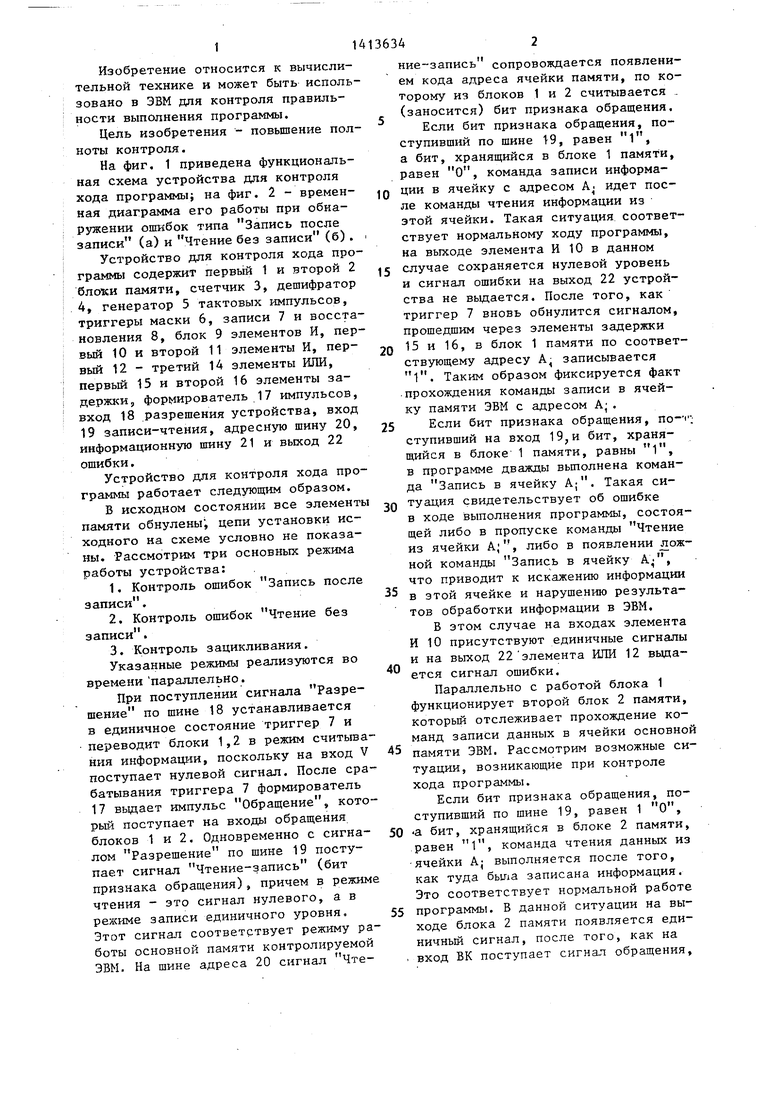

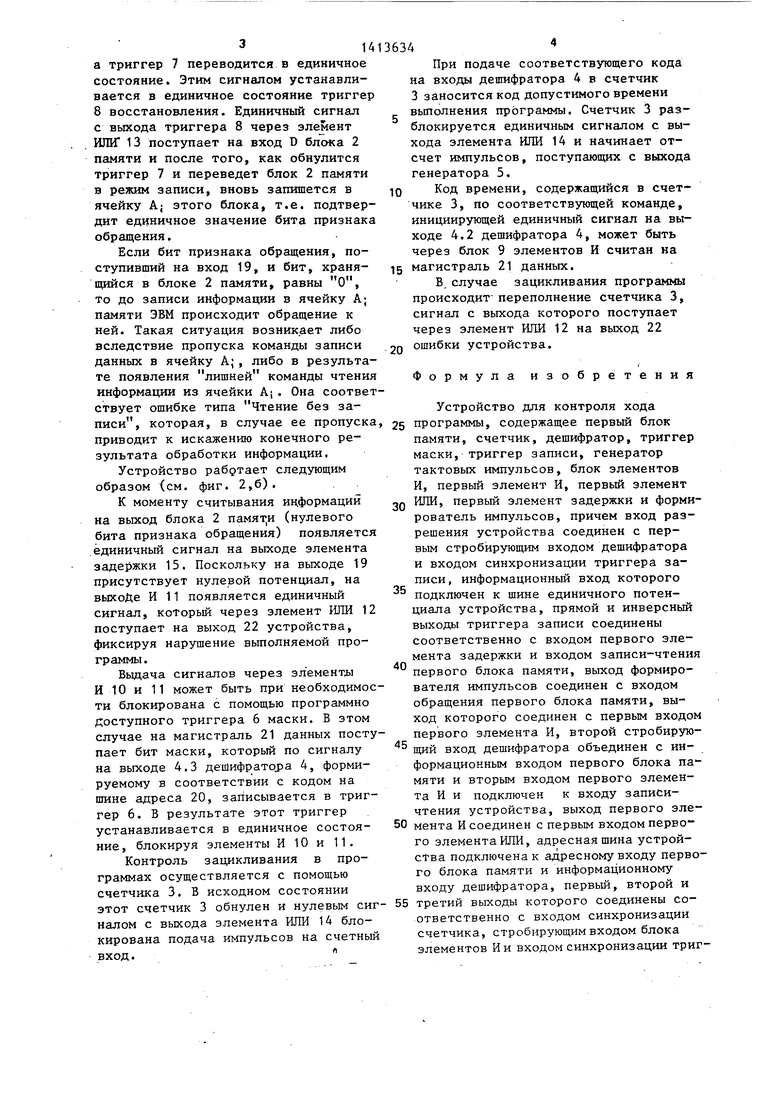

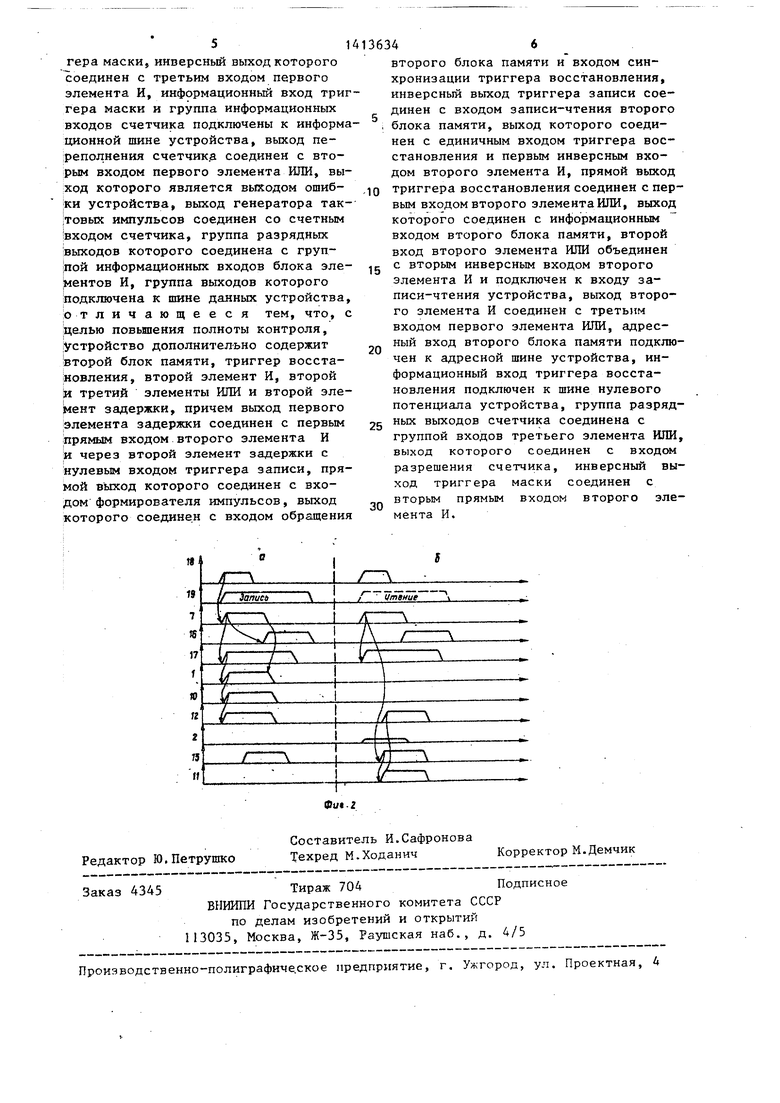

На фиг. 1 приведена функциональная схема устройства для контроля хода программы; на фиг. 2 - временная диаграмма его работы при обнаружении ошибок типа Запись после записи (а) и Чтение без записи (б) .

Устройство для контроля хода программы содержит первьш 1 и второй 2 блоки памяти, счетчик 3, дешифратор 4, генератор 5 тактовых импульсов, триггеры маски 6, записи 7 и восстановления 8, блок 9 элементов И, первый 10 и второй 11 элементы И, первый 12 - третий 14 элементы ИЛИ, первый 15 и второй 16 элементы за- держзси, формирователь 17 импульсов, вход 18 разрешения устройства, вход 19 записи-чтения, адресную шину 20, информационную шину 21 и выход 22 ошибки.

Устройство для контроля хода программы работает следующим образом,

В исходном состоянии все элементы памяти обнулены; цепи установки исходного на схеме условно не показаны. Рассмотрим три основных режима работы устройства:

1,Контроль ошибок Запись после записи.

2,Контроль ошибок Чтение без записи.

3,Контроль зацикливания. Указанные режимы реализуются во

времени параллельно.

При поступлении сигнала Разрешение по шине 18 устанавливается в единичное состояние триггер 7 и переводит блоки 1,2 в режим считьгаа- ния информации, поскольку на вход V поступает нулевой сигнал. После ера- батывания триггера 7 формирователь 17 вьщает импульс Обращение, кото- рьй поступает на входы обращения блоков 1 и 2. Одновременно с сигналом Разрешение по шине 19 поступает сигнал Чтение-запись (бит признака обращения), причем в режиме чтения - это сигнал нулевого, а в режиме записи единичного уровня. Этот сигнал соответствует режиму работы основной памяти контролируемой ЭВМ. На шине адреса 20 сигнал Чте136342

ние-запись сопровождается появлением кода адреса ячейки памяти, по которому из блоков 1 и 2 считывается . (заносится) бит признака обращения. Если бит признака обращения, поступивший по шине 19, равен 1, а бит, хранящийся в блоке 1 памяти, равен О, команда записи информаJQ ции в ячейку с адресом А идет после команды чтения информации из этой ячейки. Такая ситуация соответствует нормальному ходу программы, на выходе элемента И 10 в данном

15 случае сохраняется нулевой уровень и сигнал ошибки на выход 22 устройства не выдается. После того, как триггер 7 вновь обнулится сигналом, прошедшим через элементы задержки

2Q 15 и 16, в блок 1 памяти по соответствующему адресу А, записывается 1, Таким образом фиксируется факт прохождения команды записи в ячейку памяти ЭВМ с адресом А;,

25 Если бит признака обращения, no- i : ступивший на вход 19,и бит, хранящийся в блоке 1 памяти, равны 1, в программе дважды вьтолнена команда Запись в ячейку А;, Такая си3Q туация свидетельствует об ошибке

в ходе выполнения программы, состоящей либо в пропуске команды Чтение из ячейки А;, либо в появлении .ложной команды Запись в ячейку А-, что приводит к искажению информации

в этой ячейке и нарушению результатов обработки информации в ЭВМ.

В этом случае на входах элемента И 10 присутствуют единичные сигналы и на выход 22 элемента ИПИ 12 выдается сигнал ошибки.

Параллельно с работой блока 1 функционирует второй блок 2 памяти, который отслеживает прохождение команд записи данных в ячейки основной

5 памяти ЭВМ. Рассмотрим возможные ситуации, возникающие при контроле хода программы.

Если бит признака обращения, поступивший по шине 19, равен 1 О,

50 -а бит, хранящийся в блоке 2 памяти, .равен l, команда чтения данных из ячейки AJ выполняется после того, как туда бьша записана информация. Это соответствует нормальной работе

55 программы, В данной ситуации на выходе блока 2 памяти появляется единичный сигнал, после того, как на . вход ВК поступает сигнал обращения.

40

314

а триггер 7 переводится в единичное состояние. Этим сигналом устанавливается в единичное состояние триггер 8 восстановления. Единичный сигнал с выхода триггера 8 через элемент ИЛИ 13 поступает на вход D блока 2 памяти и после того, как обнулится триггер 7 и переведет блок 2 памяти в режим записи, вновь запишется в ячейку AJ этого блока, т.е. подтвердит единичное значение бита признака обращения.

Если бит признака обращения, поступивший на вход 19, и бит, хранящийся в блоке 2 памяти, равны О, то до записи информации в ячейку А; памяти ЭВМ происходит обращение к ней. Такая ситуация возникает либо вследствие пропуска команды записи данных в ячейку А;, либо в результате появления лишней команды чтения информации из ячейки А;. Она соответствует ошибке типа Чтение без записи, которая, в случае ее пропуска приводит к искажению конечного результата обработки информации.

Устройство рабдтает следующим образом (см. фиг. 2,6).

К моменту считывания информации на выход блока 2 памятки (нулевого бита признака обращения) появляется единичный сигнал на выходе элемента задержки 15. Поскольку на выходе 19 присутствует нулевой потенциал, на выхоДе И 11 появляется единичный сигнал, который через элемент ИЛИ 12 поступает на выход 22 устройства, фиксируя нарушение выполняемой программы.

Выдача сигналов через элементы И 10 и 11 может быть при необходимости блокирована с помощью программно доступного триггера 6 маски. В этом случае на магистраль 21 данных поступает бит маски, который по сигналу на выходе 4.3 дешифратод)а 4, формируемому в соответствии с кодом на шине адреса 20, записывается в триггер 6. В результате этот триггер устанавливается в единичное состояние, блокируя элементы И 10 и 11.

Контроль зацикливания в программах осуществляется с помощью счетчика 3. В исходном состоянии этот счетчик 3 обнулен и нулевьм сигналом с выхода элемента ИЛИ 14 блокирована подача импульсов на счетный вход.

634

При подаче соответствующего кода на входы дешифратора 4 в счетчик 3 заносится код допустимого времени выполнения программы. Счетчик 3 разблокируется единичным сигналом с выхода элемента ИЛИ 14 и начинает отсчет импульсов, поступающих с выхода генератора 5.

0 Код времени, содержащийся в счетчике 3, по соответствующей команде, инициирующей единичный сигнал на выходе 4.2 дешифратора 4, может быть через блок 9 элементов И считан на

5 магистраль 21 данных.

В, случае зацикливания программы происходит переполнение счетчика 3, сигнал с выхода которого поступает через элемент ИЛИ 12 на выход 22

Q ошибки устройства.

I

Формула изобретения

Устройство для контроля хода

5 программы, содержащее первый блок памяти, счетчик, дешифратор, триггер маски, триггер записи, генератор тактовых импульсов, блок элементов И, первый элемент И, первый элемент

0 ИЛИ, первый элемент задержки и формирователь импульсов, причем вход разрешения устройства соединен с первым стробирующим входом дешифратора и входом синхронизации триггера записи, информационный вход которого подключен к шине единичного потенциала устройства, прямой и инверсный выходы триггера записи соединены соответственно с входом первого элемента задержки и входом записи-чтения первого блока памяти, выход формирователя импульсов соединен с входом обращения первого блока памяти, выход которого соединен с первым входом первого элемента И, второй стробирую щий вход дешифратора объединен с информационным входом первого блока мяти и вторым входом первого элемента И и подключен к входу записи- чтения устройства, выход первого эле0 мента И соединен с первым входом первого элемента ИЛИ, адресная шина устройства подключена к адресному входу первого блока памяти и информационному входу дешифратора, первый, второй и

5 третий выходы которого соединены соответственно с входом синхронизации счетчика, стробирующим входом блока элементов И и входом синхронизации триг5

0

j-epa маски, инверсный выход которого соединен с третьим входом первого элемента И, информационный вход триг Гера маски и группа информационных входов счетчика подключены к информационной шине устройства, выход переполнения счетчикд соединен с вторым входом первого элемента ИЛИ, выход которого является выходом ошибки устройства, выход генератора так- |товых импульсов соединен со счетным |входом счетчика, группа разрядных :выходов которого соединена с группой информационных входов блока эле- ентов И, группа выходов которого подключена к шине данных устройства, ;отличающееся тем, что, с |Цельго повьвпения полноты контроля, |Устройство дополнительно содержит второй блок памяти, триггер восста- Иовления, второй элемент И, второй И третий элементы ИЛИ и второй элемент задержки, причем выход первого элемента задержки соединен с первым прямым входом второго элемента И и через второй элемент задержки с нулевым входом триггера записи, прямой выход которого соединен с входом формирователя импульсов, выход которого соедине.н с входом обращения

0

5

второго блока памяти и входом синхронизации триггера восстановления, инверсный выход триггера записи соединен с входом записи-чтения второго блока памяти, выход которого соединен с единичным входом триггера восстановления и первым инверсным входом второго элемента И, прямой выход триггера восстановления соединен с первым входом второго элемента ИЖ, выход которого соединен с информационным входом второго блока памяти, второй вход второго элемента ИЛИ объединен с вторым инверсным входом второго элемента И и подключен к входу записи-чтения устройства, выход второ го элемента И соединен с третьим входом первого элемента ИЛИ, адрес- Q ный вход второго блока памяти подключен к адресной шине устройства, информационный вход триггера восстановления подключен к шине нулевого потенциала устройства, группа разрядных выходов счетчика соединена с группой входов третьего элемента ИЛИ, выход которого соединен с входсм разрешения счетчика, инверсный выход триггера маски соединен с вторым прямым входом второго элемента И.

5

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля хода программ ЭВМ | 1987 |

|

SU1430960A1 |

| Устройство для контроля хода программы | 1986 |

|

SU1328819A2 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Устройство для запоминания состояний процессора | 1985 |

|

SU1278858A1 |

| Устройство для сопряжения абонентов с каналом связи | 1987 |

|

SU1432537A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

Изобретение относится к вычислительной технике и может быть ис пользовано в ЭВМ для контроля правильности выполнения программ. Цель изобретения - повышение полноты контроля. Устройство для контроля хода программы содержит первый 1 и второй 2 блоки памяти, счетчик 3, дешифратор 4, генератор 5 импульсов, триггеры маски 6, записи 7 и восстановления 8, блок 9 элементов И, первый 10 и второй 11 элементы И, первый 12, второй 13 и третий 14 элементы ИЛИ, первый 15 и второй 16 элементы задержки, формирователь 17 импульсов. Новыми элементами в устройстве являются второй 2 блок памяти, триггер 8 восстановления, второй элемент И 11, второй 13.и третий 14 элементы ИЛИ, второй элемент задержки 16. Преимущество устройства состоит в обеспечении большей полноты контроля за счет обнаружения более, широкого класса ошибок в программах. 2 ил. fg о сл

| Устройство для контроля хода программ | 1980 |

|

SU894713A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля хода программы | 1984 |

|

SU1211735A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-07-30—Публикация

1987-01-19—Подача