4ib

О

со ;о

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для подключения источников информации к общей магистрали | 1985 |

|

SU1290325A1 |

| Многоканальное устройство для подключения источников информации к общей магистрали | 1987 |

|

SU1432539A2 |

| Устройство для сопряжения источника и приемника информации | 1986 |

|

SU1381530A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1312646A1 |

| Устройство для управления динамической памятью | 1987 |

|

SU1524089A1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ МАГИСТРАЛЕЙ | 1990 |

|

RU2017210C1 |

| Устройство для проверки выполнения последовательности команд микропроцессора | 1984 |

|

SU1247874A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1444893A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1257704A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении буферных запоминающих устройств каналов и устройств обмена. Цель изобретения - расширение области применения устройства за счет организации работы устройства с асинхронными сигналами записи и чтения. Устройство содержит счетчик 1 объема накопителя, счетчики адреса записи 2 и чтения 3, элемент ИЛИ 4, мультиплексор 5, накопитель 6, выходной регистр числа 7, элемент И 8, блок синхронизации 9, злемент И 10, триггер 11 и одновибратор 12. 1 з.п. ф-лы, 6 ил.

(рИс.1

11А

Изобретение относится к вычислительной технике и может быть использовано при построении буферных запоминающих устройств каналов и уст- ройств обмена

Целью изобретения является расширение области применения устройства за счет организации работы устройства с асинхронными сигналами записи и чтения.

На фиг. 1 изображена структурная схема буферного запоминающего устрой

ства; на фиг. 2 - структурная схема блока синхронизации; на фиг. 3 - структурная схема накопителя; на фиг. 4 - временные диаграммы записи поступающей информации в буфер; на фиг. 5 - временные диаграммы автоматического чтения данных из буфера; на фиг. 6 - совмещенные временные диаграммы записи-чтения данных из буфера.

Буферное запоминающее устройство

ных к записи разрешены первые два. В случае разрешения записи задним фронтом сигнала С2, прошедшего через открытый (сигналом лог. 1 Выбор) злемент И 37, запускается одновибра- тор S 29. Сформированный одновибрато- ром S 29 импульс отрицательной полярности поступает на элемент И-НЕ 32, блокируя запуск чтения, и эле15 мент И-НЕ 33 передним фронтом запуска ет одновибратор S 30. Сформированный одновибратором S 30 отрицательный импульс (с инверсного выхода) поступает на элемент И-НЕ 32, блокируя механизм

20 чтения, а импульс с прямого выхода не проходит через закрытый (отрицательным импульсом одновибратора S 29) элемент ЗА.

Таким образом, на выходе 23 блока

содержит счетчик 1 объема накопителя, 25 9 синхронизации (фиг. 1) поддержива- счетчик 2 адреса записи, счетчик 3 адреса чтения, элбмент ИЛИ 4, мультиплексор 5, накопитель 6, выходной регистр 7 числа, элемент И 8, блок 9 синхронизации, элемент И 10, триггер 11, одновибратор 12, информационный вход 13, информационный выход 14, Ьинхровходы 15 и 16, вход 17 Выбор кристалла, вход 18 синхрочастоты, вход 19 чтения, вход 20 готовности.

45

вход 21 Буфер пуст, выход 22 разрешения записи, выход 23 разрешения чтения, выход 24 мультиплексора,,информационные входы 25 и 26 мультиплексора, информационный вход 27 регист- 40 ра 7.

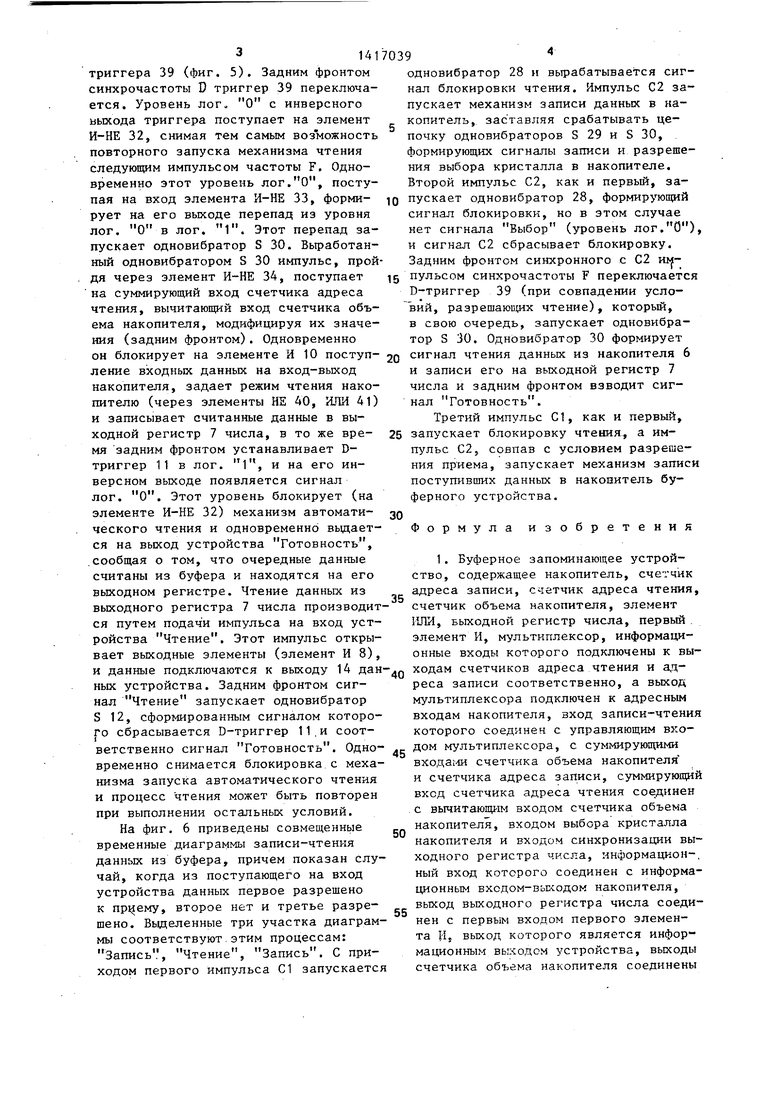

Блок 9 синхронизации состоит из одновибраторов 28 - 30, элементов И-НЕ 31 - 34, элементов НЕ 35 и 36, элементов И 37 и 38 и триггера 39.

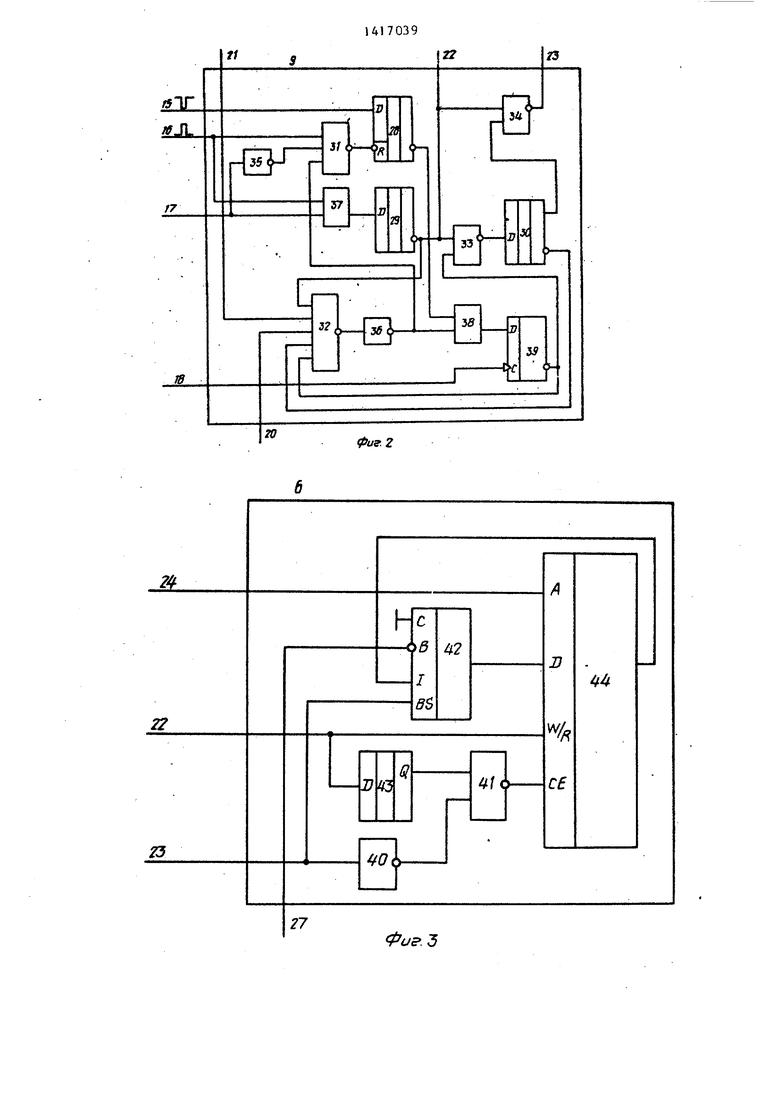

Накопитель 6 состоит из элементов НЕ 40, 1ШИ 41, двунаправленного клапана 42, одновибратора 43, ОЗУ 44.

Устройство работает следующим образом.

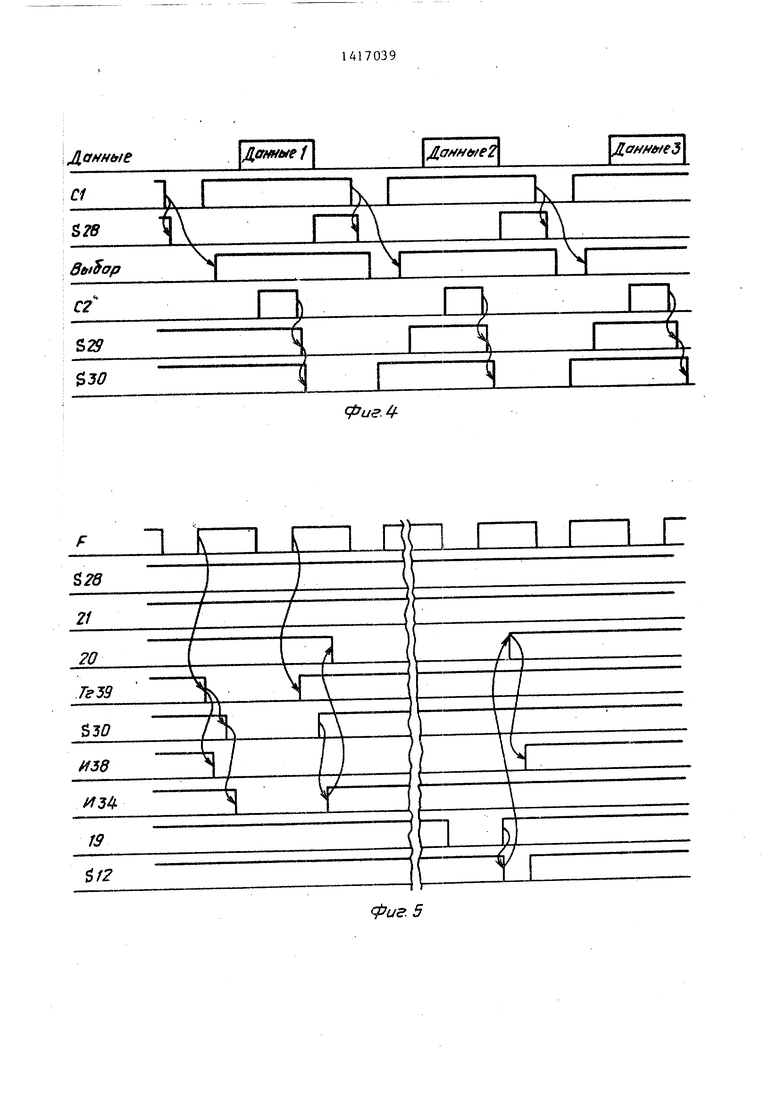

В выполнении операции записи данных (см. фиг; 4) задействованы следующие сигналы: синхросигнал С1, поступающий перед данными, сигнал Выбор, разрешающий запись данных, и синхросигнал С2, стробирующий данные. Передним фронтом сигнала С1 запускается одновибратор 28, который фop tиpy- ет ,на выходе отрицательный импульс.

ется потенциал лог. 1 , открывающий элемент И 10, для подключения данных к входу накопителя. В то же время импульс записи на выходе 22 подключает 30 к накопителю 6 текущее значение счетчика 2 адреса записи, формирует в накопителе импульс выбора кристалла, записывая в накопитель поступившие данные, и задним фронтом увеличивает содержимое счетчика 1 объема накопителя. В случае неразрешения записи (см. фиг. 4, Данные 3) синхросигнал .G2 не запускает одновибратор 29, а, пройдя через элемент И-НЕ 31, поступает на вход R одновибратора S 23 и снимает сигнал блокировки механизма чтения. Таким образом, в последующих тактах (при выполнении всех прочих условий) возможно включение механизма автоматического чтения.

Автоматическое чтение (фиг. 5) выполняется следующим образом.

Для запуска чтения необходимо совпадение условий: отсутствие записи в накопитель, наличие данных в накопителе () и отсутствие сигнала Готовность, говорящего об отсутствии данных в выходном регистре 7 числа. При совпадении этих условий вьфа батывается сигнал лог. 1, который поступает на вход элемента И 38. При отсутствии блокирующего сигнала с одновибратора S 28 сигнал лог. 1 ступает на информационный вход D50

55

блокирующий на один такт на элементе И 38 механизм пуска автоматического чтения. На фиг. 4 рассмотрен случай, когда из трех поступивших дан0

ных к записи разрешены первые два. В случае разрешения записи задним фронтом сигнала С2, прошедшего через открытый (сигналом лог. 1 Выбор) злемент И 37, запускается одновибра- тор S 29. Сформированный одновибрато- ром S 29 импульс отрицательной полярности поступает на элемент И-НЕ 32, блокируя запуск чтения, и эле5 мент И-НЕ 33 передним фронтом запускает одновибратор S 30. Сформированный одновибратором S 30 отрицательный импульс (с инверсного выхода) поступает на элемент И-НЕ 32, блокируя механизм

0 чтения, а импульс с прямого выхода не проходит через закрытый (отрицательным импульсом одновибратора S 29) элемент ЗА.

Таким образом, на выходе 23 блока

25 9 синхронизации (фиг. 1) поддержива-

5

0

ется потенциал лог. 1 , открывающий элемент И 10, для подключения данных к входу накопителя. В то же время импульс записи на выходе 22 подключает 30 к накопителю 6 текущее значение счетчика 2 адреса записи, формирует в накопителе импульс выбора кристалла, записывая в накопитель поступившие данные, и задним фронтом увеличивает содержимое счетчика 1 объема накопителя. В случае неразрешения записи (см. фиг. 4, Данные 3) синхросигнал .G2 не запускает одновибратор 29, а, пройдя через элемент И-НЕ 31, поступает на вход R одновибратора S 23 и снимает сигнал блокировки механизма чтения. Таким образом, в последующих тактах (при выполнении всех прочих условий) возможно включение механизма автоматического чтения.

Автоматическое чтение (фиг. 5) выполняется следующим образом.

Для запуска чтения необходимо совпадение условий: отсутствие записи в накопитель, наличие данных в накопителе () и отсутствие сигнала Готовность, говорящего об отсутствии данных в выходном регистре 7 числа. При совпадении этих условий вьфа батывается сигнал лог. 1, который поступает на вход элемента И 38. При отсутствии блокирующего сигнала с одновибратора S 28 сигнал лог. 1 ступает на информационный вход D0

5

триггера 39 (фиг, 5). Задним фронтом синхрочастоты D триггер 39 переключается. Уровень лог о О с инверсного выхода триггера поступает на элемент И-НЕ 32, снимая тем самым возможность повторного запуска механизма чтения следующим импульсом частоты F. Одновременно этот уровень лог,О, поступая на вход элемента И-НЕ 33, формирует на его выходе перепад из уровня лог, О в лог, 1, Этот перепад запускает одновибратор S 30, Вьфаботан- ный одновибратором S 30 импульс, пройдя через элемент И-НЕ 34, поступает на суммирующий вход счетчика адреса чтения, вычитающий вход счетчика объема накопителя, модифицируя их значения (задним фронтом), Одновременно

он блокирует на элементе И 10 поступ- 20 сигнал чтения данных из накопителя 6

ление входных данных на вход-выход накопителя, задает режим чтения накопителю (через элементы НЕ 40, ИЛИ 41) и записывает считанные данные в выходной регистр 7 числа, в то же вре

мя задним фронтом устанавливает D- триггер 11 в лог, 1, и на его инверсном выходе появляется сигнал лог, О, Этот уровень блокирует (на элементе И-НЕ 32) механизм автоматического чтения и одновременно выдается на выход устройства Готовность, .сообщая о том, что очередные данные считаны из буфера и находятся на его выходном регистре. Чтение данных из выходного регистра 7 числа производится путем подачи импульса на вход устройства Чтение, Этот импульс открывает выходные элементы (элемент И 8), и данные подключаются к выходу 14 дан ных устройства. Задним фронтом сигнал Чтение запускает одновибратор S 12, сформированным сигналом которого сбрасывается D-триггер 11.и соответственно сигнал Готовность, Одновременно снимается блокировка с механизма запуска автоматического чтения и процесс чтения может быть повторен при выполнении остальных условий,

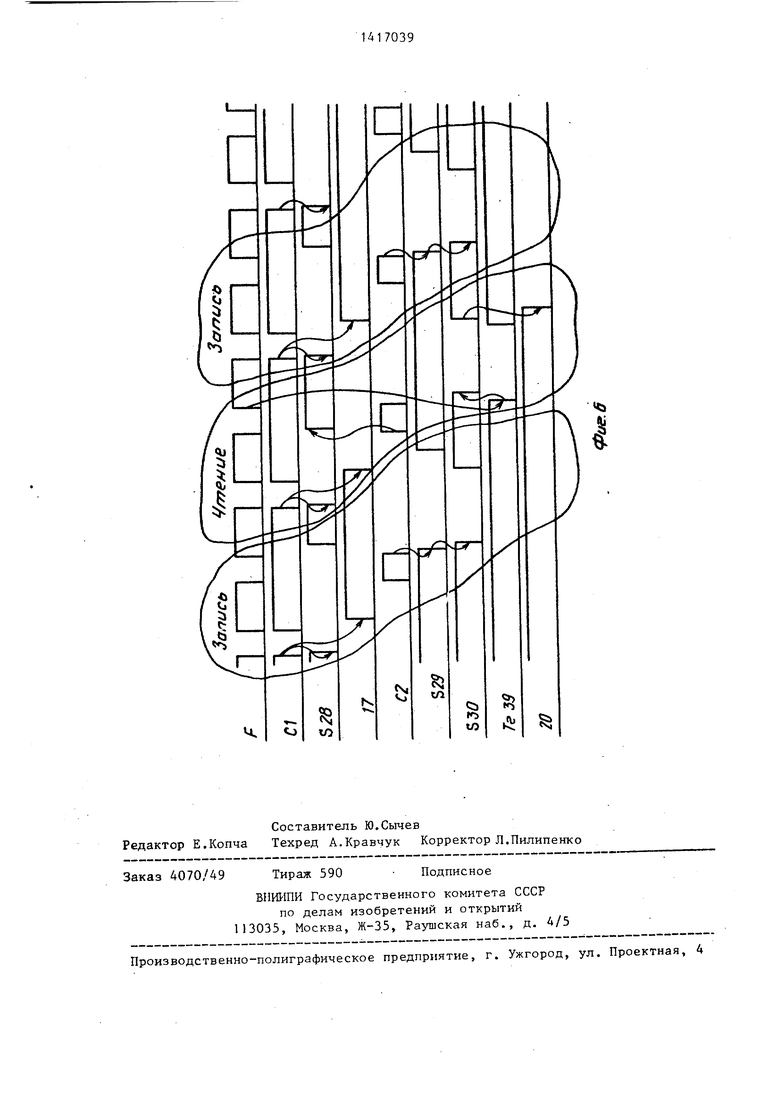

На фиг. 6 приведены совмещенные временные диаграммы записи-чтения данных из буфера, причем показан случай, когда из поступающего на вход устройства данных первое разрешено к прц.ему, второе нет и третье разрешено. Выделенные три участка диаграммы соответствуют,этим процессам: Запись, Чтение, Запись, С приходом первого импульса С1 запускается

одновибратор 28 и вьфабатывается сигнал блокировки чтения. Импульс С2 запускает механизм записи данных в накопитель, заставляя срабатывать цепочку одновибраторов S 29 и S 30, формирующих сигналы записи и разрешения выбора кристалла в накопителе. Второй импульс С2, как и первый, запускает одновибратор 28, формирующий сигнал блокировки, но в этом случае нет сигнала Выбор (уровень лог,О), и сигнал С2 сбрасывает блокировку. Задним фронтом синхронного с С2 импульсом синхрочастоты F переключается D-триггер 39 (при совпадении условий, разрешающих чтение), который, в свою очередь, запускает одновибратор S 30, Одновибратор 30 формирует

и записи его на выходной регистр 7 числа и задним фронтом взводит сигнал Готовность,

Третий импульс С1, как и первый, 25 запускает блокировку чтения, а импульс C2f совпав с условием разрешения приема, запускает механизм записи поступивших данных в накопитель буферного устройства.

ормула изобретения

1, Буферное запоминающее устройство, содержащее накопитель, счетчик адреса записи, счетчик адреса чтения, счетчик объема накопителя, элемент ШИ, выходной регистр числа, первый . элемент И, мультиплексор, информационные входы которого подключены к выходам счетчиков адреса чтения и а,ц- реса записи соответственно, а выход мультиплексора подключен к адресным входам накопителя, вход записи-чтения которого соединен с управляющим входом мультиплексора, с суммирующими входаг-ш счетчика объема накопителя и счетчика адреса записи, суммирующий вход счетчика адреса чтения соединен с вычитающим входом счетчика объема накопителя, входом выбора кристалла накопителя и входом синхронизации выходного регистра числа, ннформацион-, ный вход которого соединен с информационным входом-выходом накопителя, выход выходного регистра числа соединен с первь м входом первого элемента И, выход которого является информационным выходом устройства, выходы счетчика объема накопителя соединены

с входами элемента ИЛИ, о т л и - чающееся тем, что, с целью расширения области применения устройства за счет организации работы, устройства .с асинхронными сигналами записи и чтения, в него введены блок синхронизации, второй элемент И, первый одновибратор и первый триггер причем выход второго элемента И соединен с инфбрмационным входом регистра, первый вход второго элемента И является информационным входом уст- ройства, второй вход второго элемента И соединен с входами синхронизации регистра и первого триггера и подключен к выходу разрешения чтения блока синхронизации, выход разрешения записи которого соединен с входом записи-чтения накопителя, выход элемента ИЛИ подключен к входу Буфер пуст блока синхронизации, первый синхровход которого является первым синхровходом устройства, второй синхровход блока синхронизации является вторым синхровходом устройства, вход выбора блока синхронизации является входом йыбора кристалла устройства, вход синхрочастоты блока син хронизации является входом синхрочастоты устройства, инверсный выход первого триггера подключен к входу Готовность блока синхронизации и Является соответствующим выходом уст ройства, вход установки первого триггера соединен с инверсным выходом первого одновибратора, вход запуска которого соединен с вторым входом первого элемента И и является входом чтения устройства,

2, Ус тройство по п. 1, отличающееся тем, что блок синхронизации содержит второй, третий и четвертый одновибраторы, первый, второй, третий и четвертый элементы И-НЕ, первый и второй элементы НЕ, третий и четвертый элементы И и второй триггер, причем инверсный выход

второго одновибратора соединен с первым входом четвертого элемента И, выход которого соединен с информационным входом второго триггера, вход синхронизации которого является входом синхрочастоты блока синхронизации, а инверсный выход второго триггера соединен с вторым входом третьего элемента И-НЕ и пятым входом второго элемента И-НЕ, выход которого соединен с входом второго элемента НЕ, выход которого подключен к второ-« му входу четвертого элемента И и

g третьему входу первого элемента И-НЕ, второй вход которого подключен к выходу первого элемента -НЕ, вход которого соединен с вторым входом третьего элемента И и является входом ВыQ бор блока синхронизации, первый вход третьего элемента И соединен с первым входом первого элемента И-НЕ и является вторым синхровходом блока , синхронизации, выход первого элемен5 та И-НЕ соединен с входом блокировки второго одновибратора, инверсный вход запуска которого является первым синхровходом блока синхронизации, выход третьего элемента И подключен к ин0 вереному входу запуска третьего одно- вибратора, инверсный выход которого соединен с первыми входами второго, третьего и четвертого элементов И-НЕ и яапяется выходом разрешения записи блока синхронизации, выход третьего элемента И-НЕ подключен к прямому входу запуска четвертого одновибратора, инверсный выход которого соединен с четвертьм входом второго элемента И-НЕ, третий вход которого является входом Готовность блока синхронизации, прямой выход четвертого одновибратора подключен к второму входу четвертого элемента И-НЕ, выход которого является выходом разрешения чтения блока синхронизации, второй вход второго элемента И-НЕ является входом Буфер пуст блока синхронизации.

5

0

5

27

Фиг. 5

фие. 5

Составитель Ю.Сычев Редактор Е.Копча Техред А.Кравчук Корректор Л.Пилипенко

Заказ 4070/49

Тираж 590

ВИИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

4s

Подписное

| Патент США 4056851, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1312646A1 |

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

Авторы

Даты

1988-08-15—Публикация

1987-01-12—Подача