I памяти, счетчик 2 адреса чтения, счетчик Л адреса записи, мультиплексор 4, счетчик о данных, элемент ИЛИ 6, регистр 7, элемент И 8, элементы ИЛИ 9 и 10, дешифратор 11, трип ср 12, элемент 13, одновибра- тор 14, буферный счетчик 15, вход 16 записи, вход 17 чтения, информационный вход 18, вход 19 идентификатора нереиолнения памяти. Запись данных, поступающих на вход 16, осуществляется в блок 1 но сиг - на. |у записи на входе 16 по адресу, посту- паю1лему через мультиплексор 4 на адрес- Hi.ie входы блока 1. Считывание данных осуп1ествляется по сигналу считывания на входе 17 по адресу, поступающему через 1у.1ьти |лексор 4 на адресные входы блока

1

Изобретение относится к вычислительной технике н может быть иснользовано ||()и построении буферных запоминающих сгройств каналов связи и устройств обме- пл ин()ормацией.

Цель изобретения - расщирение функ- 11Иг)пал1)Ных возможностей устройства за счет (j)KKcanHH объема потерянных данных при переполпении памяти.

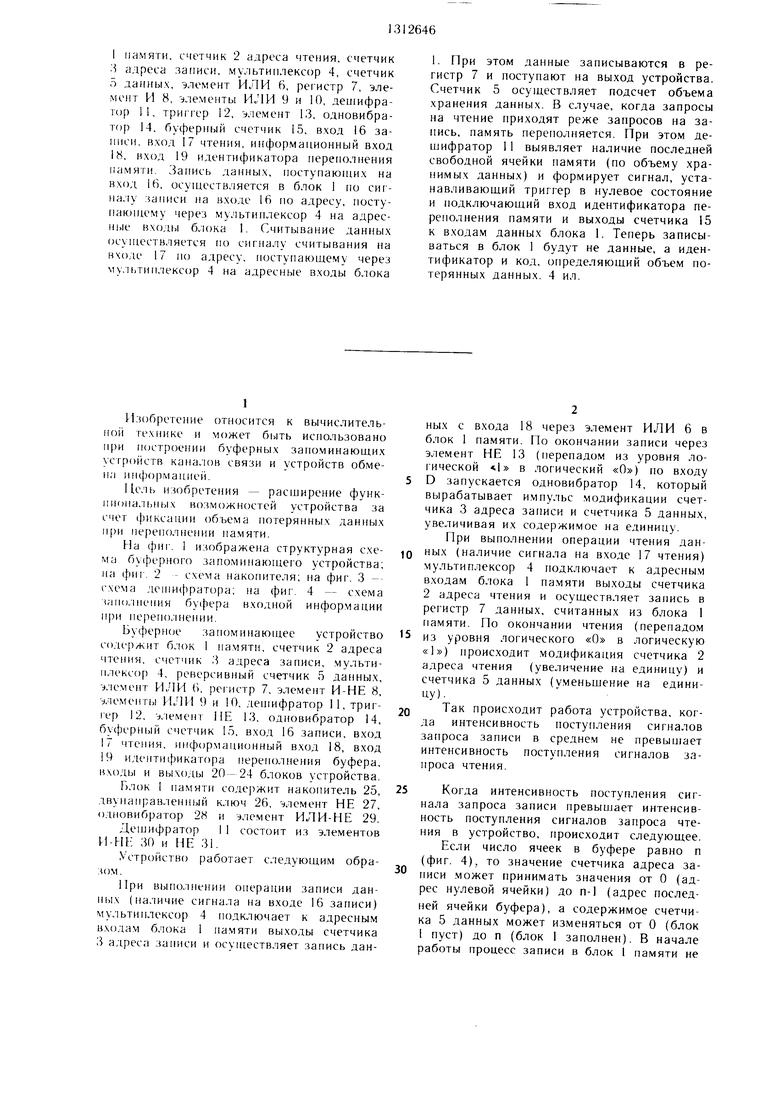

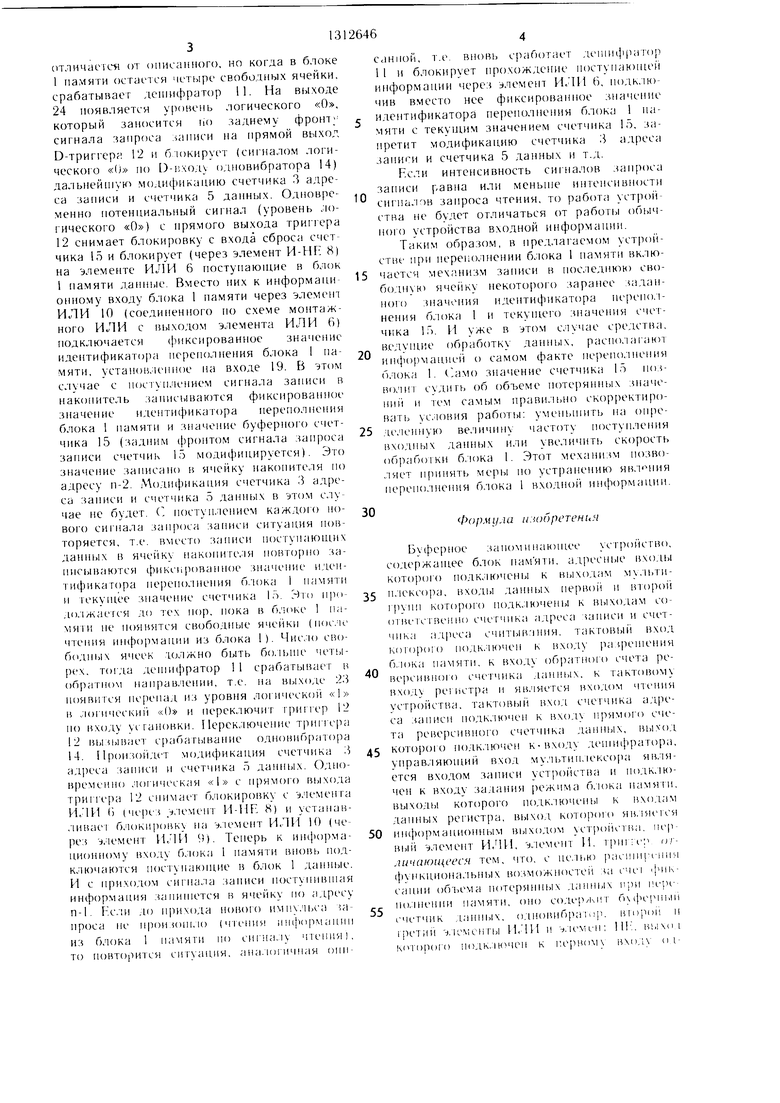

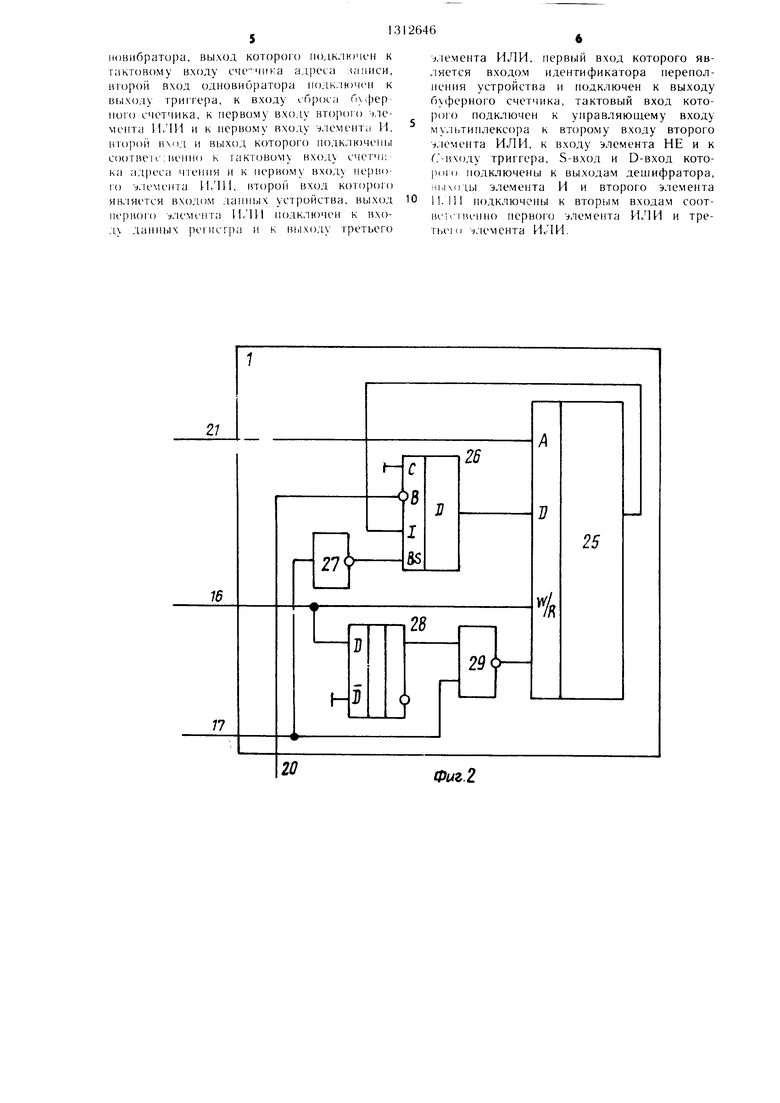

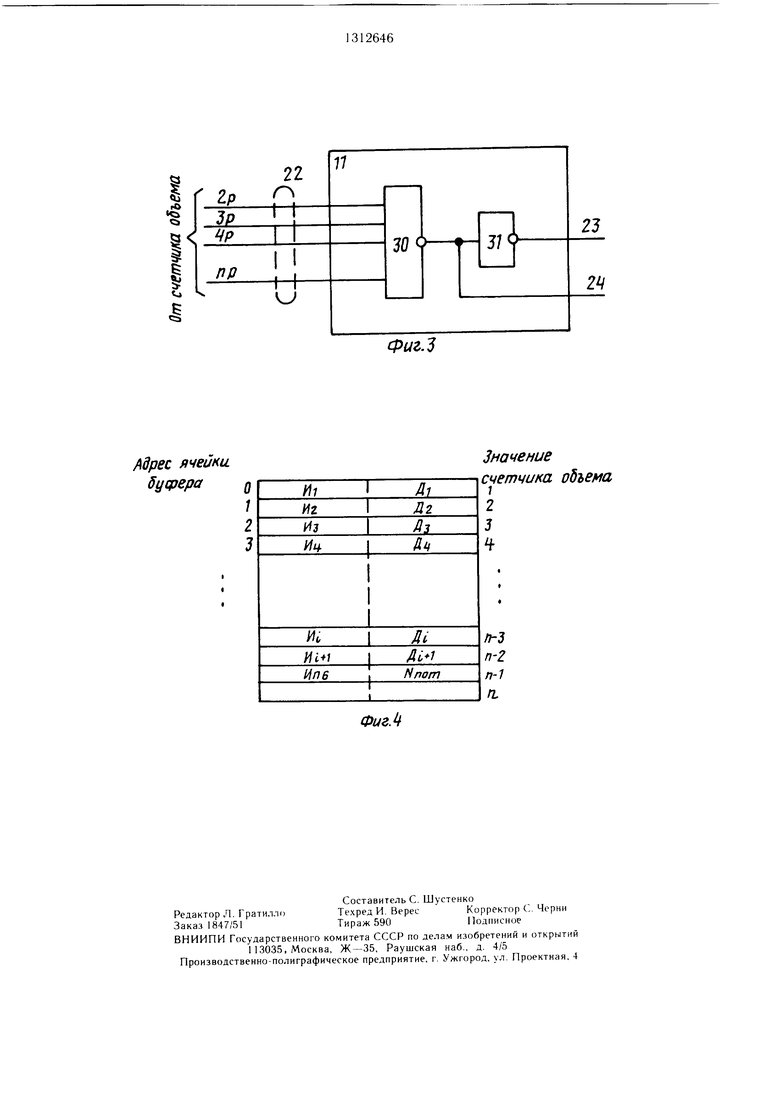

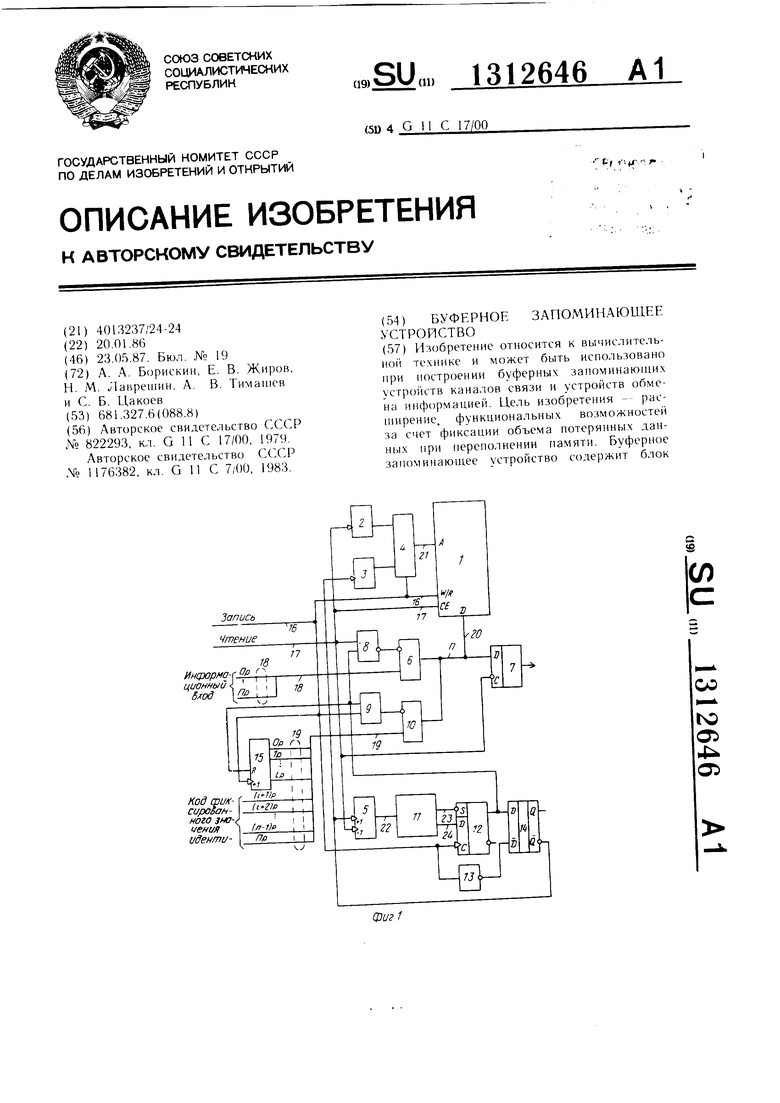

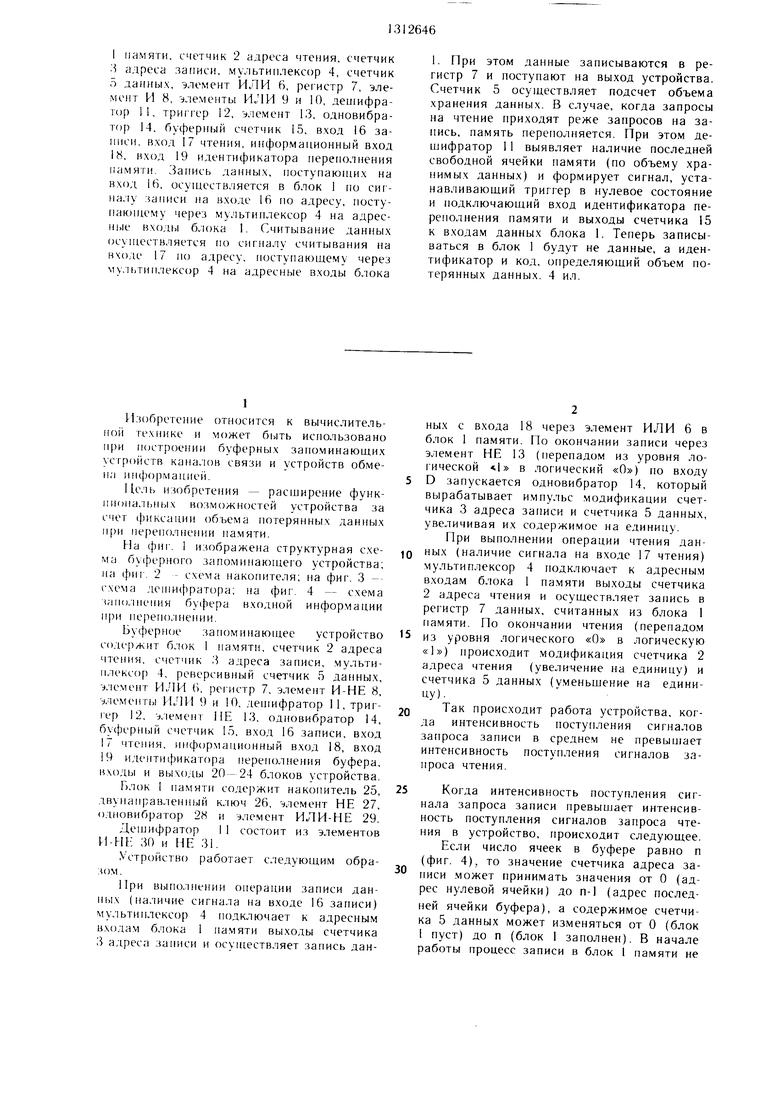

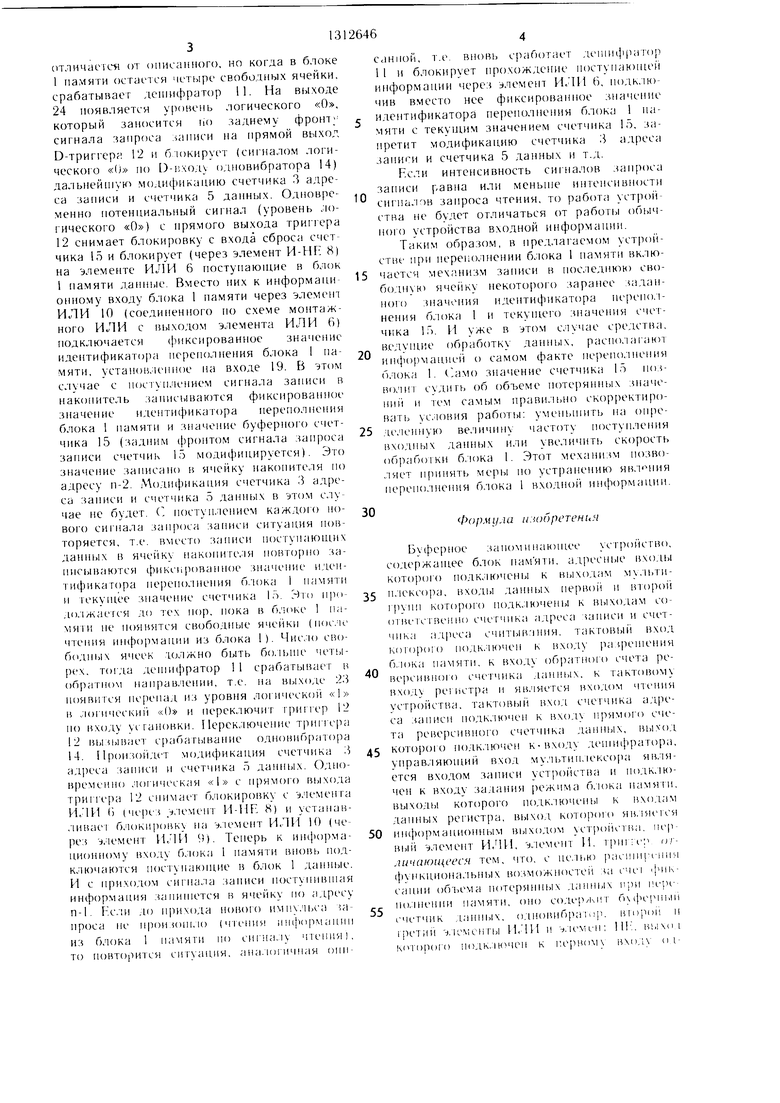

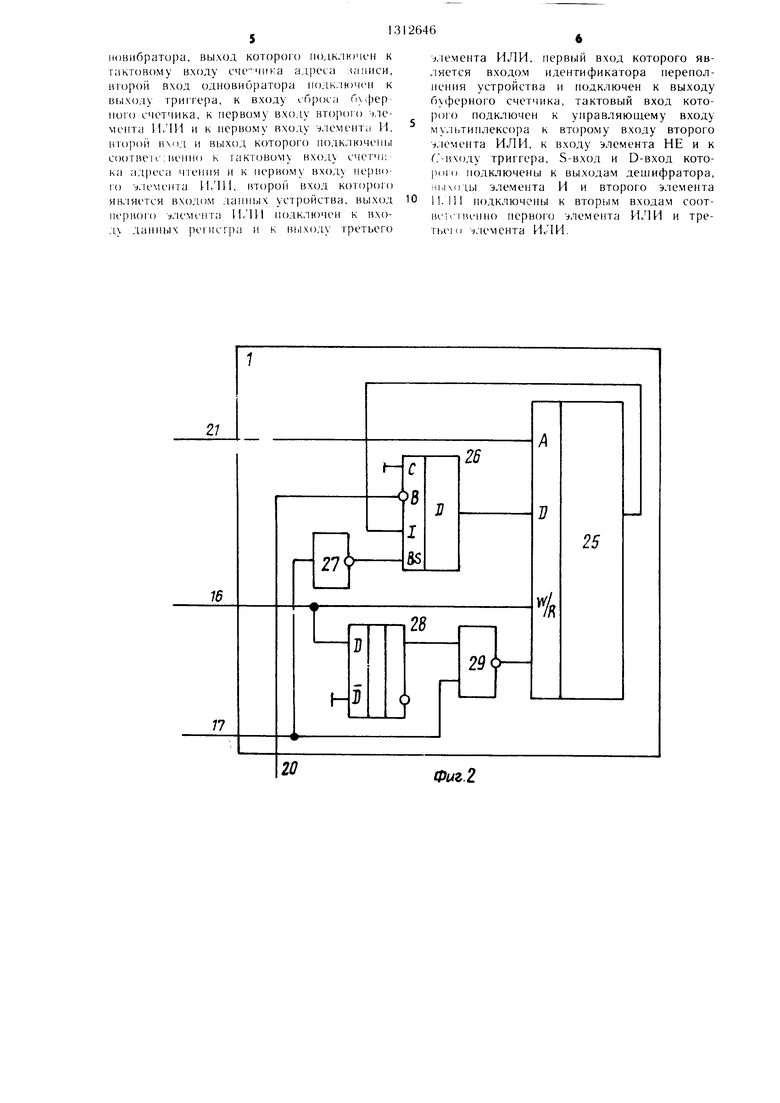

Иа (J5HI-. 1 изображена структурная схема бу|)ерного запоминающего устройства; на (()иг. 2 - схема накопителя; на фиг. 3 - схема деп1И(|)ратс)ра; на фиг . 4 - схема запос шсния буфера входной информации п|)и переполнении.

Бyфepн(Je запоминающее устройство содс ржит б. юк I памяти, счетчик 2 адреса чтения, счетчик 3 адреса записи, мультиплексор 4, реверсивпый счетчик 5 данных, :, 1смент ИЛИ ( регистр 7, элемент И-НЕ 8, элементы ИЛИ 9 и 10, дешифратор 11, триггер 12, у,темент НЕ 13, одновибратор 14, бу(})срньп 1 счетчик 15, вход 16 записи, вход 17 чтения, информационный вход 18, вход 19 идентификатора 1 еренолнения буфера, входы и выходы 20-24 блоков устройства.

Блок I памяти содержит накопитель 25, двунаправлеппый ключ 26, элемент ИЕ 27, одновибратор 28 и элемент ИЛИ-НЕ 29.

Дец нфратор I 1 состоит из элементов И-НЕ 30 и ИЕ 31.

Устройство работает следующим образом.

При выполнении операции записи дан- Н1)1Х (наличие сигнала на входе 16 записи) мультиплексор 4 юдключает к адресным в.чодам блока 1 памяти выходы счетчика 3 адреса записи и осуществляет запись дан1. При этом данные записываются в регистр 7 и поступают на выход устройства. Счетчик 5 осуществляет подсчет объема хранения данных. В случае, когда запросы на чтение приходят реже запросов на запись, память переполняется. При этом дешифратор 11 выявляет наличие последней свободной ячейки памяти (по объему хранимых данных) и формирует сигнал, устанавливающий триггер в нулевое состояние и нодключаюший вход идентификатора переполнения памяти и выходы счетчика 15 к входам данных блока 1. Теперь записываться в блок 1 будут не данные, а идентификатор и код, определяющий объем потерянных данных. 4 ил.

ных с входа 18 через элемент ИЛИ 6 в блок 1 памяти. По окончании записи через элемент ИЕ 13 (Перепадом из уровня логической . в логический «О) по входу

D запускается одновибратор 14, который вырабатывает и.мпульс .модификации счетчика 3 адреса записи и счетчика 5 данных, увеличивая их содержи.мое на единицу. Ири выполнении операции чтения данO ных (наличие сигнала на входе 17 чтения) мультиплексор 4 подключает к адресным входам блока 1 па.мяти выходы счетчика 2 адреса чтения и осуществляет запись в регистр 7 данных, считанных из блока 1 памяти. По окончании чтения (перепадом

5 из уровня логического «О в логическую «1) происходит .модификация счетчика 2 адреса чтения (увеличение на единицу) и счетчика 5 данных (уменьщение на единицу) .

Q Так происходит работа устройства, когда интенсивность поступления сигналов запроса записи в средне.м не превышает интенсивность поступления сигналов запроса чтения.

5Когда интенсивность поступления сигнала запроса записи превышает интенсивность поступления сигналов запроса чтения в устройство, происходит следующее. Если число ячеек в буфере равно п (фиг. 4), то значение счетчика адреса записи .может принимать значения от О (адрес нулевой ячейки) до п-1 (адрес последней ячейки буфера), а содержимое счетчика 5 данных может изменяться от О (блок 1 пуст) до п (блок 1 заполнен). В начале работы процесс записи в блок 1 памяти не

0

отлнчаегся от описанного, но когда в блоке 1 памяти остаемся четыре свободных ячейки, срабатывает деншфратор II. На выходе 24 появляется у)овень логического «О, который заносится ilo заднему фронт сигнала запроса ; аписи на прямой выход D-триггеря 12 и бюкирует (сигналом логического «(J по О-иходу одповибратора 14) дальнеЙ1пук1 м()ди{|)иканию счетчика } адреса записи и счетчика 5 данных. Одновременно потенциальный сигнал (уровень логического «О) с нрямого выхода триггера 12 снимает блокировку с входа сброса счетчика 15 и блокирует (через элемент И-HFi 8) на элементе ИЛИ 6 посту11аюн1.ие в блок I памяти данные. Вместо них к ипформапн- опиому входу блока 1 памяти через элемент ИЛИ 10 (соединенного но схеме монтажного ИЛИ с Исходом элемента ИЛИ 6) подключается (| иксированпое значение идентификатора переполнения блока I памяти, ycTanoii.ieiiHoe на входе 19. Ei этом с. |учае с поступлением сигнала записи в нако 1итель :и1нис,1вак)тся фикспроваппое значение идентификатора переполнения блока 1 памяти и .значение буферного счетчика 15 (задним (jpoiiTOM сигнала запроса записи счетчик 15 модифицируется). Это значение занисано в ячейку накопителя по адресу п-2. одп1()икация счетчика 3 адреса заииси и счетчпка 5 данных в этом случае не будет. С. поступ.пением каждою нового си1 нала запроса за1П1си ситуация повторяется, т.е. вместо записи поступающих данных в яче11ку накониге, 1Я повгорно записываются фиксированное 3iia4ciine идентификатора переп();1нения б.тока 1 памяти и текущее зпачение счетчика 1о. )т() про- .ю.тжаегся до тех пор, пока в блоке 1 памяти пе появится свободные ячейки (пос.тс чтения ип({)ормации из блока 1). Чис.то сво- бодпых ячеек Кхижно быть б().тьп1с четырех, тогда дец|И())ратор 1 1 срабатывает и обратном направлении, т.е. па В1,|ходе 23 появигси нерепад из уровня логическоГ) «1 в ло|пчоски1( «О и переключит григгер 12 по входу yi гаповки. Иереключеппе трнг1е 1а 12 вьпывает срабатывание Г)дн()вибрато1)а 14. 11роп.3()11дет модификация счетчпка 3 адреса записи и счетчика 5 данных. Одновременно ,то1ическая «I с прямогч) выхода три1гера 12 с |имает о.юкировку с элемепга ИЛИ Г) (че)ез лемепт И-МР. 8) и устапав- ,тивает б,ток11ровку па э.темент ИЛИ 10 (через ЭсТемент ИЛИ 9). Теперь к ип(})0)ма- ционному входу блока 1 памяти вновь подключаются постунающие в блок 1 данные. И с приходом сигнала заниси поступпв1пая информация запин1ется в ячейку по адресу п-1. Нс.ти до прихода нового импу.Т1)Са ia- проса НС npontoin.u) (чтения информаппп из блока 1 памяти по сигналу чтения 1, то повторится сит уацця, ана.тогпчпая опн0

5

0

5

0

5

0

5

0

5

санпой, Т .е. вновь сработает деп1И(}1()а гор 1 I и блокирует прохождепие поступаюпип информации через элемент ИЛИ 6, подк.тю- чив вместо нее фиксированпое значение идентификатора переполнения блока 1 памяти с текупщм значением счетчика 15, за- нретит модификацию счетчика 3 адреса заииси и счетчика 5 данных и т.д.

Р.сли интенсивность сигналов зап)оса записи равна или меньп е ипгенсивности сигналов запроса чтения, то работа ycTpoii- ства пе будет отличаться от работы обычного устройства входной информации.

Таким образс)м, в пред,тагаемом устройстве при нереиолпепии блока 1 памяти включается мехг .низм загпк и в последнк ю сво- бодпук яче11ку некото(П)го заранее заданною значения идентификатора иерепо.т- нения б,тока 1 и текун1его значения счет- 4ViKa 15. И уже в этом случае средства, в.едушие обработку данных, располагают ин(5и)рмацие11 о самом факте перепо,тнспия блока 1. ( амо зпачение счетчика 15 поз- волпг судпгь об поте1)япных значе- iniii и тем самым прави.тьно скор)ектиро- вать ус.товия работы: умепьп1игь па опре- . 1е, 1е11пую ве,тичппу частоту псх тупления входпых да1пп,1х или увеличить скорость обработки б.тока 1. Этот мехашгш позволяет принять меры по устрапению явл шия переполнения б/юка 1 входной пнформацни.

Формует и:н)6ретен1,я

13y(f)epnoe запом и накмцее устройство, содержащее блок пам яти. адресные вхо.чы которого подключены к выходам му.тьти- iKiCKCopa, вход1 1 данных nepBoii и BTopoii ipynii KOTopoi o 11одк,тн)чепы к выходам со- от BL TCT веиио счетчика адреса записи и счетчпка адреса счит1)1в:111ия. тактовьп вход когорого модк.тючеп к входу разрешения б.тока памяти, к входу обратною счета реверсивною счегчпка дапи1 1х, к тактовому входу регистра, п яв.чяется входом чтч нпя ycTpoiicTBa, тактовый вхо.ч счегчика адреса записп подк,тючеп к вхо.т прямого счета реверсивного счетчпка данных, выхо.ч которого подключен к-входу деп1И1 1ратора, унравляюи1ий вход мультиплексо а яв.тя- ется входом записи устройства и подк.тю- чен к входу задания режима б.тока иамягп, выходы KOTopoiT) подключс ны к вхо.там данных решстра, выход которого яв.тжчся ин(})ормапио1шым выходом ycTpoiicrBa. IH-II вый элемепт ИЛИ, элемепт И. rpni;c; o.i- личающееся тем, что, с пе.тью расшпршпи функциональных возможпостхм за CMCI фиксации обт1ема потеряпп1 1х да1пп.1х при перс полнеппи памяти, оно сод|. б i| cpiii.ni счс тчкк .таппых, о.тновиб аьф. вюрпп п третий э.т омспгы ИЛИ п э.темен; .. BMXHI 1(тт)|1()|Ч) подк.тим1еп к |;сриому вхо.П о iиовибратора, выход которого подключен к тактовому входу сче-чика адреса записи, второй вход одновиоратора нодк.тючс-н к В1,1ходу триггера, к входу сброса б.:()ер- ного счетчика, к первому входу второю элемента И,Ч И и к первому входу адемеита И, HTOpoii )д и выход которого подключены соответс: венно к тактовому входу счетч : ка ад1)еса чтения и к первому входу первого :1лемента ИЛИ, второй вход которого является входом данных устройства, выход первого : лемснта И, 1И нодключен к входу данных регисгра и к В1,1ходу третьего

:1лемента ИЛИ, первый вход которого яв- ,тяется входом идентификатора переполнения устройства и подключен к выходу бу()зерного счетчика, тактовый вход которого подключен к управляющему входу мультиплексора к второму входу второго элемента ИЛИ, к входу элемента НЕ и к (. -входу триггера, S-вход и D-вход кото- poio подключены к выходам дешифратора, )ды элемента И и второго элемента 11.1И подключены к вторым входам COOT- ISC ггтиен но первого элемента ИЛИ и третье: о э.темента .

Адрес ячейки Sycpepa

Фиг.З

Значение

счетчика 1

2 3

п-2

П 1

П

ФигМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения абонентов с ЭВМ | 1986 |

|

SU1376091A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1236550A1 |

| Устройство для сопряжения источника и приемника информации | 1986 |

|

SU1381530A1 |

| Многоканальное устройство для подключения источников информации к общей магистрали | 1985 |

|

SU1290325A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1163357A1 |

| Устройство для сопряжения источника и приемника информации | 1986 |

|

SU1416988A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1361632A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1672527A1 |

| Устройство для управления сверхоперативной буферной памятью мультипроцессорной ЭВМ | 1981 |

|

SU980097A1 |

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1571596A1 |

И: обретение относится к вычислительной технике и может быть использовано при иостроении буферны.х запоминающих ycTpoi icTB каналов связи и устройств обмена информацией. Цель изобретения -- рас- 1нирение, функциональных возможностей за счет фиксации объема потерянных дан- ны.х нри переполнении памяти. Буферное запоминающее устройство содержит блок HHcpopMO-r.2pJ.. ционный { . ( Код спик- сироВанИогО ЗНО: ifCHl/f иденти (Л оо ND Ci О5

| Буферное запоминающее устройство | 1979 |

|

SU822293A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1176382A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-05-23—Публикация

1986-01-20—Подача