г (Л

Изобретение относится к вычислительной технике, в частности к запоминающим У;Стройствам.

Цель изобретения - повышение надежности устройства.

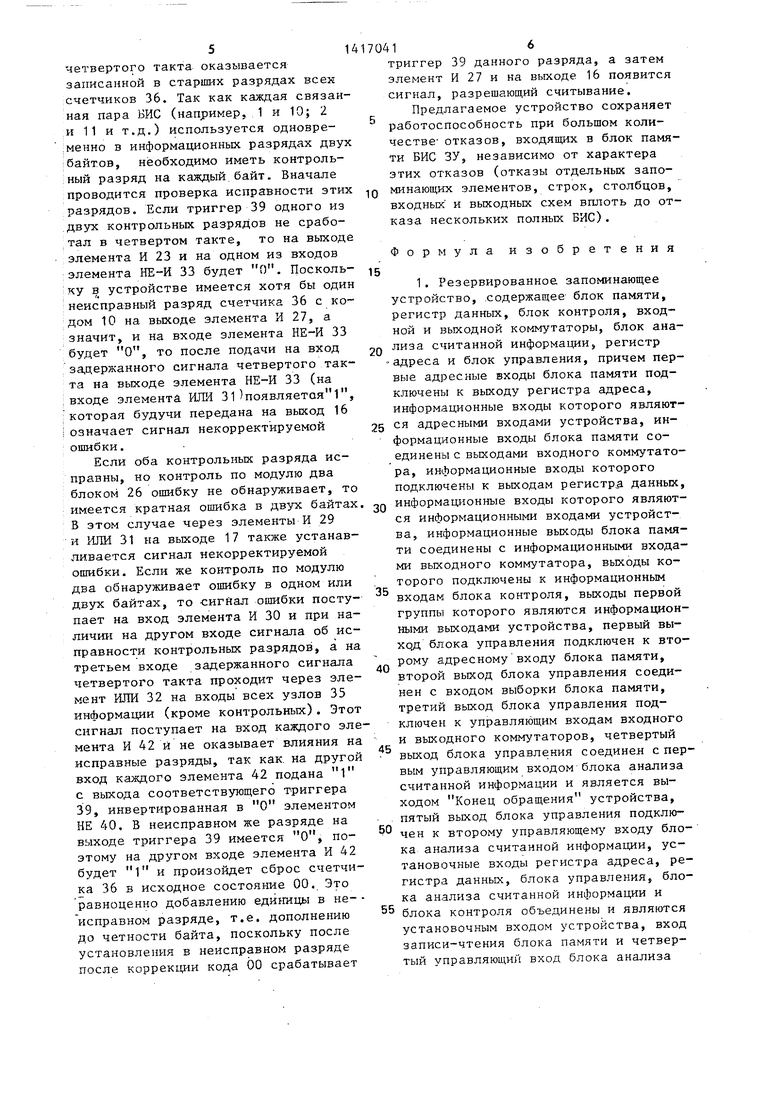

На чертеже изображена структурная схема устройства.

Устройство содержит блок 1 памяти, имеющий информационную емкость, в четыре раза превьшающую требуемую для решения задач, регистр 2 адреса, регистр 3 данных, блок 4 анализа считанной информации, блок 5 управления, входной 6 и выходной 7 коммутаторы, блок 8 контроля.

Устройство также имеет установочный вход 9, вход 10 записи-чтении, вход 11 обращения, адресные 12 и информационные 13 входы, информационные выходы 14, выход 15 Конец обращения, выход 16 Достоверная информация, выход 17 Неисправная ошибка.

Входной- 6 и выходной 7 коммутаторы полностью идентичны и содержат каждый n+k блоков 18 коммутации данных (п - разрядность данных, k количество байтов данных) и шину 19 данных.

Блок 5 содержит элемент 20 задержки, дешифратор 21, двухразрядный счетчик 22, первый 23, второй 24 и третий 25 элементы ИЛИ.

Блок 4 содержит блок 26 контроля на четность, первый 27, второй 28, третий 29 и четвертый 30 элементы И, первый 31 и второй 32 элементы ИЛИ, элемент НЕ-И 33, элемент НЕ 34. 1 Блок В контроля содержит n+k полностью идентичных узлов 35 -35р конт- роля, при этом узлы 35д и 35 л т I

контрольные, остальные - информацнон ные, счетчик 36, блок 37 сравнения, элемент ИЛИ 38, триггер 39, элемент НЕ 40, первый 41, второй 42 и третий 43 элементы И. Каждый из блоков 18 коммутации содержит первый 44 и второй 45 элементы И-НЕ, первый 46 и второй 47 элементы И, элемент ИЛИ 48.

Устройство работает следующим образом.

При каждом обращении к устройству сигналом начальной установки с входа 9 происходит установка в исходное состояние регистров 2 и 3, счетчика 22, триггеров 39, счетчиков 36 (чере элементы ИЛИ 32 и И 42, после чего проглсходит запись в ре йистры 2 и 3

5

0

5

соответственно кодов адреса и входных данных ( входов 12 и 13. После установления на входах каждой ВИС ЗУ (не показаны) блока 1 кода адреса с выходов регистра 2 и счетчика 22, а также признака записи или считывания с входа 10 арифметическое устройство (не показано) вырабатывает упд равляющий сигнал, который с входа 11 через элемент ИЛИ 24 поступает на вход выбора кристалла каждой БИС ЗУ блока 1. При этом производится запись информации в соответствующий адрес первой четверти блока 1 или считывание информации из соответствующего адреса. По истечении времени цикла обращения к блоку 1 происходит обращение к одноименному адресу второй четверти блока 1, так как задержанный на элементе 20 задержки управляющий сигнал через элемент ИЖ 23 переключает счетчик 22 в следующее состояние, после чего через.элемент ИЛИ 24 поступает на входы выбора кристалла всех БИС ЗУ блока 1. Аналогичным образом задержанный на элементе 20 задержки сигнал обеспечивает обращение к третьей и четвертой четвертям блока 1. Б зависимости от кода на выходах счетчика 22 в каждом из четырех тактов работы устройства оказывается выбранным один из выходов дешифратора 21, который управляет работой входного 6 и выходного 7 коммутаторов таким образом, что в режиме записи в первом и третьем тактах на входы блока 1 через элементы И 46 и 47 и эле мент ИЛИ 48 подается с шины 19 данных прямой код, во втором и четвертом тактах через элементы И 44 и 45 и элемент ИЛИ 48 - обратный код. Аналогично при считывании на входы блока 8 подается с блока 1 через выходной коммутатор 7 прямой код в нечетных тактах, обратный - в четньк. Кроме того, коммутаторы 6 и 7 осуществляют подключение разрядов данных к входам блока 1 и к входам блока 8, таким образом, чтобы в каждом однораз0 рядном БИС хранилась информация двух информационных разрядов.

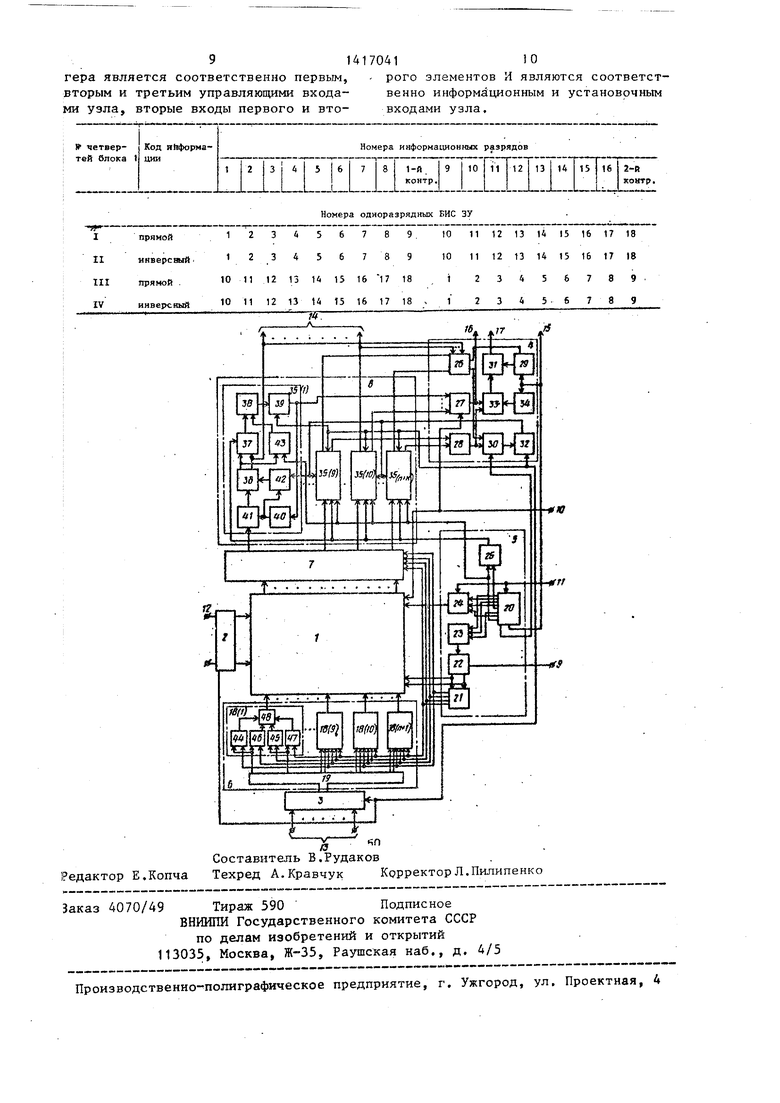

Б таблице приведен пример размещения информации в блоке 1, обеспечиваемый коммутаторами 6 и 7.

5 В зависимости от специфики использования блока 1 может быть осуществлен любой другой порядок размещения в нем информации за счет подключения

0

5

0

5

314

к входам блоков 18 коммутации данных тех или иных сочетаний разрядов шины данных (но одинаково для коммутаторов 6 и 7).

За счет размещения информа иии каждого разряда в разных частях пары ВИС и записи ее в прямом коде в двух четвертях одной и той же БИС и в инверсном коде в других четвертях той же БИС обеспечивается возможность полного контроля правильности считываемой инфЪрмащш и ее коррекции, в том числе с использованием контрольных разрядов с записанной в них сверткой по модулю два для каждого байта.

Рассмотрим далее процедуру контроля и коррекции ошибок.

1, Все БИС, входящие в блок 1, исправны. В каждом такте информация с выхода блока 1 через выходной коммутатор 7 поступает на вход каждого из узлов 35. В каждом узле 35 через элемент И 41 информация в виде О или 1 поступает на вход двух- разрядногр счетчика 36. За счет управляющего входа блок 37 сравнения производит операцию сравнения только в III и IV тактах с соответствующей задержкой на время выборки информации. Если все БИС исправны, то на выходе счетчика 36 установится после III такта код 00 или 11. Сигнал с выхода блока 37 через элемент ИЛИ 38 вызывает срабатывание триггера 39. ; При этом через элемент НЕ 40 на вход элементов И 41 поступает сигнал, запрещающий подачу из блока 1 на вход счетчика 36 информации в следующем такте. Информация на выходах старших разрядов счетчика 36 всех соответствует истинной. Поскольку сработали триггеры 39 всех разрядов, на выходе элемента И 27 устанавливается сигнал разрешения считывания. После завершения IV такта на выходе 15 устанавливается сигнал Конец обращения.

, В блоке 1 имеются отказавшие БИС с любым видом отказа вплоть до полной неработоспособности целой БИС. Количество отказавптх полностью БИС может достигать половины всех БИС блока 1.

Принцип работы каждого узла 35 остается тем же, что и описанный в предыдущем пункте. Различие заключается в том, что к концу третьего

7041

такта в узлах 35, соответствующих дефектным БИС, на выходах счетчиков 36 устанавливаются коды 10 или 01. При -ЭТОМ не происходит сравнения старшего и младшего разрядов счетчика 36 в блоке 37, не срабатывает хотя бы один из триггеров 39 на выходе 16 не вырабатывается сигнал Достоверная ин10 Форма1лия о В четвертом такте счетчики 36, соответствующие исправным разрядам, не изменяют своего состояния, как это показано вьше, а в неисправных узлах 35 в счетчике 36 запи15 сывается в зависимости от характера дефектов код 11, 01 или 10. По коду 11 происходит сравнение и работа разряда в четвертом такте аналогично описанной в п, 1, для третьего такта. При

20 коде 01 в четвертом такте истинной информацией в данном разряде является О, т.е. на соответствующем выходе 14 устанавливается истинная информация. Для обеспечения выдачи сиг25 нала на выход 16 производится переключение триггера 39 данного разряда по цепи: элемент И 43, управляемый младшим разрядом счетчика 36 и сигналом четвертого такта, задержанным на

30 время выборки с необходимой задержкой, элемент ИЛИ 38. Таким образом, если ни в одном из узлов 35 не возникает на выходе счетчиков 36 код 10, в четвертом такте на выходе 16 появляется соответствующий сигнал, а на выходах 14 - информация, истинность которой подтверждена по мажоритарному принципу Истинность информации в разрядах контроля по модулю два в данном случае не учитывается.

35

40

5

0

5

После четвертого такта на выходах счетчика 36 хотя бы одного из узлов 35 может возникнуть код 10. Причиной появления такого кода является полный отказ пары БИС одного разряда в байте. Поскольку в первую четверть одной ВИС записан прямой код, во вторую - обратный, 3 третью четверть другой БИС данного разряда записан также прямой, а в четвертую - обратный код, то практически при любом виде отказа БИС вплоть до полного из четырех четвертей этой пары БИС считается в худшем случае две 1 и два О, что и определяет на выходе счетчика код 10. Для коррекции такого рода дефектов используется метод контроля по модулю два считанной информации, которая после

51

четвертого такта оказывается записанной в старших разрядах всех счетчиков 36. Так как каждая связанная пара БИС (например, 1 и 10; 2 и 11 и т.д.) используется одновре- :менно в информационных разрядах двух байтов, необходимо иметь контрольный разряд на каждый байт. Вначале проводится проверка исправности этих разрядов. Если триггер 39 одного из двух контрольных разрядов не сработал в четвертом такте, то на выходе элемента И 23 и на одном из входов элемента НЕ-И 33 будет О. Поскольку в устройстве имеется хотя бы один неисправный разряд счетчика 36 с кодом 10 на вькоде элемента И 27, а значит, и на входе элемента НЕ-И 33 будет О, то после подачи на вход за,держанного сигнала четвертого такта на выходе элемента НЕ-И 33 (на

входе элемента ИЛИ 31)появляетая 1, которая будучи передана на выход 16

I означает сигнал некорректируемой ошибки.

Если оба контрольных разряда исправны, но контроль по модулю два блоком 26 ошибку не обнаруживает, то имеется кратная ошибка в двух байтах В этом случае через элементы И 29 и ИЛИ 31 на выходе 17 также устанав- v ивaeтcя сигнал некорректируемой ошибки. Если же контроль по модулю два обнаруживает ошибку в одном или двух байтах, то сигйал ошибки поступает на вход элемента И 30 и при наличии на другом входе сигнала об исправности контрольных разрядов, а на третьем входе задержанного сигнала четвертого такта проходит через элемент ИЛИ 32 на входы всех узлов 35 информации (кроме контрольных). Этот сигнал поступает на вход каждого элемента И 42 и не оказывает влияния на исправные разряды, так как. на другой вход каждого элемента 42 подана 1 с выхода соответствующего триггера 39, инвертированная в О элементом НЕ 40. В неисправном же разряде на выходе триггера 39 имеется О, поэтому на другом входе элемента И 42 будет 1 и произойдет сброс счетчика 36 в исходное состояние 00. Это равноценно добавлению в не- исправном разряде, т.е. дополнению до четности байта, поскольку после установления в неисправном разряде после коррекции кода 00 срабатывает

170416

триггер 39 данного разряда, а затем элемент И 27 и на выходе 16 появится сигнал, разрешающий считывание.

Предлагаемое устройство сохраняет работоспособность при большом количестве- отказов, входящих в блок памяти БИС ЗУ, независимо от характера этих отказов (отказы отдельных запо1Q минающих элементов, строк, столбцов, входных и выходных схем вплоть до отказа нескольких полных БИС).

5

0

5

0

5

0

5

0

5

Формула изобретения

1. Резервированное запоминающее устройство, .содержащее блок памяти, регистр данных, блок контроля, входной и выходной коммутаторы, блок анализа считанной информации, регистр адреса и блок управления, причем первые адресные входы блока памяти подключены к выходу регистра адреса, информационные входы которого являются адресными входами устройства, информационные входы блока памяти соединены с выходами входного коммутатора, информационные входы которого подключены к выходам регистра данных, информационные входы которого являются информационными входами устройства, информационные выходы блока памяти соединены с информационными входами выходного коммутатора, выходы которого подключены к информационным входам блока контроля, выходы первой группы которого являются информационными выходами устройства, первый выход блока управления подключен к второму адресному входу блока памяти, второй выход блока управления соединен с входом выборки блока памяти, третий выход блока управления подключен к управляющим входам входного и выходного коммутаторов, четвертый выход блока управления соединен с первым управляющим входом блока анализа считанной информации и является выходом Конец обращения устройства, пятый выход блока управления подключен к второму управляющем входу бло- ка анализа считанной информации, установочные входы регистра адреса, регистра данных, блока управления, блока анализа считанной информации и блока контроля объединены и являются установочным входам устройства, вход записи-чтения блока памяти и четвертый управляющий вход блока анализа

714

считанной информа1№1и объединены и являются входом записи-чтения устройства, вход запуска блока управления является входом обращения устройства, выходы второй группы блока контроля подключены к входам первой группы блока анализа считанной информации, первый выход блока анализа считанной информации является выходом Достоверная информация устройства, отличающееся тем, что, с целью повышения надежности устройства, в нем первый, второй и третий управляющие входы блока контроля подключены соответственно к шестому и седьмому выходам блока управления и- второму выходу блока анализа считанной инфомации, третий выход которого является выходом Неисправимая ошибка устройства, информационные и контрольные входы блока анализа считанной информации подключены соответственно к информационным выходам устройства и к выходам третьей группы блока контроля, выходы четвертой группы которого подключены к управля- ницим входам второй группы блока анализа считанной информации.

2. Устройство по п. 1, отличающееся тем, что блок анализа считанной информации содержит.с первого по четвертый элементы И, первый и второй элементы ИЛИ, элемент НЕ-И, элемент НЕ, блок контроля на четность, первый выход которого подключен к первому входу третьего элемента И, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого подключен к выходу элемента НЕ-И, входы элемента НЕ-И соединены соответственно с выходами элемента НЕ, первого элемента И, с выходом второго элемента И И первым входом четвертого элемента И, второй вход которого подключен к второму выходу элемента контроля на.четность, выход четвертого элемента И подключен к первому входу второго элемента ИЛИ, причем входы первой и второй групп блока контроля на четность являются соответственно информационными и контрольными входами блока, второй вход третьего элемента И и вход элемента НЕ соединены и являются первым управляющим входом блока, вторым, третьим и четвертым управляющими входами которого являются соответственно третий вход

7041,8

четвертого элемента И, второй вход второго элемента ИЛИ и один из входов первого элемента И, другие входы которого являются управляющими входами первой группы блока, вькод первого элемента И, выход второго элемента ИЛИ и выход первого элемента ИЛИ являются соответственно первым, втоQ рым и третьим выходами блока, входы второго элемента И являются управляющими входами второй группы блока.

3,Устройство по п. 1, о т л и- чающееся тем, что блок контg роля содержит п информационных и k .контрольных узлов контроля (где п разрядность данных, k - число байтов в слове данных), причем информационные входы узлов контроля являются

Q информационными входами блока, первые, вторые и третьи управляющие входы узлов контроля соответственно объедине- ны и являются первым, вторым и третьим управляющими входами блока конт5 роля, установочные входы узлов контроля объединены и являются установочным входом блока, информационные и контрольные выходы информационных узлов контроля являются соответственно

0 выходами первой и второй групп блока, информационные и контрольные выходы контрольных узлов контроля являются соответственно выходами третьей и четвертой групп блока.

4.Устройство по п. 3, отличающееся тем, что каждый узел контроля содержит первый, второй и третий элементы И, счетчик, блок сравнения, элемент ИЛИ, эле.Q мент НЕ, вькод которого соединен с первыми входами первогд и второго элементов И, выходы которых подключе-, ны соответственно к счетному и установочному входам счетчика, выходы разрядов счетчика соединены с информационными входами блока сравнения, выходы третьего элемента И и блока сравнения подключены к входам элемента ИЛИ, выход которого подключен к информационному-входу триггера, выход младшего разряда счетчика подключен к первому входу третьего элемента И, выход триггера соединен с входом элемента НЕ и является контрольным выходом узла, информационным выходом которого является выход старшего разряда счетчика, второй вход третьего элемента , управляющий вход блока сравнения и установочный вход триг5

5

0

55

9141704110

гера является соответственно первым, - рого элементов И являются соответст- вторым и третьим управляющими входа- венно информационным и установочным ми узла, вторые входы первого и вто- входами узла.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1249592A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1741137A1 |

| Резервированное запоминающее устройство | 1985 |

|

SU1278984A1 |

| Устройство для контроля монтажа | 1986 |

|

SU1312616A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Процессор с микропрограммным управлением | 1975 |

|

SU525956A1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам. Цель изобретения - повышение надежности устройства. Устройство содержит блок памяти, регистр адреса, регистр данных, блок анализа считанной информации, блок управления, входной и выходной коммутаторы и блок контроля. В устройстве используется четырехкратное резервирование. 3 з.п. ф-лы, t ил.,. 1 табл.

Iпрямой

IIинверсвый.

IIIпрямой .

IVинверсный

1234567891011 12 13 14 15 16 17 18

10 11 12 13 14 15 16 17 18i23456789

10 11 12 13 14 15 16 17 18 ,l 23456789

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1188784A1 |

| Солесос | 1922 |

|

SU29A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-08-15—Публикация

1986-08-08—Подача