Изобретение относится к запоминающим устройствам.

Целью изобретения является повышение надежности запоминающего устройства за счет совершенствования свойств самоконтроля и самовосстановления при использовании современных БИС ЗУ, обеспечивающих, например, четырехкратную избыточность информационной емкости по сравнению с необходимой.

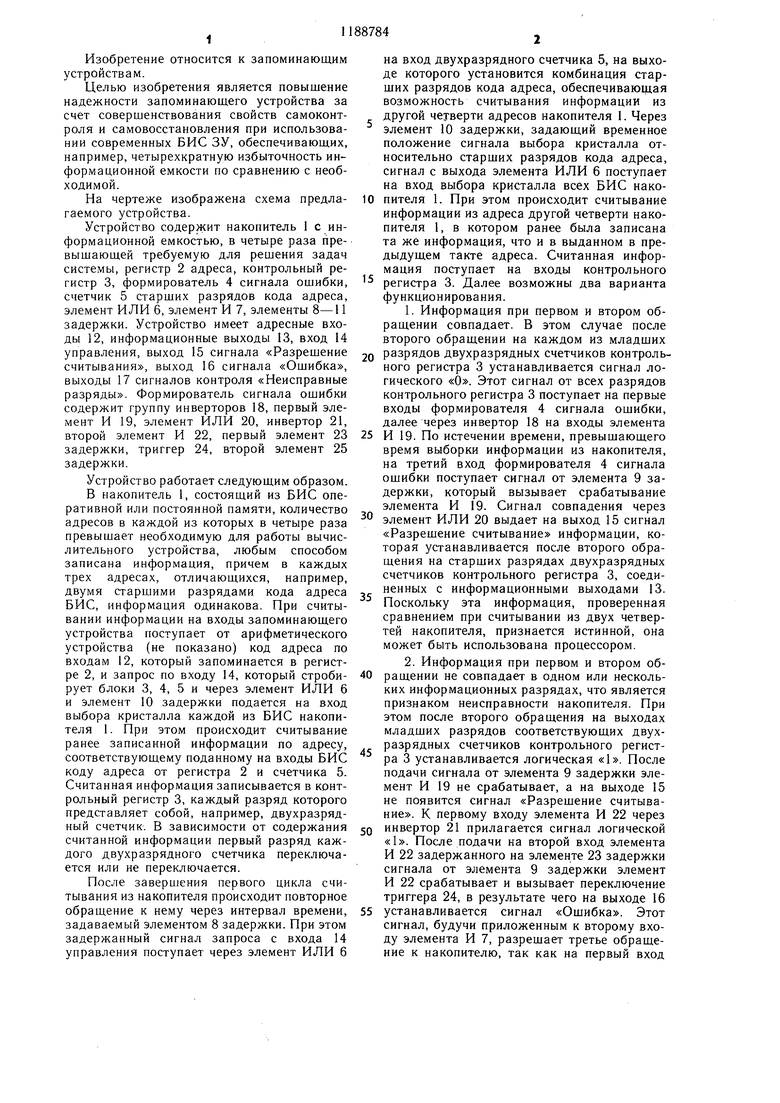

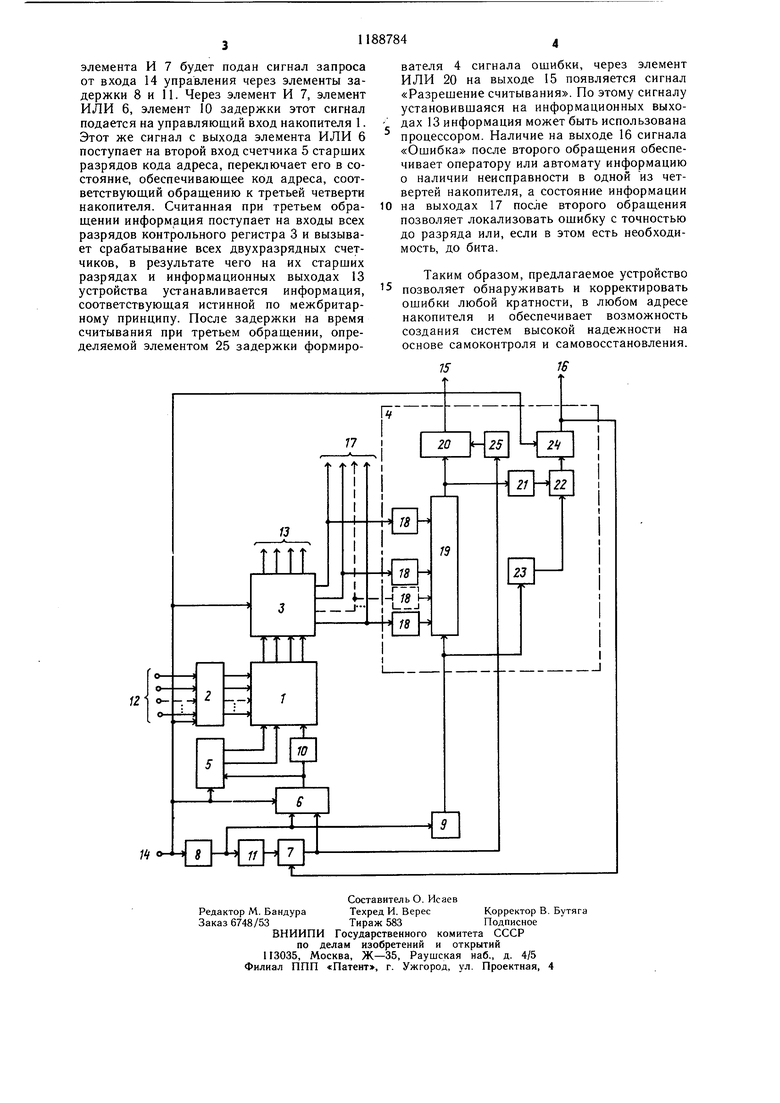

На чертеже изображена схема предлагаемого устройства.

Устройство содержит накопитель 1 с информационной емкостью, в четыре раза превышающей требуемую для решения задач системы, регистр 2 адреса, контрольный регистр 3, формирователь 4 сигнала ошибки, счетчик 5 старших разрядов кода адреса, элемент ИЛИ 6, элемент И 7, элементы 8-11 задержки. Устройство имеет адресные входы 12, информационные выходы 13, вход 14 управления, выход 15 сигнала «Разрешение считывания, выход 16 сигнала «Ошибка, выходы 17 сигналов контроля «Неисправные разряды. Формирователь сигнала ошибки содержит группу инверторов 18, первый элемент И 19, элемент ИЛИ 20, инвертор 21, второй элемент И 22, первый элемент 23 задержки, триггер 24, второй элемент 25 задержки.

Устройство работает следующим образом.

В накопитель 1, состоящий из БИС оперативной или постоянной памяти, количество адресов в каждой из которых в четыре раза превышает необходимую для работы вычислительного устройства, любым способом записана информация, причем в каждых трех адресах, отличающихся, например, двумя старшими разрядами кода адреса БИС, информация одинакова. При считывании информации на входы запоминающего устройства поступает от арифметического устройства (не показано) код адреса по входам 12, который запоминается в регистре 2, и запрос по входу 14, который стробирует блоки 3, 4, 5 и через элемент ИЛИ 6 и элемент 10 задержки подается на вход выбора кристалла каждой из БИС накопителя 1. При этом происходит считывание ранее записанной информации по адресу, соответствующему поданному на входы БИС коду адреса от регистра 2 и счетчика 5. Считанная информация записывается в контрольный регистр 3, каждый разряд которого представляет собой, например, двухразрядный счетчик. В зависимости от содержания считанной информации первый разряд каждого двухразрядного счетчика переключается или не переключается.

После завершения первого цикла считывания из накопителя происходит повторное обращение к нему через интервал времени, задаваемый элементом 8 задержки. При этом задержанный сигнал запроса с входа 14 управления поступает через элемент ИЛИ 6

на вход двухразрядного счетчика 5, на выходе которого установится комбинация старших разрядов кода адреса, обеспечивающая возможность считывания информации из другой четверти адресов накопителя 1. Через элемент 10 задержки, задающий временное положение сигнала выбора кристалла относительно старших разрядов кода адреса, сигнал с выхода элемента ИЛИ 6 поступает на вход выбора кристалла всех БИС накопителя 1. При этом происходит считывание информации из адреса другой четверти накопителя 1, в котором ранее была записана та же информация, что и в выданном в предыдущем такте адреса. Считанная информация поступает на входы контрольного

регистра 3. Далее возможны два варианта функционирования.

1.Информация при первом и втором обращении совпадает. В этом случае после второго обращении на каждом из младщих

Q разрядов двухразрядных счетчиков контрольного регистра 3 устанавливается сигнал логического «О. Этот сигнал от всех разрядов контрольного регистра 3 поступает на первые входы формирователя 4 сигнала ошибки, далее через инвертор 18 на входы элемента

5 И 19. По истечении времени, превышающего время выборки информации из накопителя, на третий вход формирователя 4 сигнала ошибки поступает сигнал от элемента 9 задержки, который вызывает срабатывание элемента И 19. Сигнал совпадения через

элемент ИЛИ 20 выдает на выход 15 сигнал «Разрешение считывание информации, которая устанавливается после второго обращения на старших разрядах двухразрядных счетчиков контрольного регистра 3, соединенных с информационными выходами 13. Поскольку эта информация, проверенная сравнением при считывании из двух четвертей накопителя, признается истинной, она может быть использована процессором.

2.Информация при первом и втором обращении не совпадает в одном или нескольких информационных разрядах, что является признаком неисправности накопителя. При этом после второго обращения на выходах младщих разрядов соответствующих двухразрядных счетчиков контрольного регистра 3 устанавливается логическая «1. После подачи сигнала от элемента 9 задержки элемент И 19 не срабатывает, а на выходе 15 не появится сигнал «Разрешение считывание. К первому входу элемента И 22 через

0 инвертор 21 прилагается сигнал логической «1. После подачи на второй вход элемента И 22 задержанного на элементе 23 задержки сигнала от элемента 9 задержки элемент И 22 срабатывает и вызывает переключение триггера 24, в результате чего на выходе 16

5 устанавливается сигнал «Ошибка. Этот сигнал, будучи приложенным к второму входу элемента И 7, разрешает третье обращение к накопителю, так как на первый вход

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2024969C1 |

| Запоминающее устройство с резервированием | 1987 |

|

SU1437917A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1249592A1 |

| Резервированное запоминающее устройство | 1986 |

|

SU1417041A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU951406A1 |

| Резервированное запоминающее устройство | 1985 |

|

SU1278984A1 |

| Резервированное запоминающее устройство | 1987 |

|

SU1513526A1 |

| Резервированное оперативное запоминающее устройство | 1982 |

|

SU1137538A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU879655A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

1. ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ, содержащее регистр адреса, информационные входы которого являются адресными входами устройства,а выходы подключены к адресным входам первой группы накопителя, выходы которого соединены с информационными входами контрольного регистра, выходы первой группы которого являются информационными выходами устройства, а выходы второй группы подключены к входам группы формирователя сигнала ошибки и являются контрольными выходами устройства, управляющие входы регистра адреса, контрольного регистра, первый вход формирователя сигнала ошибки, первый вход элемента ИЛИ и вход первого элемента задержки объединены и являются управляющим входо.м устройства, выход элемента задержки-подключен к второму входу элемента ИЛИ и входу второго элемента задержки, выход которого соединен с вторым входом формирователя сигнала ошибки, отличающееся тем, что, с целью повышения надежности устройства в него введены счетчик старших разрядов кода адреса, элемент И, третий и четвертый элементы задержки, причем выходы счетчика старших разрядов кода адреса подключены к адресным входам второй группы накопителя, а входы синхронизации и начальной установки соединены соответственно с выходом элемента ИЛИ и управляющим входом устройства, вход третьего элемента задержки подключен к выходу элемента ИЛИ, а выход соединен с управляющим входом накопителя, вход четвертого элемента задержки подключен к выходу первого элемента задержки, а выход соединен с первым входом элемента И, второй вход которого подключен к первому выходу формирователя сигнала ошибки, третий вход которого подключен к выходу элемента И и к третьему входу элемента ИЛИ, а первый и второй выходы соединены с управляющим выходом устройства. 2. Устройство по п. 1, отличающееся тем, что формирователь сигнала ошибки содержит группу инверторов, элемент ИЛИ, перi вый и второй элементы И,, первый и второй элементы задержки, инвертор и триггер, (Л причем входы инверторов группы являются входами группы формирователя сигнала ошибки, первый, второй и третий входы которого соединены соответственно с первым входом триггера, с одним входом первого элемента И и входом первого элемента задержки, а первый и второй выходы формирователя сигнала ошибки подключены соответственно к выходу триггера и выходу элеас мента ИЛИ, вход которого соединен с вхо00 дом инвертора и выходом первого элемента И, другие входы которого подк тючены к выходам инверторов группы, выход первого 00 элемента задержки соединен с вторым вхоNj дом элемента ИЛИ, выход второго элемента И подключен к второму входу триггера, первый вход - к выходу инвертора, а второй вход - к выходу второго элемента задержки, вход которого соединен с вторым входом формирователя сигнала ошибки.

| Электроника, 1978, № 19, с | |||

| Прялка для изготовления крученой нити | 1920 |

|

SU112A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU951406A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-10-30—Публикация

1983-12-22—Подача