00

Изобретение относится к радиотех нике и может быть использовано в приемопередающей и измерительной ап паратуре,

Целью изобретения является упро щение устройства.

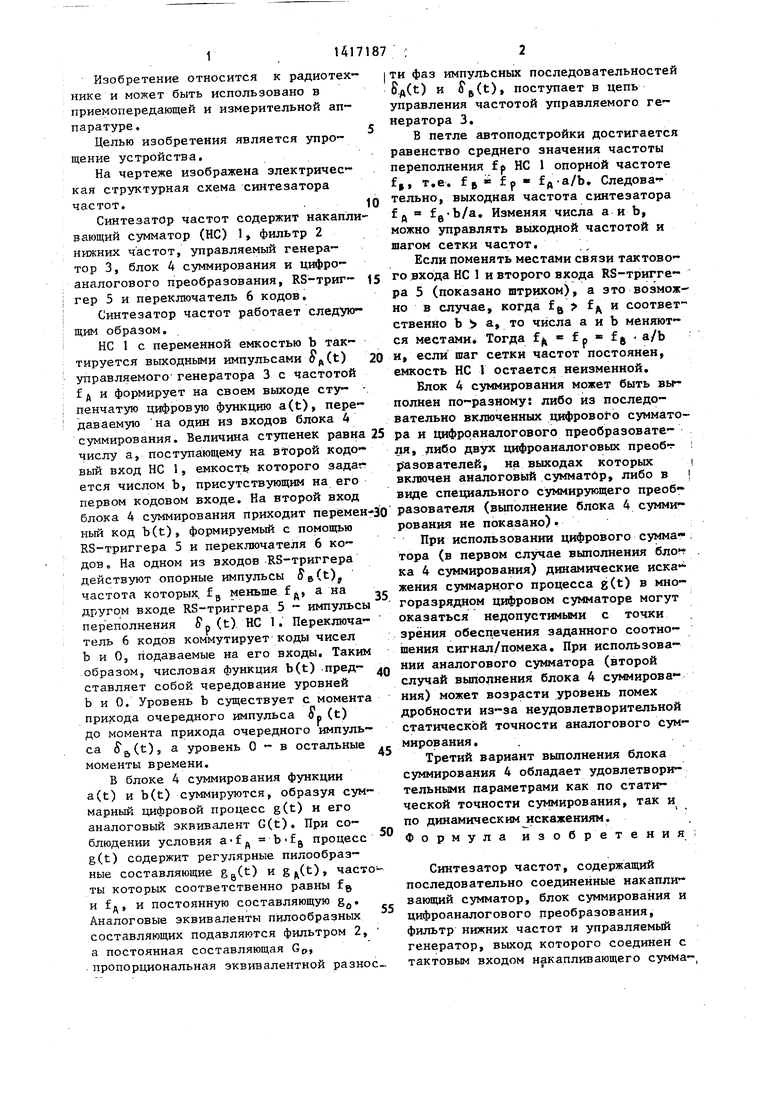

На чертеже изображена электрическая структурная схема синтезатора частот..

Синтезатор частот содержит накапливающий сумматор (НС) 1, фильтр 2 нижних частот, управляемый генератор 3, блок 4 суммирования и цифро- аналогового преобразования, К8-триг гер 5 и переключатель 6 кодов.

Синтезатор частот работает следукт щим образом,

НС 1 с переменной емкостью b тактируется выходными импульсами 5(t) управляемого генератора 3 с частотой fд и формирует на своем выходе сту- - пенчатую цифровую функцию a(t), передаваемую на один из входов блока 4 суммирования. Величина ступенек равна числу а, поступающему на второй кодовый вход НС 1, емкости которого задаг- ется числом Ь, присутствующим на его первом кодовом входе. На второй вход блока 4 суммирования приходит перемен ный код b(t), формируемый с помощью RS-триггера 5 и переключателя 6 кодов. На одном из входов RS-триггера действуют опорные импульсы S eCt), частота которых, f меньше f д а на другом входе RS-триггера 5 - импульсы переполнения (t) НС 1, Переключатель 6 кодов коммутирует коды чисел b и О, подаваемые на его входы. Таким образом, числовая функция b(t) пред- ставляет собой чередование уровней Ь и 0. Уровень b существует с момента прихода очередного импульса Ор(t) до момента прихода очередного импульса 5 g(t)5 а уровень О-в остальные моменты времени.

В блоке 4 суммирования функции a(t) и b(t) суммируются, образуя суммарный цифровой процесс g(t) и его аналоговьй4 эквивалент G(t). При соблюдении условия a-f b fg процесс g(t) содержит регулярные пилообразные составляющие gg(t) и gj(t), часто ты которых соответственно равны fg и д, и постоянную составляющую g. Аналоговые эквиваленты пилообразных составляющих подавляются фильтром 2, а постоянная составляющая Gj, пропорциональная эквивалентной разнос

5 0 g Q

5

0

ти фаз импульсных последовательностей O.(t) и S g(t), поступает в цепь управления частотой управляемого генератора 3,

В петле автоподстройки достигается равенство среднего значения частоты переполнения fр НС 1 опорной частоте fj, т.е, f 6 f р - fft-a/b, Следова- тельно, выходная частота синтезатора fд в fg-b/a. Изменяя числа а и Ь, можно управлять выходной частотой и шагом сетки частот.

Если поменять местами связи тактового входа НС 1 и второго входа RS-триггера 5 (показано штрихом), а это возмож- но в случав, когда fg А и соответ ственно b а, то числа а и b меняются местами Тогда д f„ « f - a/b и, если шаг сетки частот постоянен, емкость НС 1 остается неизменной.

Блок 4 суммирования может быть выполнен по-разному; либо из последовательно включенных цифрово о сумматора и цифроаналогового преобразователя, либо двух хщфроаналоговых преоб г ; { азователей, на выходах которых i включен аналоговый сумматор, либо в | виде специального суммирующего преобразователя (вьтолнение блока 4 суммирования не показано)

При использовании цифрового сумма тора (в первом случае выполнения бло ка 4 суммирования) динамические иска жения суммарного процесса g(t) в многоразрядном цифровом сумматоре могут оказаться недопустимыми с точки зрения обеспечения заданного соотношения сигнал/помеха. При использовании аналогового сумматора (второй случай выполнения блока 4 суммирования) может возрасти уровень помех дробности из-за неудовлетворительной статической точности аналогового суммирования.

Третий вариант выполнения блока суммирования 4 обладает удовлетворительными параметрами как по статической точности cy Iмиpoвaния, так и по динамическим искажениям. Формула изобретения;

Синтезатор частот, содержащий последовательно соединенные накапливающий сумматор, блок суммирования и цифроаналогового преобразования, фильтр нижних частот и управляемый генератор, выход которого соединен с тактовым входом накапливающего сумма-,

31А17187

тора, выход переполнения котороговходом блока е ммирования и цифроана

подключен к первому входу К8-тригге логового преобразования включен перера, при этом первый и второй кодовыеключатель кодов, первый и второй

входы накапливающего сумматора явля кодовые входы которого подключены со

ются соответственно первьм и вторымответственно к первому кодовому входу

кодовыми входами синтезатора частот,синтезатора частот и к шине логическое

отличающийся тем, что,го нуля, а второй вход RS-триггера

с целью упрощения синтезатора частот,является тактовым входом синтезатора

меяаду выходом RS-триггера и вторым Qчастот.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1985 |

|

SU1254576A1 |

| Синтезатор частот | 1985 |

|

SU1392613A1 |

| Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах | 1988 |

|

SU1757080A1 |

| Квазисинхронный детектор | 1985 |

|

SU1352637A1 |

| Синтезатор частот | 1988 |

|

SU1566455A1 |

| Синтезатор частот | 1985 |

|

SU1262685A1 |

| Устройство фазовой подстройки частоты | 1982 |

|

SU1251322A1 |

| Цифровой фазовый детектор для синтезаторов частот | 1988 |

|

SU1539677A1 |

| Синтезатор частот | 1988 |

|

SU1552344A1 |

| Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах | 1981 |

|

SU1109872A1 |

Изобретение относится к радиотехнике. Цель изобретения - упрощение устр-ва. Синтезатор частот содержит накапливающий сумматор (НС) 1, фильтр 2 нижних частот, управляемый г-р 3, блок суммирования и цифроаналогового .преобразования (БСЦП) 4, RS-триггер 5 и переключатель 6 кодов. На входы БСЦП 4 поступают одновременно ступенчатая цифровая ф-ция a(t), формируемая с помощью НС 1, и переменная ф-ция b(t), формируемая с помощью RS-триггера 5 и переключателя 6. В БСЦП 4 эти ф-цин суммируются, образуя суммарный цифровой процесс и его аналоговый эквивалент G(t). Аналоговые эквиваленты пилообразных составляющих подавляются фильтром 2, а постоянная составляюп;ая G, поступает в цепь управления частотой г-ра З..В синтезаторе частот осзтдествляется управление выходной частотой и шагом сетки частот. БСПП 4 может быть выполнен в трех вариантах: либо из последовательно включенных цифрового сумматора и ЦАП, либо из двух ЦАП, на выходах которых включен аналоговьш сумматор, либо в виде специального суммирующего ЦАП. 1 ил (Л

| Синтезатор частот | 1982 |

|

SU1117839A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Козлов В.К, Способ цифрового фазового детектирования.- Радиотехника, 1980, № 4, 0.25-29. | |||

Авторы

Даты

1988-08-15—Публикация

1986-09-29—Подача