00

0д ел

аи

20

25

30

Изобретение относится к автоматике и может быть использовано в сис- темах управления с шаговым двигате- лем.г

Цель изобретения - сокращение объема программирования и распирение области применения.

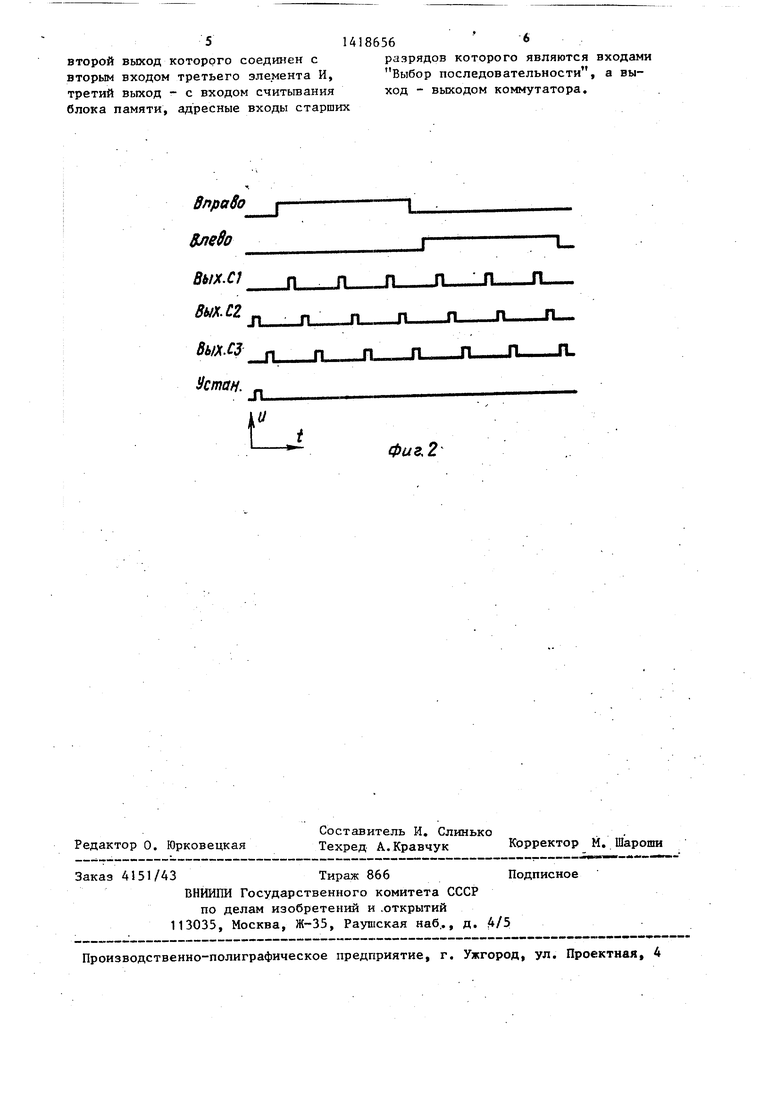

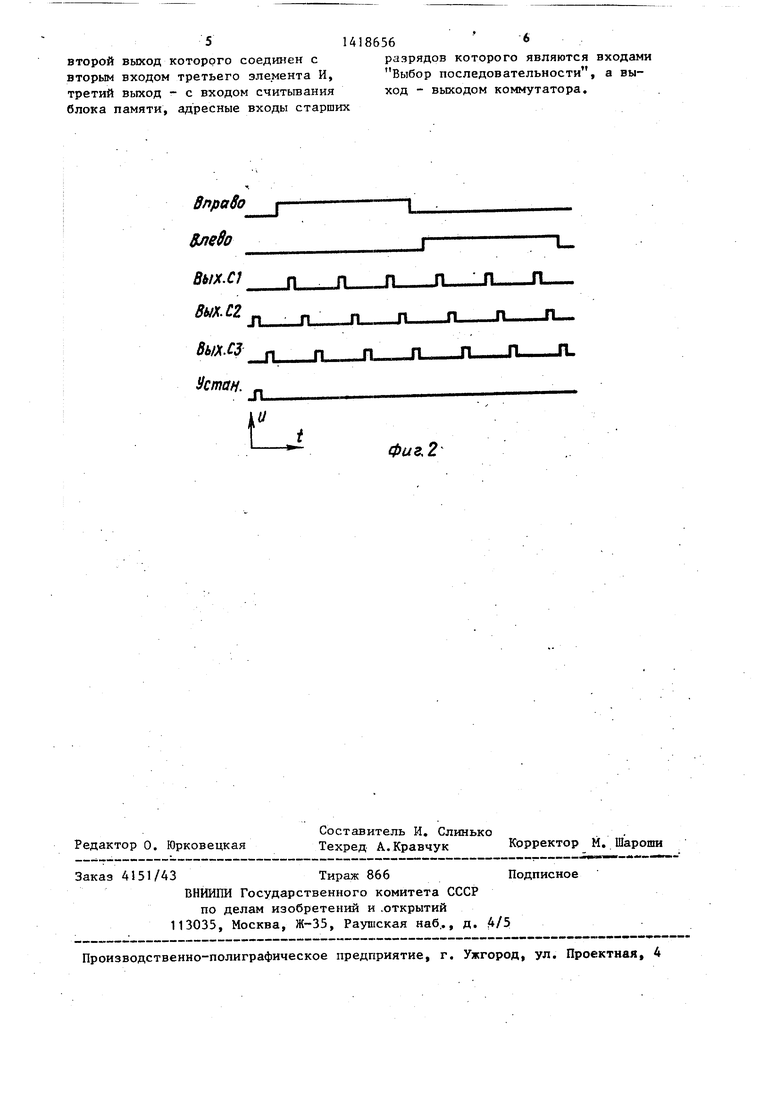

На фиг, 1 изображена структурная схема коммутатора; на фиг, 2 - при- 10 мер временного расположения управляющих сигналов;

Коммутатор содержит генератор 1 импульсов, предназначенный для получения трех импульсных последователь- 5 ностей, сдвинутых по фазе, блок 2 памяти для записи и хранения последовательностей состояний переключения фйз различных шаговых двигателей и формирователь 3 циклов коммутации,.

Формирователь 3 циклов коммутации содержит первый 4, второй 5 и третий 6 элементы И, первый 7 и второй 8 элементы ИЖ, двоичный счетчик 9 импульсов для формирования циклов и адресов выборки состояний, первьй JO и второй I1 элементы задержки и элемент 12 сравнения для формирования сигнала окончания цикла при прямой последовательности коммутации.

Коммутатор работает следующим образом.

Входы А2 блока 2 памяти с помощью входов коммутатора Выбор последова- 5 тельности устанавливает р состояние, соответствующее адресу необходимой последовательности состояний переключения фазо Информационные входы D счетчика 9 импульсов и вторую груп-40 пу информационных входов В элемента 12.сравнения, с помощью входов Цикл коммутатора устанавливают в состояние, соответствующее числу тактов в цикле. Эти состояния с помощью внеш- 5 него источника управляющих сигналов (не показан) сохраняются в течение необходимого времени работы коммутатора.

При необходимости формирования Q циклов с первого такта подают команду Установка с помощью импульса, который, пройдя через элемент ИЛИ 8, устанавливает счетчик 9 импульсов, а следовательно, и входы А-элемента 12 сравнения и входы А1 блока 2 памяти в нулевое состояние.

Генератор 1 импульсов непрерьтно формирует три последовательности им0

5

0

0

5

5 0 5

Q

пульсов в тактах С1, С2 и СЗ. Импульсы с третьего выхода генератора в такте .СЗ, поступая на вход считьша- ния RD блока 2 памяти, считьшают состояние коммутации фаз в первом такте, которое поступает на вход Q,

При поступлении команды Вправо на первом входе элемента И 4 и на управляющем входе элемента 12 сравнения устанавливается единичный потенциал, который открьшает элемент И 4 и разрешает сравнение,

Импульсы с первого выхода генератора 1 в такте С1 проходят через элемент И 4 на вход су }мирования счетчика 9 импульсов и последовательно переводят счетчик, следовс1тельно, входы А элемента 12 срав нения и входы А1 блока 2 памяти в следующие состояния. При этом с помощью импульсов в такте СЗ с блока памяти происходит последовательное считьшание состояний переключения фаз.

С переходом счетчика ш шульсов в состояние, соответствующее состоянию входов Б элемента 12 сравнения, на выходе формируется сигнал равенства, который поступает на первый вход элемента И 6 и открывает его Импульс с второго выхода генератора 1 в такте С2 проходит через элементы И 6 и ИЛИ 8 и устанавливает счетчик 9 импульсов в нулевое состояние. Начинается формирование следующих цик- лов, которое продолжается, пока на входе Вправо присутствует единичный потенциал. При этом происходит. последовательное считьшание в прямом надравлении состояний выбранной последовательности из запоминающего устройства,

При поступлении команды Влево на первом входе элемента И 5 устанавливается единичный потенциал, который открьтает его. Импульсы с первого выхода генератора 1 в такте 01 проходят через элемент И 5, через элемент ИЛИ 7 и поступают на вход вычитания счетчика 9 импульсов и последовательно переводят счетчик, следовательно, и входы А.1 блока 2 памяти в следующие состояния. При этом с помощью импульсов в такте СЗ с блока памяти происходит последовательное считывание состояний переключения фаз в обратном направлении. Элемент 12 сравнения в это время не анализирует состояний его информационньпс входов, так как на его управляющем входе присутствует нулевой потенциал. Когда счетчик 9 импульсов, по мере поступления на его вход вычитания импульсов в такте С1 .переведен в нулевое состояние, приход следующего импульса в такте С1 вызьюает появление на его выходе В импульса той же длительности сигнала Заем, который, постздгая на вход элемента 10 задержки,- вызьшает появление импульсов на выходах элементов 10 и 11, задержанных соответственно на длительность и удвоенную длительность импульса в такте С1.

Импульс с выхода элемента 10 задержки поступает на вход записи W F счетчика 9 импульсов, в связи с чем счетчик переходит в состояние, соответствующее состоянию его информационных входов I) , Затем на вход вычитания счетч1-1ка через элемент ИЛИ 7 поступает импульс с выхода элемента И задержки, содержимое счётчика уменьшается на единицу и начинается формирование следутощих циклов которое продолжается, пока на входе Вле ,во присутствует единичный потенциал При этом происходит последовательное циклическое считьшание в обратном направлении состояний выбранной последовательности с блока памяти.

Уменьшение содержимого счетчика после установки в состояние, соответствующее состоянию его информаци онных входов, необходимо в связи с тем, что нулевое состояние счетчика является адресом выборки состояния в первом такте. Это учитывается и при выборке состояний в прямом направлении. В этом случае с установлением счетчика в состояние, соответствующее состоянию его информационных входов, он сбрасьшается с по- мопрью элемента сравнения в нулевое состояние, при- этом предыдущее состояние не используется для адресации

Предлагаемый коммутатор содержит универсальный формирователь циклов коммутации, перестраиваемый с помощью входов управления и с установ- кой в нулевое состояние в любом такте, что. позволяет сократить обьем программирования и использовать коммутатор в универсальных устройствах для контроля и испытаний шаговых двигателей, а формирователь циклов коммутации - для разработки микросхе1418656

мы универсального формирователя циклов коммутации фаз шаговых двигателей

I

Формула изобретения

0

5

0

5

0

5

0

5

0

Коммутатор для управления шаговым двигателем, содержащий генератор импульсов и блок памяти, о т л и- чающ.ийся тем, что, с целью сокращения объема программирования и расширения области применения, введен формирователь циклов коммутации, включакнций перв.ый, второй и третий элементы И, первый и второй элементы ИЛИ, двоичный счетчик импульсов, первый и второй элементы задержки, элемент сравнения, выход первого элемента И соединен с входом суммирования двоичного счетчика импульсов, выход второго элемента И соединен с первым входом первого элемента ИЛИ, выход которого соединен с входом вычитания двоичного счетчика импульсов, выход заема которого, соединен с входом первого элемента задержки, выход которого соединен с входом записи данных двоичного счетчика импульсов и с входом второго элемента задержки, выход которого соединен с вторым входом первого элемента ИЛИ, выход третьего элемента И соединен с первым входом второго элемента ИЛИ, выход которого соединен с входом установки в нулевое состояние двоичного счетчика импульсов, информационные выходы которого соединены .с первой группой информационных входов элемента сравнения и адресными входами мпадших разрядов блока памяти, выход равнозначности элемента сравнения соединен с первым входом треть его элемента И, первый вход первого элемента И соединен с входом управления Равенство элемента сравнения и является входом Вправо коммутатора, первый вход второго элемента И является входом Влево коммутатора, второй вход второго элемента ИЛИ яв- яяется входом Установка коммутатора, информационные вкоды двоичного счетчика имцудьсов соответств енно соединены с второй грутшой информационных входов элемента сравнения и являются входами Цикл коммутатора, вторые входы первого и второго эле-, ментов И объединены и соединены с первым выходом генератора импульсов.

51418656 6 ,

второй выход которого соедю ен с разрядов которого являются входами вторым входом третьего элемента И, Выбор последовательности, а вы- третий выход - с входом считьшания ход - выходом коммутатора, блока памяти, адресные входы старших

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемая линия задержки | 1986 |

|

SU1406753A1 |

| Устройство для определения свойств полноты логических функций | 1984 |

|

SU1170446A1 |

| Устройство для отображения информации | 1986 |

|

SU1446642A1 |

| Устройство для управления считыванием графической информации | 1986 |

|

SU1334170A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| Устройство для считывания графической информации | 1982 |

|

SU1037296A1 |

| Мажоритарное декодирующее устройство | 1987 |

|

SU1471313A1 |

| Устройство для ввода информации | 1988 |

|

SU1513438A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Программно-временное устройство | 1982 |

|

SU1062645A1 |

Изобретение относится к автоматике и может быть использовано в системах управления с шаговым двигателем. Целью изобретения является сок- ращение объема программирования и расширение области применения. Коммутатор содержит генератор импульсов Iдля формирования трех импульсных последовательностей, сдвинутых по фазе, блок памяти 2 для хранения различных последовательностей состояний для коммутации фаз, формирователь циклов коммутации 3 состоящий из двоичного счетчика импульсов 9 элемента сравнения 12, здементов И 4, 5, 6 и ИЛИ 7, 8 и злементов задержки 10, I1для управления формированием цик- .лов. 2 ип.

Вправо

л

8ле$о

п п п п п п

п п п п п п п п п п п п п п стан. «

tL

i

Фиг.2

| Устройство для управления шаговым двигателем | 1981 |

|

SU1004979A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Коммутатор для управления шаговым двигателем | 1984 |

|

SU1191886A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1988-08-23—Публикация

1987-01-22—Подача