(Л

I Изобретение относится к цифровой вычислительной технике и может быть использовано в процессорах ЭВМ и цифровых устройствах автоматики.

Цель изобретения - повышение быстродействия.

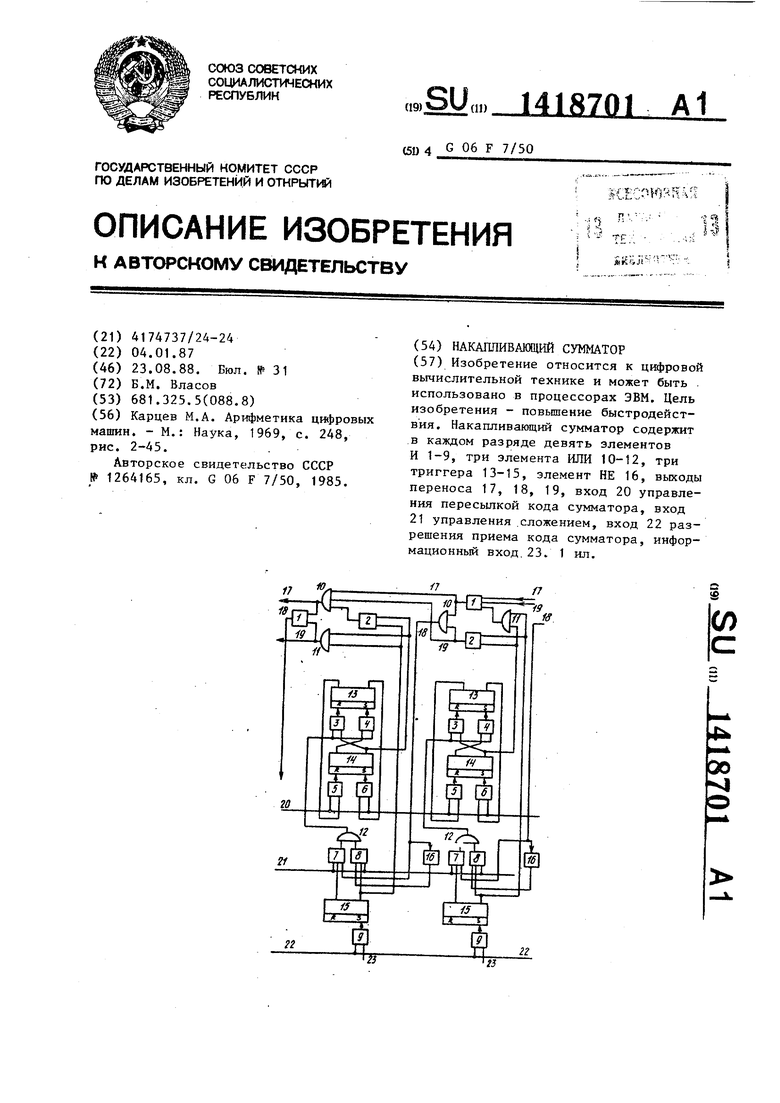

На чертеже представлена функциональная схема двух разрядов накапливающего сумматора.

Накапливающий сумматор содержит в каждом разряде девять элементов И 1-9 элемента ИЛИ 10-12, три триггера 1J3-15, элемент НЕ 16, выходы 17-19 переноса в старший разряд, вход 20 управления пересылкой кода сумматора, вход 21 управления сложением, вход 22 разрешения приема кода сумматора и| информационные входы 23.(Входы ус- т|ановки триггеров 13-15 в нулевое с эстояние не показаны) .

I Работа сумматора при выполнении операции сложения двух положительных чисел. Считают, что код первого сла- гэемого хранится в триггерах 13, а код второго слагаемого поступает в сумматор с входов 23. Триггеры 15 приемного регистра предварительно ус- т ановлены в нулевое состояние или прием информации в этот регистр осуществляется парафазным кодом.

В Лервом такте работы сумматора выполняются элементарные операции приема кода второго слагаемого в триггеры 15 и пересылки кода первого слагаемого, хранящегося в триггерах 13, в триггеры 14. Для выполнения этих двух операций на входы 20 и 22 одновременно подаются исполнительные импульсы. ЕСЛИ в триггере 13 хранится код единицы, то исполнительный импульс, поступив на вход 20, через элемент И 6 поступает на S-вход триггера 14 и устанавливает .его в единичное состояние. Если в триггере 13 хранится код нуля, то исполнительный импульс через элемент И 5 поступает на R-вход триггера 14 и устанавливает его в нулевое состояние. Если на входе 23 отсутствует потенциал, соответствующий коду единицы, то триггер 15 устанавливается в нулевое состояние.

После переключения триггеров 14 и 15 создаются условия для начала формирования и распространения в сторону старших разрядов потенциала сквозного переноса.

В четных разрядах сумматора, в которых триггеры 13-15 хранят коды еди0

5

0

5

0

5

0

5

0

5

ницы, на выходах 17-19 формируются потенциалы переноса в старший разряд сумматора. Эти потенциалы формируются с помощью элементов И 2 и 1 и ИЛИ 11. В нечетных разрядах сумматора при наличии кодов единицы в триггерах 13- 15 потенциалы переноса в старший разряд вырабатываются с помощью элементов И 1, ИЛИ 10 и И 2. Если в следующем старшем разряде в триггере 14 или 15 хранится код единицы, то сигнал переноса, поступивший с выходов 17 и 19 предыдущего разряда, через элемент ИЛИ 10 поступает в следующий старший разряд сумматора. Таким образом, сквозной перенос проходит в каждом разряде сумматора только через один логический элемент И или ИЛИ и имеет временную задержку, , т.е. задержку на одном логическом элементе. После завершения формирования максимального сквозного переноса, равного времени п с , где п - число двоичных разрядов сумматора, в третьем такте работы сумматора выполняется формирование результата сложения двух чисел за счет подачи на вход 21 исполнительного импульса. Если в рассматриваемом разряде сумматора код, хранящийся в триггере 15, и сигнал переноса, поступивший из младшего разряда с выхода 18, равны единице или нулю, т.е. одинаковы, то исполнительный импульс, поступивший на вход 21, не проходит на счетный вход триггера 13 и не меняет его состояние. Если же код триггера 15 и значение потенциала переноса, поступившего из младшего разряда, не совпадают, то исполнительный импульс по цепи элементов И 7 и 8 и ИЛИ 12 поступает на входы элементов И 3 и 4 и инвертирует состояние триггера 13.

Фор м у ла изобретения

Накапливающий сумматор, содержащий в каждом разряде три RS-триггера, три элемента ИЛИ, девять элементов И, элемент НЕ, причем первый вход первого элемента И соединен с входом управления приемом кода сумматора, второй вход первого элемента И соединен с информационным входом данного разряда сумматора, выход первого элемента,И соединен с S-входом первого триггера, единичный выход которого соединен с первым входом второго элемента И, выход второго элемента И подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, выход первого элемента ИЛИ соединен с первыми входами четвертого и пятого элементов И, вторые входы которых соединены соответственно с единичньм и нулевым выходами второго триггера, R- и S-входы которого соединены с выходами соответственно шестого и седьмого элементов И, первые входы которых соединены с входом управления пересылкой кода сумматора, а вторые входы соединены соответственно с нулевьм и единичньм выходами третьего триггера, R- и5-вхо ды которого соединены с выходами соответственно четвертого и пятого элементов И, первый вход третьего элемента И соединен с нулевым выходом первого триггера, второй вход третьего элемента И соединен с входом переноса из младшего разряда сумматора, второй вход второго элемента И соединен с выходом элемента НЕ, вход которого соединен с входом переноса из младшего разряда сумматора, третьи входы второго и третьего элементов И

соединены с входом управления сложением сумматора, единичный выход первого триггера соединен с первыми входами второго элемента ИЛИ и восьмого элемента И, вторые входы этих элементов соединены с единичньм выходом второго триггера, выход второго элемента ИЛИ соединен с первым входом девятого элемента И, выход восьмого элемента И подключен к первому входу - третьего элемента ИЛИ, выход которого соединен с вторьм входом девятого элемента И, отличающийся

тем,-,что, с целью повышения быстродействия, в каждс нечетном разряде выход восьмого элемента И подключен к первому входу третьего элемента ИЛИ данного разряда и к первому входу

третьего элемента ИЛИ старшего разряда, второй вход третьего элемента ИЛИ соединен с выходом девятого элемента И и с вторым входом третьего элемента ИЖ старшего разряда, в каждом четном разряде первый и второй входы девятого элемента И соединены с первьм и вторым входами девятого элемента И старшего разряда, а третий вход девятого элемента И соединен с

выходом второго элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Накапливающий сумматор | 1985 |

|

SU1264165A1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2269153C2 |

| Арифметическое устройство | 1983 |

|

SU1239710A1 |

| Двоичный накапливающий сумматор | 1983 |

|

SU1112363A1 |

| Арифметическое устройство | 1979 |

|

SU842794A1 |

| Параллельный накапливающий сумматор | 1979 |

|

SU911517A1 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2006 |

|

RU2306596C1 |

| Накапливающий сумматор | 1984 |

|

SU1176323A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2395833C2 |

| Накапливающий сумматор | 1982 |

|

SU1043638A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в процессорах ЭВМ. Цель изобретения - повышение быстродействия. Накапливающий сумматор содержит в каждом разряде девять элементов И 1-9, три элемента ИЛИ 10-12, три триггера 13-15, элемент НЕ 16, выходы переноса 17, 18, 19, вход 20 управления пересылкой кода сумматора, вход 21 управления .сложением, вход 22 разрешения приема кода сумматора, информационный вход, 23. 1 ил.

| Карцев М.А | |||

| Арифметика цифровых машин | |||

| - М.: Наука, 1969, с | |||

| Деревянная повозка с кузовом, устанавливаемым на упругих дрожинах | 1920 |

|

SU248A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Накапливающий сумматор | 1985 |

|

SU1264165A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-08-23—Публикация

1987-01-04—Подача