Изобретение относится к цифровой вычислительной технике и предназначается для использования в составе цифровых вычислительных машин.

Цель изобретения - повышение быстродействия.

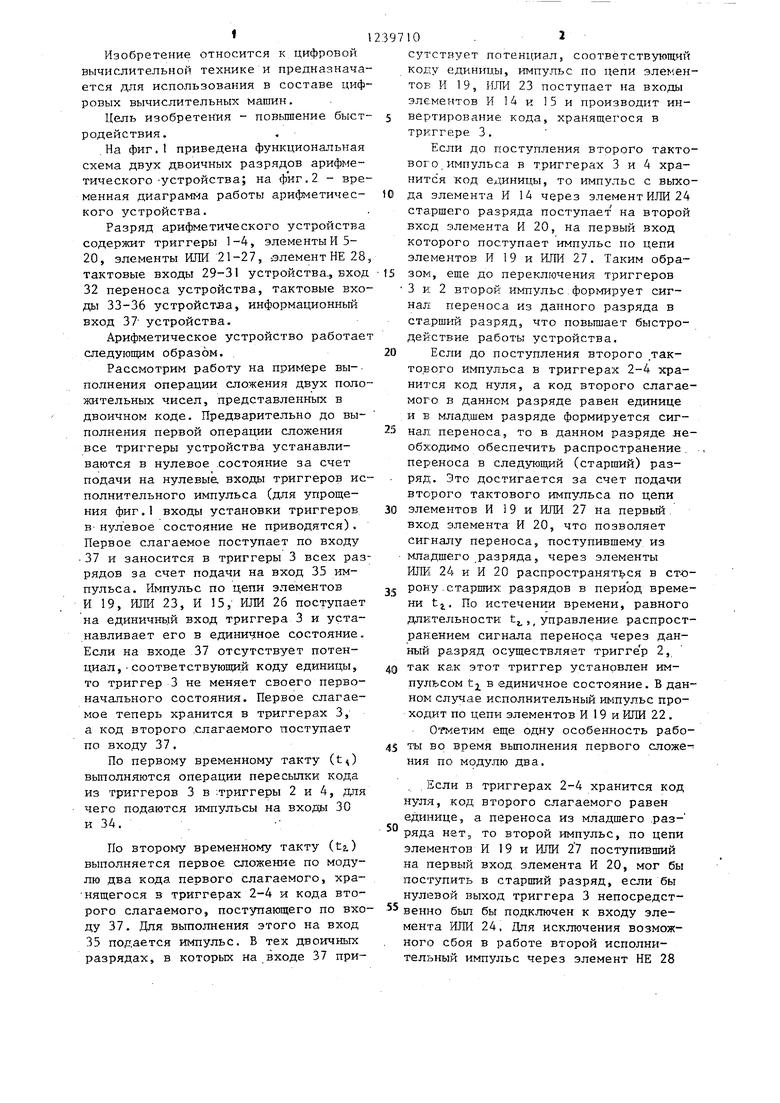

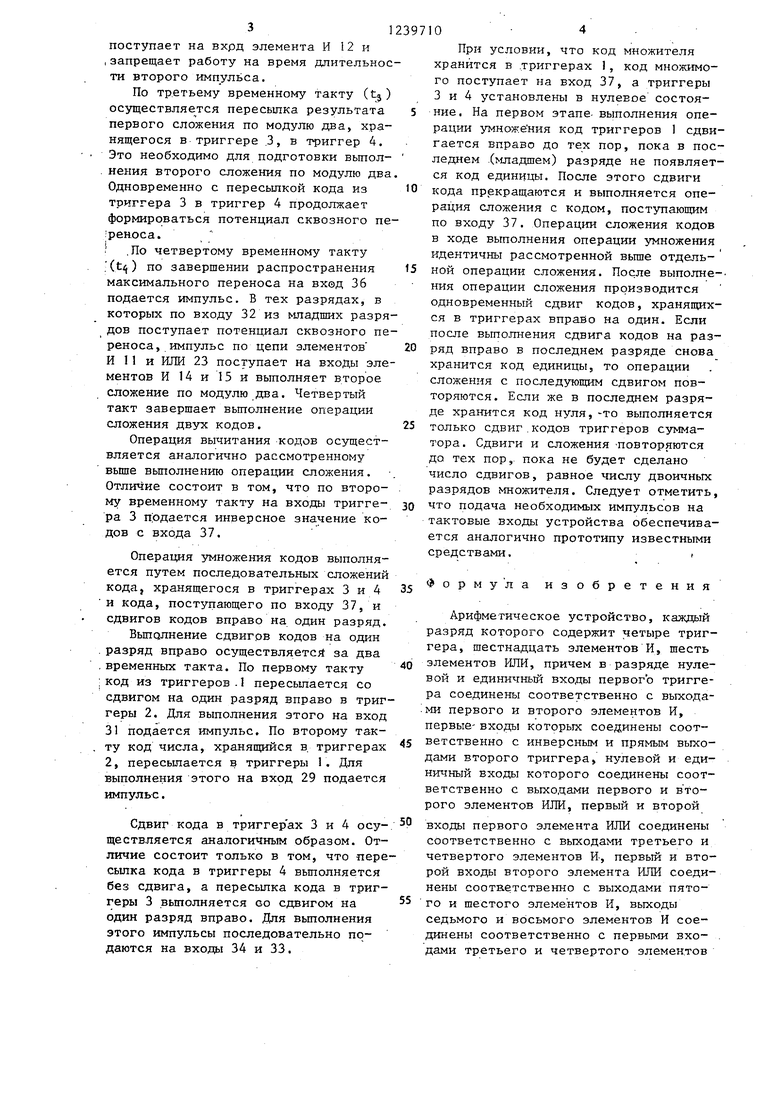

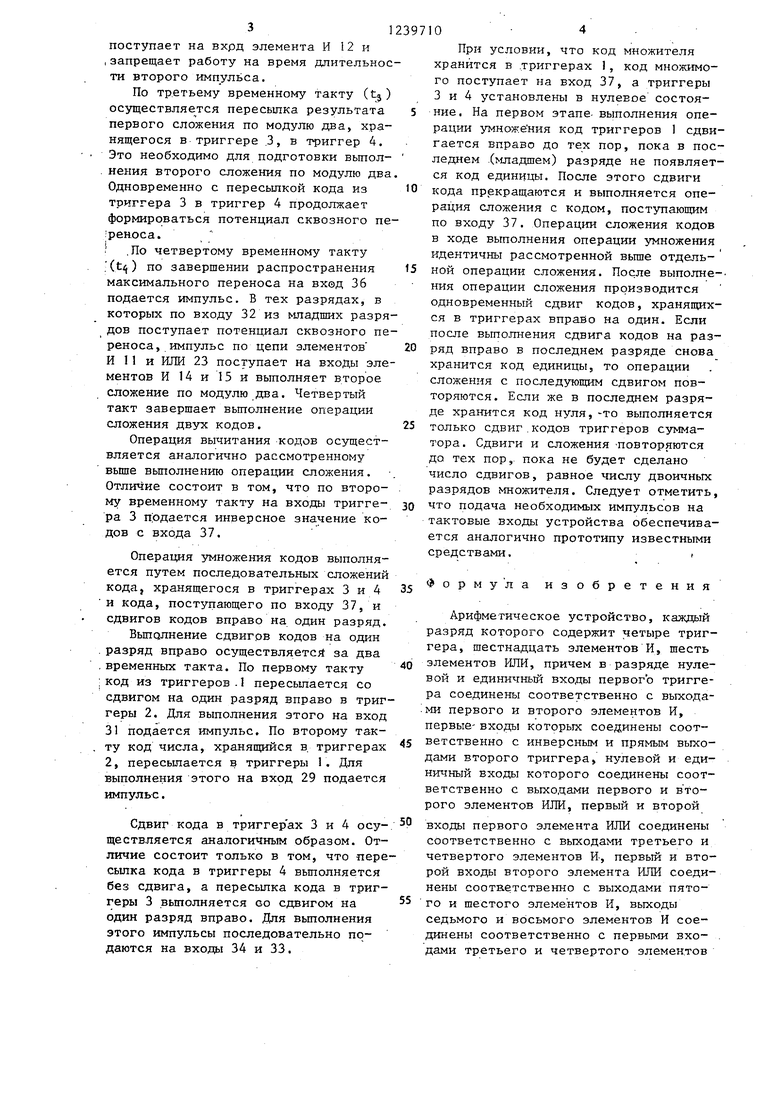

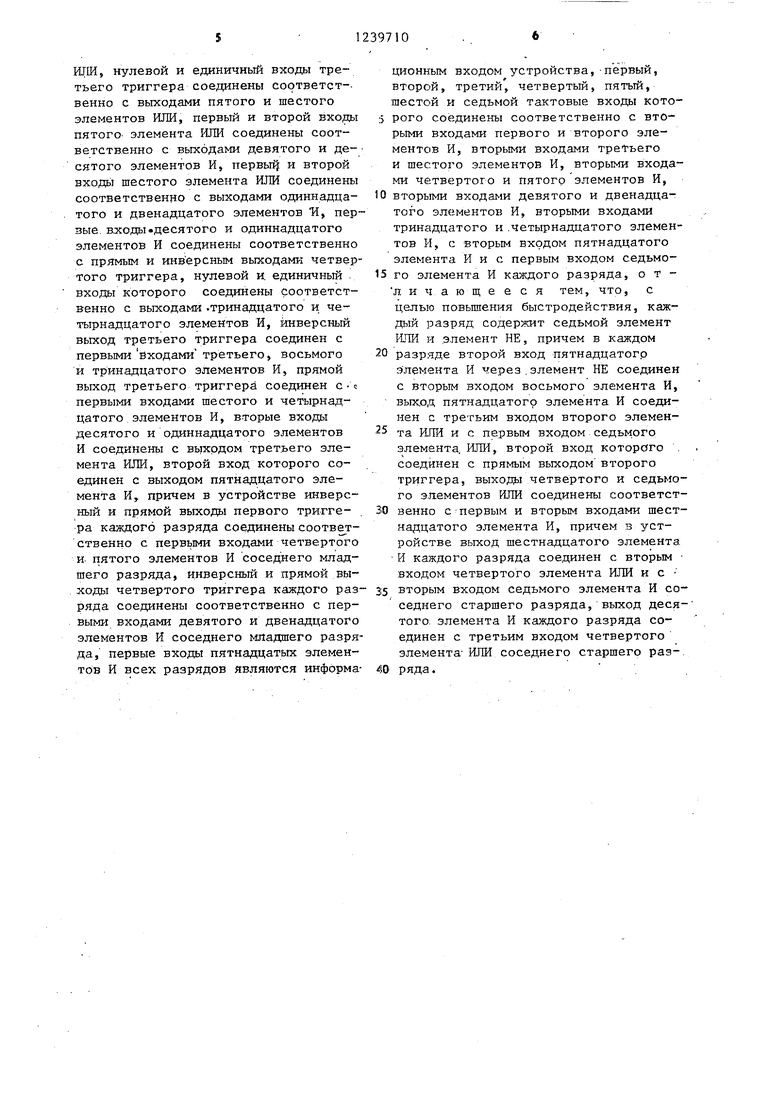

На фиг.1 приведена функциональная схема двух двоичных разрядов арифметического -устройства; на фиг.2 - временная диаграмма работы арифметического устройства.

Разряд арифметического устройства содержит триггеры 1-4, элементы И 5- 20, элементы ИЛИ 21-27, -элемент НЕ 28 тактовые входы 29-31 устройства,, вход 32 переноса устройства, тактовые входы 33-36 устройства, информационный вход 37- устройства.

Арифметическое устройство работает следующим образом.

Рассмотрим работу на примере вы- полнения операции сложения двух положительных чисел, представленных в двоичном коде. Предварительно до вы- полнения первой операции сложения все триггеры устройства устанавливаются в нулевое .состояние за счет подачи на нулевые, входы триггеров исполнительного импульса (для упрощения фиг.1 входы установки триггеров в- нулевое состояние не приводятся). Первое слагаемое поступает по входу 37 и заносится в триггеры 3 всех разрядов за счет подачи на вход 35 импульса. Импульс по цепи элементов И 19, ИЛИ 23, И 15,- ИЛИ 26 поступает на единичнь1й вход триггера 3 и устанавливает его в единично.е состояние. Если на входе 37 отсутствует потенциал, соответствующий коду единицы, то триггер 3 не меняет своего первоначального состояния. Первое слагаемое теперь хранится в триггерах 3, а код второго .слагаемого поступает по входу 37.

По первому временному такту (t) выполняются операции пересьшки кода из триггеров 3 в -.триггеры 2 и 4, для чего подаются импульсы на входы 30 и 34.

По второму временному такту (tj.) выполняется первое сложение по модулю два кода первого слагаемого, хра- нящегося в триггерах 2-4 и кода второго слагаемого, поступающего по входу 37. Для выполнения этого на вход 35 подается импульс. В тех двоичных разрядах, в которых на входе 37 при

39710 . 2

сутствует потенциал, соответствующий коду ;диницы, импульс по цепи элементов И 19, HIM 23 поступает на входы элементов И 14 к 15 и производит ин5 вертирование кода, хранящегося в триггере 3.

Если до поступления второго тактового импульса в триггерах 3 и 4 хранится код единицы, то импульс с выхо)0 да элемента И 14 через элемент ИЛИ 24 старшего разряда поступает на второй вход элемента И 20, на первый вход которого поступает импульс по цепи элементов И 19 и ИЛИ 27. Таким обра1S зом, еще до переключения триггеров 3 и 2 второй импульс.формирует сигнал переноса из данного разряда в старший разряд, что повышает быстродействие работы устройства.

20 Если до поступления второго .тактового импульса в триггерах 2-4 хранится код нуля, а код второго слагаемого в данном разряде равен единице и в младшем разряде формируется сиг25 нал переноса. 5 то в данном разряде необходимо обеспечить распространение. переноса в следующий (старший) разряд. Это достигается за счет подачи второго тактового импульса по цепи

30 элементов И 19 и ИЛИ 27 на первый. вход элемента И 20, что позволяет сигналу переноса, поступившему из - мла.дшего разряда, через элементы ИЛИ 24 и И 20 распространяться в сто35 рону.старших разрядов в период времени tj,. По истечении времени, равного длительности tj, управление распространением сигнала перенора через данный разряд осуществляет тригге р 2,

40 так как этот триггер установлен импульсом с- в единичное состояние. В данном случае исполнительный импульс проходит по цепи элементов И 19 и ИЛИ 22 . OrNseTHM еще одну особенность рабо45 ты во время выполнения первого сложе- ния по модулю два.

Если в триггерах 2-4 хранится код нуля, код второго слагаемого равен единице, а переноса из младшего .раз- ряда нет, то второй импульс, по цепи элементов И 19 и ИЛИ 27 поступивший на первый вход элемента И 20, мог бы поступить в старший разряд, если бы нулевой выход триггера 3 непосредст- 55 венно бьш бы подключен к входу элемента ИЛИ 24, Для исключения возможного сбоя в работе второй исполнительный импульс через элемент НЕ 28

50

312397

поступает на вхрд элемента И 12 и запрещает работу на время длительности второго импульса.

По третьему временному такту (tj ) осуществляется пересылка результата 5 первого сложения по модулю два, хранящегося в триггере .3, в триггер 4. Это необходимо для подготовки выпол- нения второго сложения по модулю два. Одновременно с пересылкой кода из Ю триггера 3 в триггер 4 продолжает формироваться потенциал сквозного пе- реноса.

,По четвертому временному такту (ц) по завершении распространения 15 максимального переноса на вход 36 подается импульс. В тех разрядах, в которых по входу 32 из младших разрядов поступает потенциал сквозного переноса, импульс по цепи элементов 20 И I1 и ИЛИ 23 поступает на входы элементов И 14 и 15 и выполняет второе сложение по модулю два. Четвертый такт завершает выполнение операции сложения двух кодов.25

Операция вычитания кодов осуществляется аналогично рассмотренному вьше вьшолнению операции сложения. Отличие состоит в том, что по второ- му временному такту на входы тригге- зо ра 3 подается инверсное значение кодов с входа 37.

Операция умножения кодов выполняется путем последовательных сложений кода, хранящегося в триггерах 3 и 4 35 и кода, постуцающего по входу 37, и сдвигов кодов вправо на один разряд. Выполнение сдвигов кодов на один разряд вправо осуществляется за два временных такта. По первому такту код из триггеров . 1 пересыпается со сдвигом на один разряд вправо в триггеры 2. Для выполнения этого на вход 31 подается импульс. По второму такту код числа, хранящийся в. триггерах 2, пересылается в триггеры Г. Для выполнения этого на вход 29 подается импульс.

Сдвиг кода в триггер ах 3 и 4 осу- Р ществляется аналогичным образом. Отличие состоит только в том, что пересылка кода в триггеры 4 выполняется без сдвига, а пересылка кода в триггеры 3 выполняется со сдвигом на один разряд вправо. Для выполнения этого импульсы последовательно подаются на входы 34 и 33,

10 4 .

При условии, что код множителя хранится в .триггерах 1, код множимого поступает на вход 37, а триггеры 3 и 4 установлены в нулевое состояние. На первом этапе- выполнения операции умноже ния код триггеров 1 сдвигается вправо до тех пор, пока в последнем .(младшем) разряде не появляется код единицы. После этого сдвиги кода прекращаются и выполняется операция сложения с кодом, поступающим по входу 37. Операции сложения кодов в ходе выполнения операции умножения идентичны рассмотренной выше отдель- ной операции сложения. После выполне кия операции сложения производится одновременный сдвиг кодов, хранящихся в триггерах впрайо на один. Если после выполнения сдвига кодов на разряд вправо в последнем разряде снова хранится код единицы, то операции сложения с последуюшлм сдвигом повторяются. Если же в последнем разряде хранится код нуля, -то выполняется только сдвиг.кодов триггеров сумматора. Сдвиги и сложения Повторяются до тех пор, пока не будет сделано число сдвигов, равное числу двоичных разрядов множителя. Следует отметить что подача необходимых импульсов на тактовые входы устройства обеспечивается аналогично прототипу известными средствами.Формула изобретения

Арифметическое устройство, каждый разряд которого содержит четыре триггера, шестнадцать элементов И, шесть элементов ИЛИ, причем в разряде нулевой и единичный входы первого триггера соединены соответственно с выходами первого и второго элементов И, первые- входы которых соединены соответственно с инверсным и прямым выходами второго триггера, нулевой и единичный входы которого соединены соответственно с выходами первого и в то- рого элементов ИЛИ, первый и второй

входы первого элемента ИЛИ соединены соответственно с выходами третьего и четвертого элементов И, пе.рвый и второй входы второго элемента ИЛИ соединены соответственно с выходами пято- го и шестого элементов И, выходы седьмого и восьмого элементов И соединены соответственно с первыми вхо- дами третьего и четвертого элементов

ИХШ, нулевой и единичный входы третьего триггера соединены соответст-- венно с выходами пятого и шестого элементов ИЛИ, первый и второй входы пятого- элемента ИЛИ соединены соответственно с выходами девятого и де- сятого элементов И, первьй} и второй входьт шестого элемента ИЛИ соединены соответственно с выходами одиннадцатого и двенадцатого элементов И, первые, входы«десятого и одиннадцатого элементов И соединены соответственно с прямым и инверсным выходами четвертого триггера, нулевой и. единичный . входы которого соединены соответственно с выходами .тринадцатого и четырнадцатого элементов И, инверсный выход третьего триггера соединен с первыми входами третьего, восьмого и тринадцатого элементов И, прямой выход третьего триггера соединен с-с первыми входами шестого и четырнадцатого элементов И, вторые входы десятого и одиннадцатого элементов И соединены с выходом третьего элемента ИЛИ, второй вход которого соединен с выходом пятнадцатого элемента И,, причем в устройстве инверсный и прямой выходы первого триггера каждого разряда соединены соответственно с первь1ми входами четвертого и. пятого элементов И соседнего младшего разряда, инверсный и прямой выходы четвертого триггера каждого разряда соединены соответственно с первыми входами девятого и двенадцатого элементов И соседнего младшего разряда, первые входы пятнадцатых элементов И всех разрядов являются информационным входом устройства,-первый, второй, третий , четвертый, пятый, шестой и седьмой тактовые входы кото- 5 рого соединены соответственно с вторыми входами первого и второго элементов И, втор)ыми входами третьего и шестого элементов И, вторыми входами четвертого и пятого элементов И,

10 вторыми входами девятого и двенадцатого элементов И, вторыми входами тринадцатого и .четырнадцатого элементов И, с вторым входом пятнадцатого элемента И и с первым входом седьмо15 го элемента И каждого разряда, о т - л и ч а ю щ е е с я тем, что, с целью повьшгения быстродействия, каждый разряд содержит седьмой элемент ИЛИ и элемент НЕ, причем в каждом

20 разряде второй вход пятнадцатогр

элемента И через элемент НЕ соединен с вторым входом восьмого элемента И, выход пятнадцатого элемента И соединен с третьим входом второго элемен25 та ИГИ и с первым входом седьмого элемента, ИЛИ, второй вход которого . соединен с прямым выходом второго триггера, выхода, четвертого и седьмого э.лементов ИЛИ соединены соответст30 венно с-первым и вторым входами шестнадцатого элемента И, причем з устройстве выход шестнадцатого элемента И каждого разряда соединен с вторым входом четвертого элемента ИЖ и с

35 вторым входом седьмого элемента И соседнего старшего разряда, выход десятого, элемента И каждого разряда соединен с третьим входом четвертого элемента ИЛИ соседнего старшего раз-.

40 ряда.

фиг.1

t2

Пересылка кода из ТрЗ 8 ТрЧ- fnepBafl)

Сложение кодов по маЗулнг 2 (перВое)

Формирование потенциала переноса.

Пересылка кода из Тр. 3 6 Тр. (впюрал,

Сложение кодов по модулfoZ (второе)

Редактор Е.Папп

Составитель А. Клюев Техред Л.Олейник

Заказ 3397/49 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР, .

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,4

.2

Корректор Е.Рошко

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1979 |

|

SU842794A1 |

| Накапливающий сумматор | 1985 |

|

SU1262479A1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2261469C1 |

| Двухтактный п-разрядный сумматор накапливающего типа | 1974 |

|

SU538365A1 |

| Цифровой интерполяционный фильтр | 1990 |

|

SU1728962A1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2269153C2 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2262735C1 |

| СПОСОБ И УСТРОЙСТВО ВЫПОЛНЕНИЯ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ ПРИ МИНИМАЛЬНЫХ ЗАТРАТАХ ОБОРУДОВАНИЯ | 2005 |

|

RU2287849C1 |

| Двоичный накапливающий сумматор | 1983 |

|

SU1112363A1 |

| РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА ВЛАСОВА | 2006 |

|

RU2309536C1 |

Изобретение относится к цифро- ,вой вычислительной технике и может быть использовано в составе как специализированных ЭВМ, так и ЭВМ широкого назначения. Цель изобретения - повьшение быстродействия за счет совмещения во времени вьшолнения отдельных элементарных операций. Поставленная цель достигается тем, что в арифметическом устройстве, каждый разряд которого содержит четыре триггера., шестнадцать элементов И и шесть элементов ИЛИ, в каждай разряд дополнительно вводятся седьмой элемент ИЛИ и элемент НЕ с-соответствзгняцими связями. 2 ил. 00 со Nl

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 0 |

|

SU318941A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Арифметическое устройство | 1979 |

|

SU842794A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

Авторы

Даты

1986-06-23—Публикация

1983-07-15—Подача