Изобретение относится к цифровой вычислительной технике и предназначается для использования в процессорах ЭВМ или в устройствах цифровой автоматики.

Цель изобретения - упрощение конструкции накапливающего сумматора.

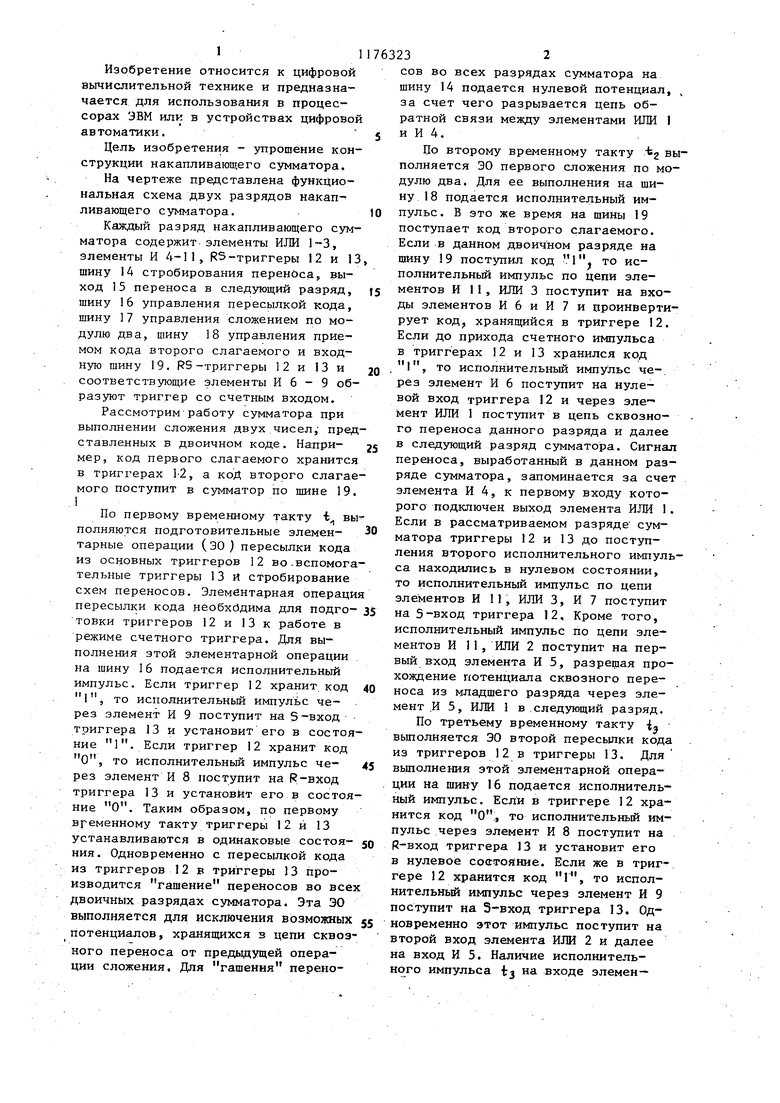

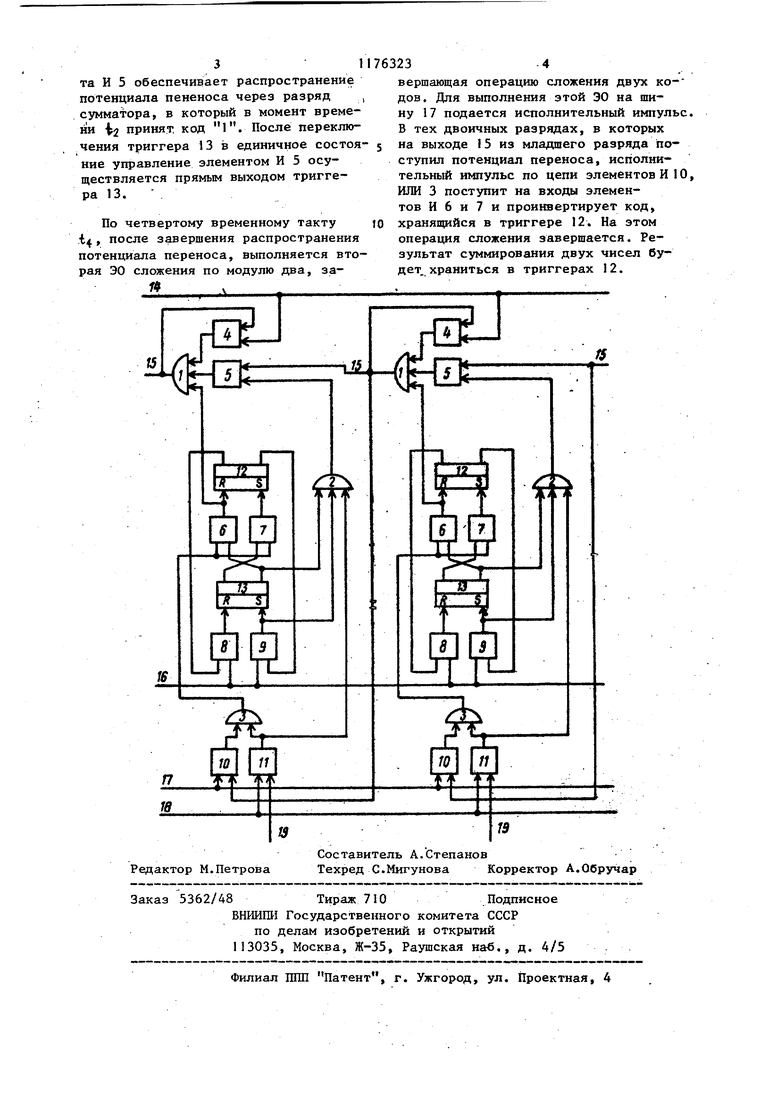

На чертеже представлена функциональная схема двух разрядов накапливающего сумматора.

Каждый разряд накапливающего сумматора содержит элементы ИЛИ 1-3, элементы И 4-11, R5-триггеры 12 и 13 шину 14 стробирования переносац выход 15 переноса в следующий разряд, шину 16 управления пересылкой кода, шину 17 управления сложением по модулю два, шину 18 управления приемом кода второго слагаемого и входную шину 19. RS -триггеры 12 и 13 и соответствующие элементы И 6 - 9 образуют триггер со счетным входом.

Рассмотрим работу сумматора при выполнении сложения двух чисел, представленных в двоичном коде. Например, код первого слагаемого хранится в триггерах 1-2, а коД второго слагаемого поступит в сумматор по шине 19. I

По первому временному такту t выполняются подготовительные элемен- тарные операции (ЭО) пересылки кода из основных триггеров 12 во.вспомогательные триггеры 13 и стробирование схем переносов. Элементарная операци пересылки кода необхбдима для подготовки триггеров 12 и 13 к работе в режиме счетного триггера. Для выполнения этой элементарной операции на шину 16 подается исполнительный импульс. Если триггер 12 хранит код 1, то исполнительный импульс через элемент И 9 поступит на 5-вход триггера 13 и установит его в состояние 1. Если триггер 12 хранит код о, то исполнительньй импульс через элемент И 8 поступит на R-вход триггера 13 и установит его в состояние О. Таким образом, по первому временному такту триггеры 12 и 13 устанавливаются в одинаковые состояния. Одновременно с пересылкой кода из триггеров 12 в триггеры 13 производится гашение переносов во все двоичных разрядах сумматора. Эта 30 выполняется для исключения возможных потенциалов, хранящихся в цепи сквозного переноса от предьщущей операции сложения. Для гашения переносов во всех разрядах сумматора на шину 14 подается нулевой потенциал, , за счет чего разрывается цепь обратной связи между элементами ИЛИ 1 и И 4.

Оо второму временному такту tg выполняется ЭО первого сложения по модулю два. Для ее выполнения на шину 18 подается исполнительный импульс . В это же время на шины I9 поступает код второго слагаемого. Если в данном двоичном разряде на шину 19 поступил код то исполнительньй импульс по цепи элементов И П, ИЛИ 3 поступит на входы элементов И 6 и И 7 и цроинвертирует код хранящийся в триггере 12. Если до прихода счетного импульса в триггерах 12 и 13 хранился код

I, то исполнительный импульс че-. рез элемент И 6 поступит на нулевой вход триггера 12 и через элв мент ИЛИ 1 поступит в цепь сквозного переноса данного разряда и далее в следующий разряд сумматора. Сигнал переноса, выработанный в данном разряде сумматора, запоминается за счет элемента И 4, к первому входу которого подключен выход элемента ИЛИ 1. Если в рассматриваемом разряде сумматора триггеры 12 и 13 до поступления второго исполнительного импульса находились в нулевом состоянии, то исполнительный импульс по цепи элементов И П, ИЛИ 3, И 7 поступит на 5-вход триггера 12, Кроме того, исполнительный импульс по цепи элементов И 11, ИЛИ 2 поступит на первый вход элемента И 5, разрещая прохождение потенциала сквозного переноса из младшего разряда через элемент И 5, ИЛИ 1 в .следующий разряд. По третьему временному такту „ выполняется ЭО второй пересылки кода из триггеров 12 в триггеры 13. Для вьшолнения этой элементарной операции на шину 16 подается исполнительный импульс. Если в триггере 12 хранится код о, то исполнительный импульс через элемент И 8 поступит на R-вход триггера 13 и установит его в нулевое состояние. Если же в триггере 12 хранится код Г, то исполнительный импульс через элемент И 9 поступит на 3-вход триггера 13. Одновременно этот импульс поступит на второй вход элемента ИЛИ 2 и далее на вход И 5. Наличие испол1штельного импульса tj на входе элемен-

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоичный накапливающий сумматор | 1983 |

|

SU1112363A1 |

| Накапливающий сумматор | 1985 |

|

SU1264165A1 |

| Параллельный накапливающий сумматор | 1979 |

|

SU911517A1 |

| Накапливающий сумматор | 1987 |

|

SU1418701A1 |

| Арифметическое устройство | 1979 |

|

SU842794A1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2269153C2 |

| Накапливающий сумматор | 1985 |

|

SU1262479A1 |

| Накапливающий сумматор | 1982 |

|

SU1043638A1 |

| Накапливающий сумматор | 1987 |

|

SU1418705A1 |

| Двухтактный п-разрядный сумматор накапливающего типа | 1974 |

|

SU538365A1 |

НАКАПЛИВАЮЩИЙ СУММАТОР, со держащий в каждом разряде первый и , второй Р5-триггеры, семь элементов И и два элемента ИЛИ, причем входы . первого элемента И соединены с шиной :управления сложением по модулю два и с выходом переноса предыдущего разряда сумматора соответственно, входы второго элемента И соединены с шиной управления приемом кода второго слагаемого и с соответствующим разрядом входной шины сумматора соответственно, выходы первого и второго элементов И подключены к соответствующим входам первого элемента ИЛИ, выход которого соединен с первыми входами третьего и четвертого элементов И, выходы третьего и четвертого элементов И соединены соответственно с (I- и S-входами пер-: вого ЯЗ триггера, инверсный выход которого соединен с первым входом пятого элемента И, а прямой выход с первым входом шестого элемента И, 8С Гогл тдл I БЕБЛйОТь}/, вторые входы пятого и шестого элементов И подключены к шине управления пересылкой кода сумматора, прямой и инверсный вьтходы второго RS-триггера соединены с вторыми входами третьего и четвертого элементов И соответственно, первый вход седьмого элемента И соединен с выходом предьдущего разряда сумматора, выход седьмого элемента И соединен с первым входом второго элемента ИЛИ, выход которого подключен к выходу переноса данного разряда сумматора, отличающийся тем, что, с целью упрощения конструкции, накапливающий сумW матор содержит в каждом разряде восьмой элемент И и третий элемент ИЛИ, первый вход восьмого элемента И соединен с выходом , второго элемента ИЛИ, а второй вход - с шиной стробирования переноса сумматора, а выход подключен к второму входу второ | го элеме| та ИЛИ, третий вход котороо го соединен с выходом третьего элемента И, первый вход третьего эле00 мента ИЛИ соединен с;прямым выходом го второго / 3-триггера, R- н 5-входы со которого подключены к выходам пятого и шестого элементов И соответственно, второй вход третьего элемента ИЛИ соединен с выходом шестого элемента И, а третий вход - с выходом второго элемента И, выход третьего элемента ИЛИ соединен с вторым вход6м седьмого элемента И.

| Папернов А.А | |||

| Логические основы ЦВТ | |||

| М.: Советское радио, 1972, с | |||

| Система механической тяги | 1919 |

|

SU158A1 |

| Насос | 1917 |

|

SU13A1 |

| Двоичный накапливающий сумматор | 1983 |

|

SU1112363A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-08-30—Публикация

1984-01-06—Подача