(pus.i

Изобретение относится к вычислительной технике и может быть использовано для контроля дискретных сиг- Налов,Целью изобретения является расширение области применения за счет фиксации приема контролируемых последовательностей длиной менее m разрядов,

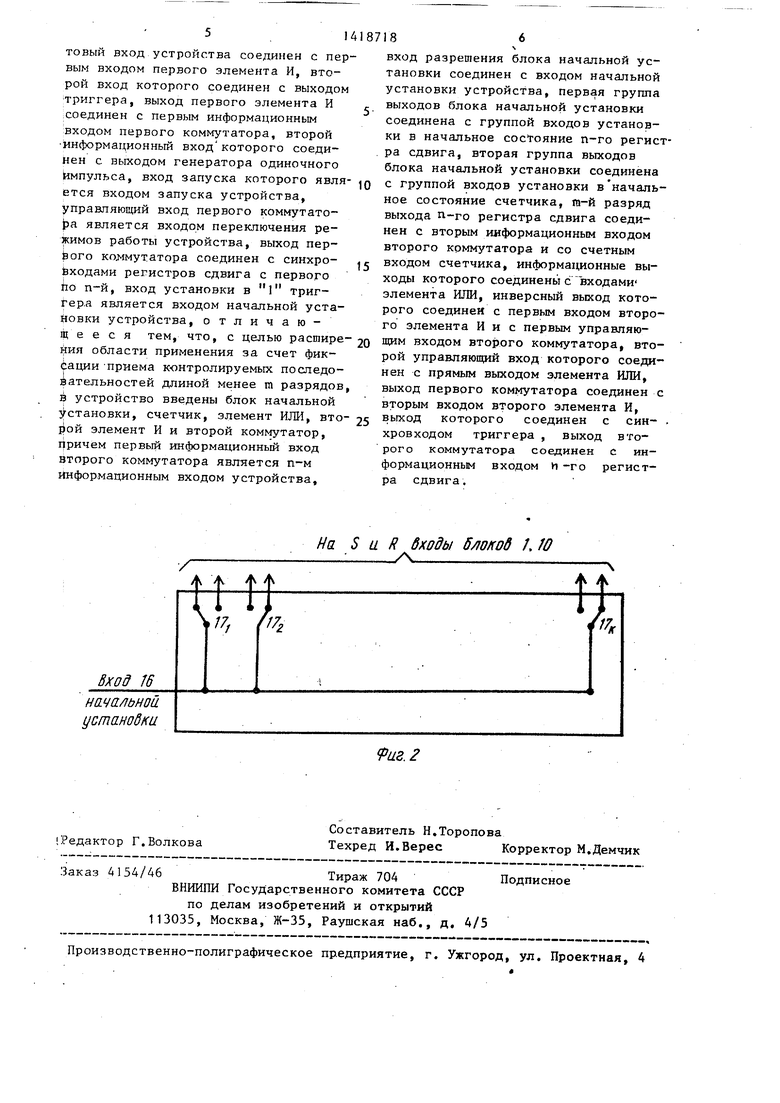

На фиг.1 приведена схема предлага рмого устройства; на фиг.2 - схема блока начальной установки.

Устройство содержит п регистров 1 сдвига, триггер 2, элемент И 3, ге- нератор 4 одиночного импульса, блок 5 индикации, первый коммутатор 6, второй коммутатор 7, блок 8 начальной установки, элемент ИЛИ 9, счетчик 10, элемент И 11, группу 12 ин- формационнык входов устройства, вход 13 запуска генератора одиночного импульса, вход 14 переключения режимов работы, тактовый вход 15, вход 16 начальной установки, переключатели

1.Л- 1 7к.

. Устройство работает следующим образом.

На входе 14 переключения режимов устройства устанавливается сигнал задания режима записи информации и, таким образом, разрешается прохождение, через первый коммутатор 6 тактовых импульсов с выхода элемента И 3 на с инхровходы регистров 1 сдвига и вход элемента И 1, Перед началом работы в блоке 8 начальной установки набирается информация, которая заносится в п-й регистр 1 сдвига и код числа циклов. По сигналу начальной установки (короткому импульсу), подаваемому на вход 16 устройства, набранная информация заносится на п-й регистр 1 сдвига и в счетчик 10, преставляющий собой вычитающий счетчик, По этому же сигналу устанавливается в единичное состояние триггер 2 и разрешает прохождение тактовых импульсов по тактовому входу 15 через элемент И 3. При контроле начальных разрядов длинных последовательностей сигналов в первый разряд п-го регистра 1 сдвига записывается ноль (а в остальные - единицы), в счетчик 10 также записываются, нули. В этом случае, единица на инверсном выходе элемента ИЛИ 9 разрешает прохождение синхроимпульсов через элемент И 11 на синхровход триггера 2,.

0

5 0 5

0 j О g

0

5

а п-й контролируемой цифровой по.сле- довательности через коммутатор 7 на информационный вход (вход первого разряда) п-го регистра 1 сдвига.

Синхроимпульсы поступают на син- хровходы регистров 1 сдвига и по каждому синхроимпульсу на них записываются логические значения сигналов, поступающих с группы 12 входов устройства. Первый элемент И 3 пропускает синхроимпульсы до тех пор, пока регистры 1 сдвига полностью не заполняются контролируемыми последовательностями, т.е. до тех пор, пока ноль, записанный в первый разряд п-го регистра сдвига, не сбросит триггер 2, который нулевым потенциалом .на выходе запрещает прохождение синхроимпульсов через элемент И 3. Запись информации в регистры 1 сдвига прекращается и в них хранятся контролируемыме. последовательности.

При необходимости контроля коротких последовательностей длительностью К тактов, при , где m - длина регистров 1 сдвига устройства, а К - длина контролируемых последовательностей, по сигналу начальной установки ноль заносится не в первый разряд п-го регистра сдвига 1, а в К-й от конца регистра сдвига разряд. В счетчик 10 записываются нули.

Запись информации происходит аналогично вышеописанному и по окончании поступления короткой последовательности на регистры 1 сдвига, триггер 2 сбрасывается нулем, записанным в k-й от конца п-го регистра сдвига разряд, и фиксирует окончание приема информации.

При контроле в длинных последовательностях не первых m разрядов, а последующих m разрядов, по сигнал начальной установки 16 с блока 8 ноль заносится в первый рязряд п-го регистра 1 сдвига, триггер 2 устанавливается в единицу, а в счетчик 10 записывается код числа циклов, равного единице. В этом числе единичный потенциал на прямом вьрюде элемента ИЛИ 9 поступает на второй управляющий вход коммутатора 7 и разрешает подключение выхода последнего разря- да п-го регистра 1 сдвига к входу его первого разряда (обеспечивается зацикливание регистра). Нулевой потенциал на инверсном выходе элемента ШШ 9 з.апрещает прохождение сии3 , 14187: хроимпульсов через элемент И 11 и п-ой контролируемой последовательности через коммутатор 7,

При поступлении синхроимпульсов g на тактовый вход 15 устройства ноль, записанный в первом разряде п-го регистра 1 сдвига, продвигается по закольцованному регистру, на входы первого разряда которого при этом ю поступают единицы. По (т-1)-му синхроимпульсу ноль оказывается в последнем разряде п-го регистра 1 сдвига. По т-му синхроимпульсу этот ноль переписывается в первый рязряд п-го 15 регистра 1 сдвига и положительным перепадом на выходе последнего (т-го) разряда этого регистра из содержимого счетчика 10 вычитается единица. Счетчик обнуляется, на прямом выхо- 20 де элемента ИЛИ 9 устанавливается нулевой потенциал, а на инверсном - единичный.

Таким образом, разрешается прохождение синхроимпульсов через эле- 25 мент И I на синхровход триггера 2 и поступление п-ой контролируемой последовательности через коммутатор 7 на вход первого разряда п-го регистра 1 сдвига, цепь зацикливания кото- 30 рого разрывается. Начиная с (т+Г)-го синхроимпульса, регистры 1 сдвига заполняются информацией, необходимой оператору, при этом ноль продвигается по п-му регистру 1 сдвига в на- 5 правлении от первого разряда к последнему. По синхроимпульсу 2т триггер 2 сбрасывается и прохождение синхроимпульсов через элемент И 3 запрещается.40

На регистрах 1 сдвига зафиксированы контролируемые последовательности (разряды с (m+l) по 2т). Для контроя следующих m разрядов последова- , тельностей на счетчик 10 по сигналу 45 ачальной установки записывают код исла циклов, равный двум и т.д.

Изменение места записи нуля в п-й егистр 1 сдвига позволяет записыать на регистры 1 сдвига любые ni 50 азрядов контролируемой последоваельности.

Предположим, что на устройстве

с регистром сдвига длиной 64 .разряа необходимо проконтролировать циф- gg овую. последовательность 90 разрядов (т.е. превышающую длину регистра сдвига на 26 разрядов). В начале для, того, чтобы проконтролировать первые 64 разряда последоватепьности, ноль заносится в первый разряд п-го регистра сдвига и в сче-тчик циклов.

Затем, для,того, чтобы проконтролировать конец последовательности, ноль заносится в 26-й от конца регистра разряд , т.е. в 39-й разряд п.-го регистра сдвига и единица в младший разряд счетчика. При появлении последовательности на входах устройства ее запись на регистры сдвига начнется, начиная с 27-го разряда, таким образом будут зафиксированы последние 64 разряда контролируемой последовательности.

Отображение хранящейся в регистрах сдвига информации производится в блоке 5 тщикации в поцгаговом режиме. На входе 14 переключет-гаж режимов задается режим воспроизведения, при этом от выхода первого коммутатора 6 отключается вход элемента И 3 и подключается выход генератора 4 одиночного импульса,. При поступлении сигнала запуска (по входу 13) генератор 4 формирует одиночный импульс, который через первьгй коммутатор 6 поступает на синхровходы регистров 1 сдвигая записанную в них информацию на один разряд. Информация из последних разрядов регистров 1 при этом поступает в блок индикации. Частота , сигналов на входе 13. определяется . оператором, таким образом в блоке индикации последовательно просматривается вся записанная в регистры 1 информация.

Формула изобретенмя

Устройство для контроля цифровых последовательностей, содержащее п т-разрядных регистров сдвига (где п- число контролируемых последовательностей) , триггер, элемент И, генератор одиночного импульса, блок индикации и первый коммутатор, причем информационные входы регистров сдвига с.первого по (п-1)-й являются информационными входами устройства соответственно с первого по (п-1)-й, т-е разряды выходов регистров сдвига с первого по (п-1)-й соединены соответственно с входами с первого по (п-1)-й блоки индикации, га-й разряд выхода п-го регистра сдвига соединен с-информационным входом триггера и с п-м входом блока индикации, так514

товый вход устройства соединен с первым входом первого элемента И, второй вход которого соединен с выходом триггера, выход первого элемента И :соединен с первым информационным входом первого коммутатора, второй информационный вход которого соединен с выходом генератора одиночного импульса, вход запуска которого является входом запуска устройства, управляютдий вход первого коммутато- jsa является входом переключения режимов работы устройства, выход пер- Ього коммутатора соединен с синхро- йходами регистров сдвига с первого ho п-й, вход установки в 1 триг- гер.а является входом начальной установки устройства, отличающееся тем, что, с целью расшире- Йия области применения за счет фиксации -приема контролируемых последовательностей длиной менее m разрядов, в устройство введены блок начальной З становки, счетчик, элемент ИЛИ, второй элемент И и второй коммутатор. Причём первый информационный вход второго коммутатора является п-м Информационным входом устройства.

186

вход разрешения блока начальной установки соединен с входом начальной установки устройства, первая группа выходов блока начальной установки соединена с группой входов установки в начальное coctoяниe п-го регистра сдвига, вторая группа выходов блока начальной установки соединена

группой входов установки в начальное состояние счетчика, tn-й разряд выхода п-го регистра сдвига соединен с вторым информационным входом второго коммутатора и со счетным

входом счетчика, информационные выходы которого соединены с входами элемента ИЛИ, инверсный выход которого соединен с первым входом второго элемента И и с первым управляющим входом второго коммутатора, второй управляющий вход которого соединен с прямым выходом элемента ИЛИ, выход первого коммутатора соединен с вторым входом второго элемента И,

выход которого соединен с син- . хровходом триггера , выход второго коммутатора соединен с информационным входом И-го регистра сдвига.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

| Устройство для контроля цифровых последовательностей | 1988 |

|

SU1603388A1 |

| Коррелятор | 1985 |

|

SU1309038A1 |

| Устройство для определения среднего арифметического значения | 1986 |

|

SU1310840A1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1742753A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439618A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1553980A1 |

| Устройство для контроля ввода информации | 1988 |

|

SU1647567A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля дискретных сигналов. Целью изобретения является расширение функциональных возможностей за счет фиксации приема контролируемых последовательностей длиной менее m разрядов. Цоставленная цель достигается введением коммутатора 7, блока 8 начальной установки, элемента ИЛИ 9, счетчика 10 и элемента И I1. 2 ип.

Hd S и. R Входы блок об Л W

tMf

4/7/ га

Вход 76

начальной устанодка

417

Риг.2

| Устройство для контроля многовыходных цифровых узлов | 1982 |

|

SU1076908A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля цифровых последовательностей | 1983 |

|

SU1238081A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-08-23—Публикация

1987-01-04—Подача