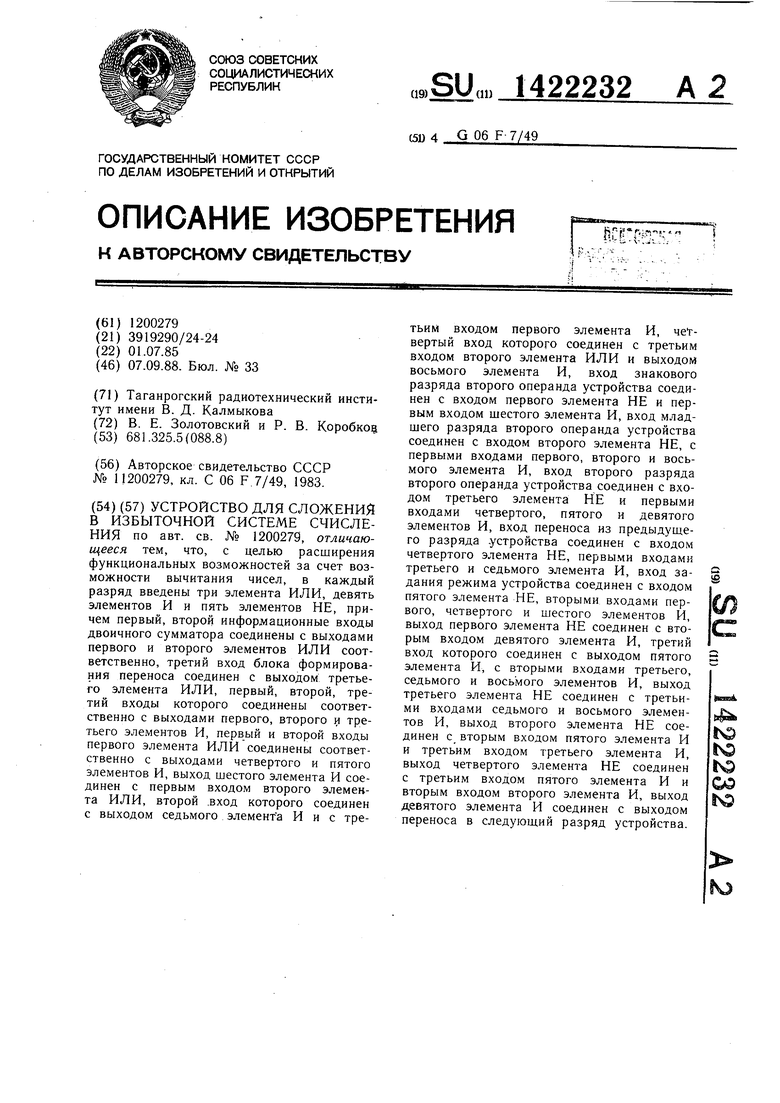

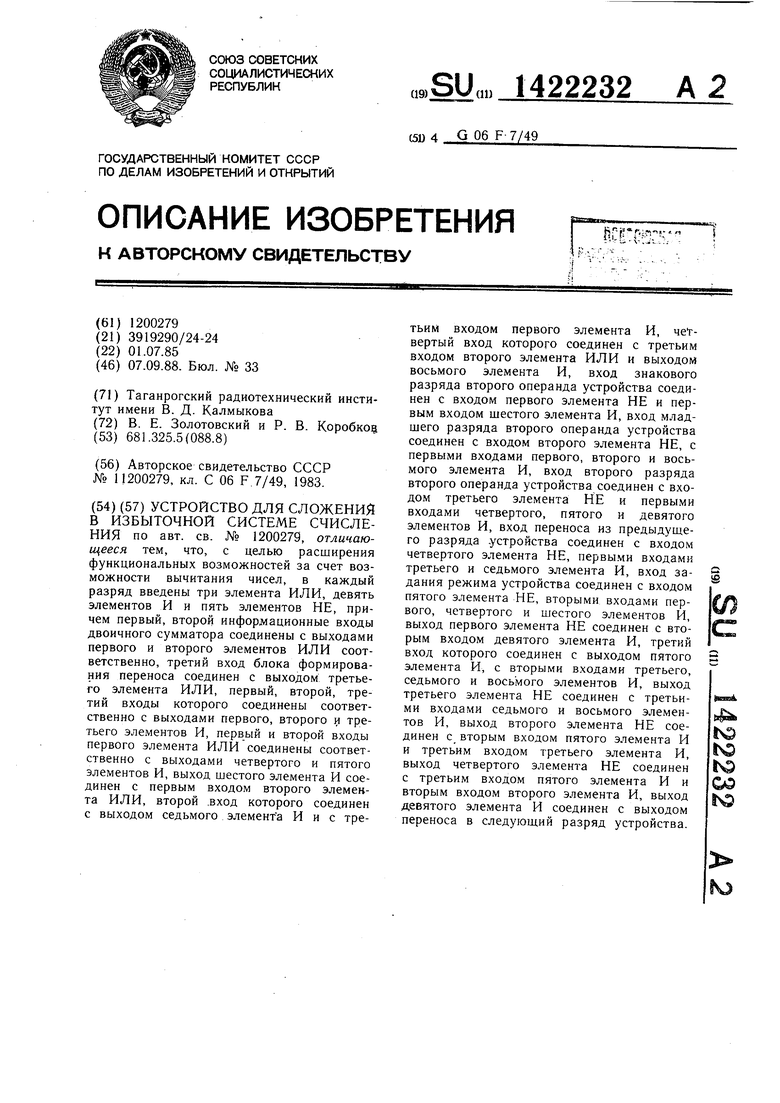

, Изобретение относится к вычислительной технике, может быть использовано при {Конструировании специализированных и уни- версальных вычислительных устройств и является усовершенствованием известного устройства по авт. св. № 1200279.

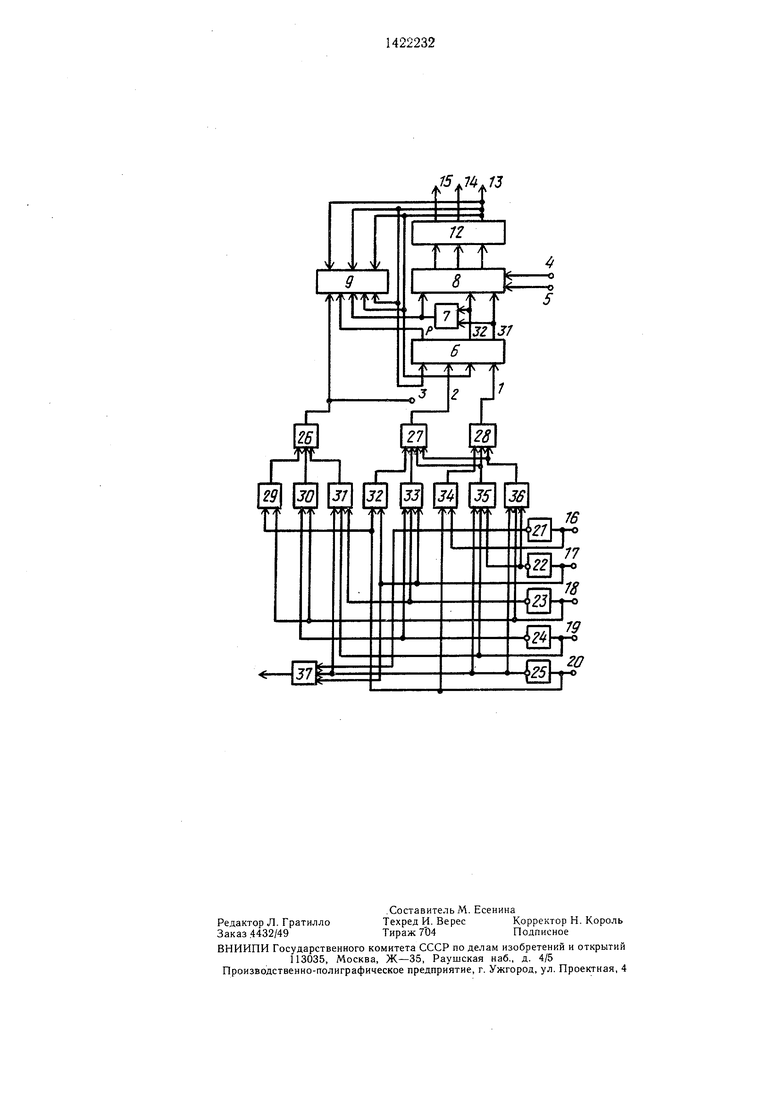

; Целью изобретения является расширение функциональных возможностей за счет iвозможности вычитания чисел, i На чертеже представлена функциональ- (ная схема одного разряда устроства. i Устройство содержит входы 1-3 сла- : гаемых, входы 4 и 5 переноса, двоичный i сумматор 6, элемент И 7, формирователь 8 i суммы, блок 9 формирования переноса, ; выходы 10 и 1 переноса в следующий : разряд, регистр 12, выходы 13-15 суммы, вход 16 знакового разряда очередного сла- i гаемого, входы 17 и 18 второго и млад- : шего разрядов очередного слагаемого, вход ; 19 переноса из предыдуш,его разряда уст- ройства, вход 20 управления сложением, элементы НЕ 21-25, элементы ИЛИ 26-28, элементы И 29-37, выход 38 переноса в следующий разряд устройства (выходы 10, 11 и 38 не обозначены).

Рассмотрим работу устройства.

В исходном состоянии регистр 12 сброшен в ноль. На вход 20 подается сигнал «1, на входы 16-18 подаются биты первого слагаемого. Через элементы И 34, 32 и 29 и элементы ИЛИ 28, 27 и 26 разряд, не меняясь, поступает на входы 1-3 устройства для сложения в избыточном коде, преобразуется в нем в вспомогательный код и записывается в регистр 12. Сигналы перехода при этом не возникают. При выполнении операции сложения на входе 20 остается сигнал 1 и на входы 16-18 подаются биты второго слагаемого. Второе слагаемое, также не меняясь, поступит на входы 1-3 устройства для сложения в избыточном коде и в последнем сформируется сумма. При выполнении операции сложения работа предлагаемого

устройства не отличается от работы известного.

При выполнении операции вычитания на вход 20 подается сигнал «О и на входы 16-18 - биты вычитаемого. С помощью элементов ИЛИ 26-28 и элементов И 30, 31, 33, 35 и 36 знак второго операнда меняется на обратный. При этом возможно возникновение сигналов перехода. Второй операнд с обратным знаком складывается 0 с первым операндом в устройстве для сложения в избыточном коде. Сформированная разность считывается с выходов 13-15. Пример. Поскольку при выполнении операции сложения работа п{)едл а гаемого - устройства не отличается от работы усовершенствуемого устройства, ограничимся рассмотрением лишь операции вычитания. Пусть необходимо выполнить операцию: 3 2 О 1 1 011 110 000 001 111 OlOj 1 3223 000010 111 011 ПО 110011. 0 В первом такте на вход 20 подается сигнал «1, на входы 16-18 - четвертичные разряды уменьшаемого. Четвертичные разряды, не меняясь, проходят на входы 1-3 устройства для сложения в избыточном коде и в регистр 12 запишет- ся уменьшаемое во вспомогательном коде. Р G 010 010 000 001 111 010 Во втором такте на вход 20 подается сигнал «О, на входы 16-18 - четвертичные разряды вычитаемого. Из схемы вид- Q но, что в млашем разряде сформируется код 001 и сигнал перехода во втором разряде: 001 и в третьем: 0,10 Истз 0, в четвертом: 001, в пятом: 000 в шестом; 010, в седьмом: 111, . Первый и преоб- jr разованный второй операнды складываются 00001001000000 111 010 111 010000001 010001 001 111 000010001 111 000 111 (вспомогательный код)

100101 (переносы) 0000 000 010 010 111 001 111 (основной

код) Имеем 111, результат верен.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения в избыточном последовательном коде | 1983 |

|

SU1173410A1 |

| Устройство для алгебраического сложения кодов целых комплексных чисел | 1980 |

|

SU862140A1 |

| Устройство для округления числа | 1978 |

|

SU771667A1 |

| ОТКАЗОУСТОЙЧИВАЯ ЭВМ | 2018 |

|

RU2704325C1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО ПО МОДУЛЮ | 1993 |

|

RU2034328C1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР КОДОВ ФИБОНАЧЧИ | 1993 |

|

RU2047898C1 |

| Преобразователь целых комплексных чисел в двоичный код | 1980 |

|

SU962914A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Сумматор параллельного действия | 1974 |

|

SU531157A1 |

| Арифметико-логическое устройство для сложения и вычитания чисел по модулю | 2017 |

|

RU2639645C1 |

| Авторское свидетельство СССР № 11200279, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-07—Публикация

1985-07-01—Подача