IsD

4

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор-умножитель | 1983 |

|

SU1173409A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1985 |

|

SU1337904A1 |

| Асинхронный матричный вычислитель обратных тригонометрических функций | 1982 |

|

SU1132286A1 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| Процессор для цифровой обработки сигналов | 1985 |

|

SU1257662A1 |

| Устройство для сложения операндов с плавающей точкой с контролем | 1986 |

|

SU1310826A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Арифметическое устройство для процессора быстрого преобразования Фурье | 1989 |

|

SU1631556A1 |

| Устройство для умножения | 1981 |

|

SU1012245A1 |

| Устройство для одновременного вычисления двух многочленов | 1980 |

|

SU926650A1 |

Изобретение относится к вычислительной технике и может быть использовано при проектировании цифровых вычислительных комплексов и микросхем. Цель изобретения - сокращение количества оборудования. Схема двух разрядов сумматора - вычитателя содержит восемь коммутаторов 1-8 па К ЩП-трапзисторах и десять элементов НЕ 9-18. 2 ил.

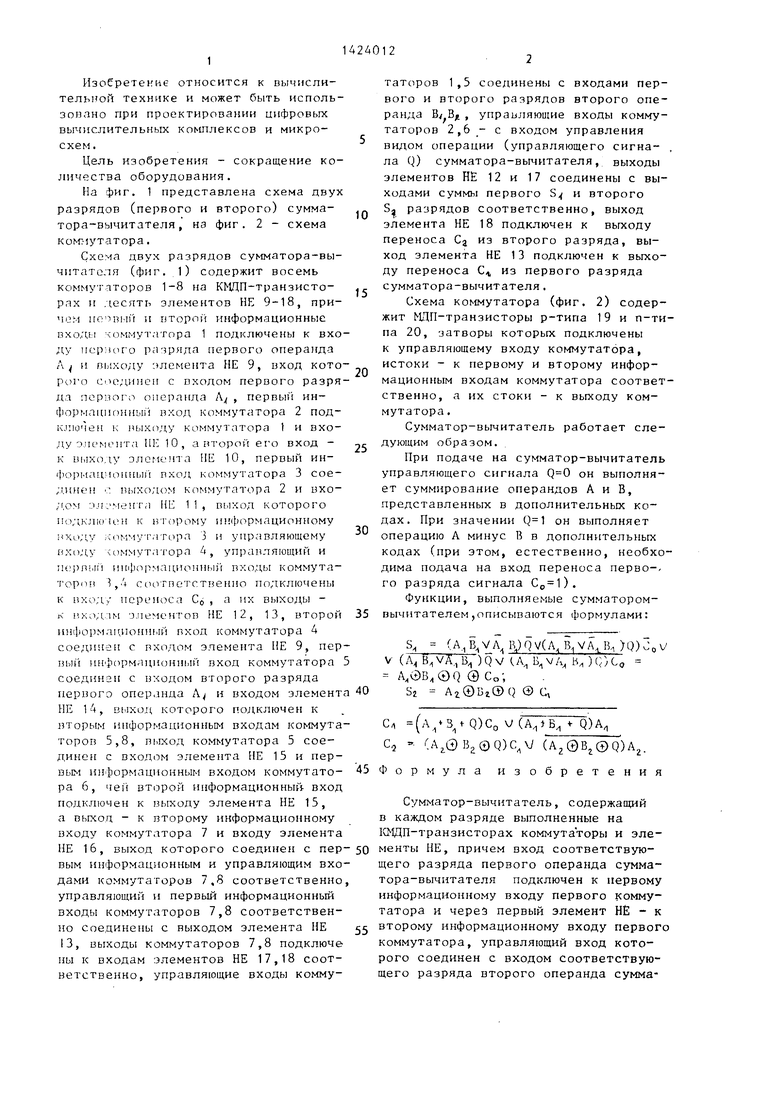

фиг.1

Изобретение относится к вычислительной технике и может быть использовано при проектировании цифровых вычислительных комплексов и микросхем .

Цель изобретения - сокращение количества оборудования.

На фиг. 1 представлена схема двух разрядов (первого и второго) сумма- тора-вычитателя, на фиг. 2 - схема ком:-1утатора.

Схема двух разрядов сумматора-вы- читателя (фиг. 1) содержит восемь коммутаторов 1-8 на КМДП-транзисто- рах и десять злементов НЕ 9-18, причем 1гг; М11-п и БТорон информационные вхо.г;ы коммутатора 1 подключены к входу псриог о разряда первого опера1гда Л и выходу элемента НЕ 9, вход кото Р1)го С| едииеи с входом первого разряда nopuoi o операнда Л , первыГ ин- формацпонньи вход коммутатора 2 подключен 1ч пыходу коммутатора ) и входу элемента 111 10, г второй его вход - к выходу эломонта ПЕ 10, первый ин- Фор1-1ац 1оиныГ вход коммутатора 3 сое- ;1.ииен .. выходом коммутатора 2 и вхо- ;i,OM :-1-1 ; меита ПК 11, выход которого П одключен к- второму И(1)ормационному нхч;1,у ;чог-г-1ут/1тора 3 и управляющему «ходу чоммутатора f, управляющий и П(;рпы11 иифо|1мационпыГ входы коммута- т орпи 3,. + соответственно подключены к входу переноса С, а пх выходы - к 1 ход:1м элементов НЕ 12, 13, второй )ормл1Г11онный вход коммутатора соедпиеп с входом элемента НЕ 9, первый ин i opмaulloнIlый вход коммутатора соединен с входом второго разряда первого опер.лпда Л и входом злемент НЕ 14, выход которого подключен к вторым информационным входам коммутаторов 5,8, В1.1ХОД коммутатора 5 соединен с входом элемента НЕ 15 и первым информационным входом коммутатора 6, 4ei второй информационны вход подключен к выходу элемента НЕ 15, а выход - к второму информационному входу коммутатора 7 и входу элемента

НЕ 16, выход которого соединен с пер-50 менты НЕ, причем вход соответствуювым информационным и управляющим входами коммутаторов 7,8 соответственно, управляющий и первьиЧ информационный входы коммутаторов 7,8 соответственно Соединены с выходом элемента НЕ 13, выходы коммутаторов 7,8 подключе пы к входам элементов НЕ 17,18 соответственно, управляющие входы комму0

5

5

. 5 0

0

татсфов 1,5 соединены с входами первого и второго разрядов второго операнда , управляющие входы коммутаторов 2, с входом управления видом операции (управляющего сигнала Q) сумматора-вычитателя, выходы элементов НЕ 12 и 17 соединены с выходами суммы первого S и второго S разрядов соответственно, выход элемента НЕ 18 подключен к выходу переноса Cj из второго разряда, выход элемента НЕ 13 подключен к выходу переноса С,, из первого разряда сумматора-вычитателя.

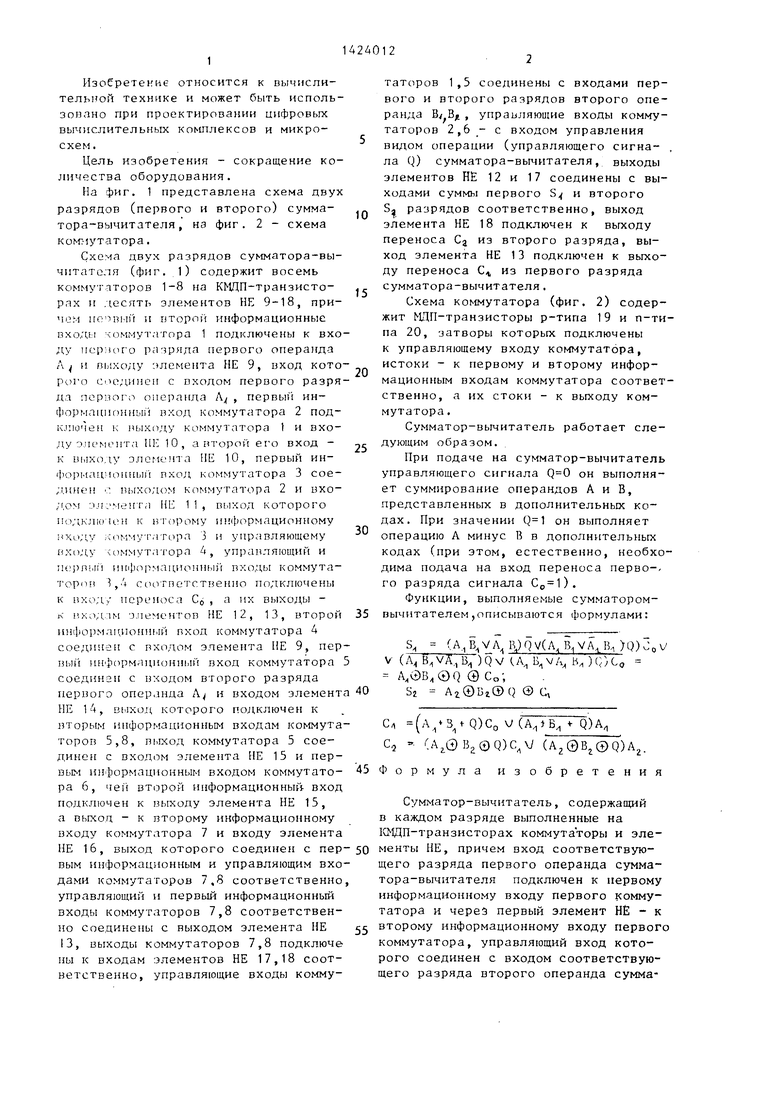

Схема коммутатора (фиг. 2) содержит МДП-транзисторы р-типа 19 и п-ти- па 20, затворы которых подключены к управляющему входу коммутатора, истоки - к первому и второму информационным входам коммутатора соответственно, а их стоки - к выходу коммутатора .

Сумматор-вычитатель работает следующим образом.

При подаче на сумматор-вычитатель управляющего сигнала он выполняет суммирование операндов А и В, представленных в дополнительных кодах. При значении он выполняет операцию А минус В в дополнительных кодах (при этом, естественно, необходима подача па вход переноса перво-- го разряда сигнала ).

Функции, выполняемые сумматором- вычитателем ,описываются формулами:

S. (А, В, V А I)QV(A, В., )Q) vJ„ V

V (,VA,B;)QV (А, B,VA, к, )q)c, A,0B,0Q О Со;

Si Аг©Вг® Q @ С,

С, (А/З Q)CO v(A,B V Q)A,

С, Ф о

iw i; ч --j i/iJ ® (А.,0 B2QQ) (A,W рмула изобретения

Сумматор-вычитатель, содержащий в каждом разряде выполненные на 1СМДП-транзисторах коммутаторы и эле

щего разряда первого операнда сумматора-вычитателя подключен к первому информационному входу первого коммутатора и череЭ первый элемент НЕ - к второму информационному входу первого коммутатора, управляющий вход которого соединен с входом соответствующего разряда второго операнда сумматора-вычитателя, а выход подключен к первому информационноьт входу второго коммутатора и череч BTopoii элемент НЕ - к второму информационному входу второго коммутатора, управляющий вход которого соединен с входом управления видом операции сумматора- вычитателя, выход третьего коммутатора через третий элемент НЕ подключен к выходу суммы соответствующего разряда сумматора-вычитателя, выход второго коммутатора через четвертый элемент НЕ соединен с управляющим входом четвертого коммутатора, выход которого соединен с входом пятого элемента НЕ, управляющий вход третьего коммутатора каждого нечетного разряда сумматора-вычитателя соединен с выходом сигнала переноса предыдущего разряда сумматора-вычитателя, отличающийся тем, что, с целью сокращения количесва оборудования, ВЕЯХОД пятого элемента НЕ каждого нечетного разряда сумматора-вычитателя является выходом сигнала инверсии переноса данного разряда сумматора-вычитлтеля и сое0

й

0

5

динен с управляющим входом третьего и с первым информационным входом четвертого коммутаторов последующего разряда сумматора-вычитателя, в каждом нечетном разряде сумматора-вычитателя первый и второй информационные входы третьего коммутатора соединены с выходами соответственно второго коммутатора и третьего элемента НЕ, первый и второй информационные входы четвертого коммутатора соединены соответственно с управляющим входом третьего и перым информационным входом первого коммутаторов, в каждом четном разряде сумматора-вычитателя первьгй и второй иш ормационные входы третьего коммутатора соедине 1ы соответственно с выходами третьего элемента НЕ и второго коммутатора, первый и второй информационные входы четвертого коммутатора соединены соответственно с управляющим входом третьего и вторым и формационным входом первого коммутаторов, выход пятого элемента НЕ является выходом сигнала переноса данного разряда.

п

W

j

О

сриг.2

| Патент США № 4592007, кл, 364-784, опублик | |||

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

| Сумматор | 1986 |

|

SU1363190A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-15—Публикация

1987-01-22—Подача