.Изобретение относится к вычислительной технике и может использоваться в интегральных схемах на КМДП- транзисторах.

Цель изобретения - расширение функциональных возможностей за счет реализации операции вычитанияс

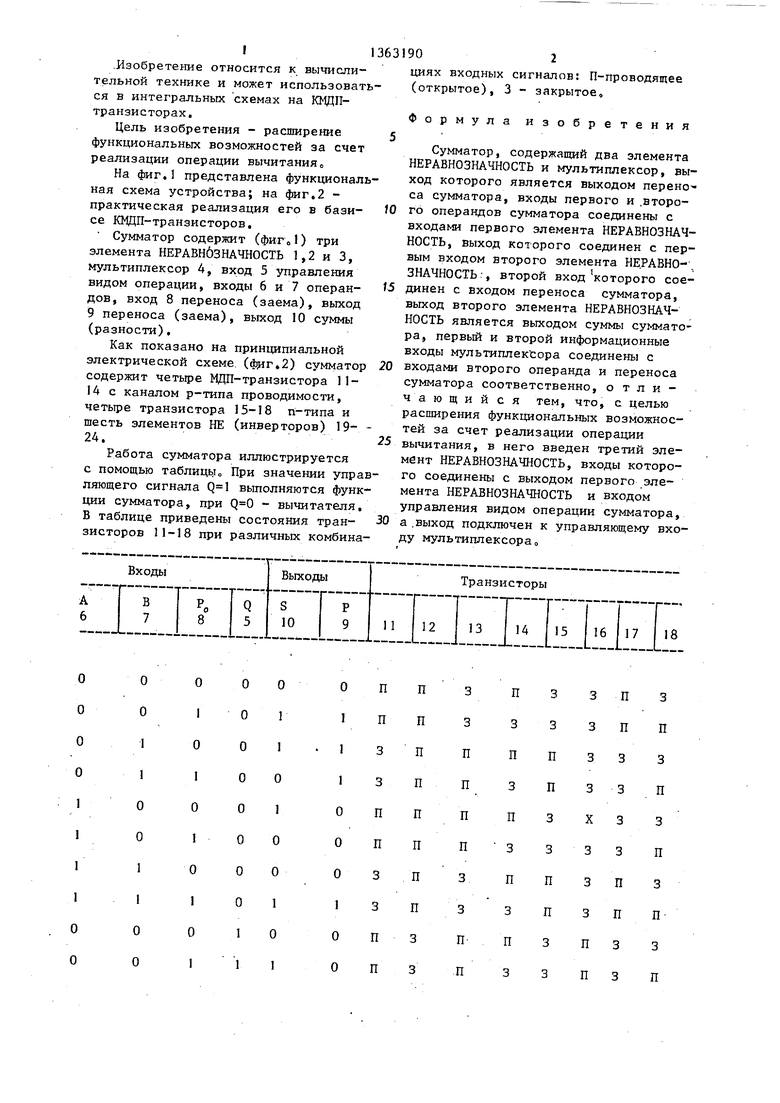

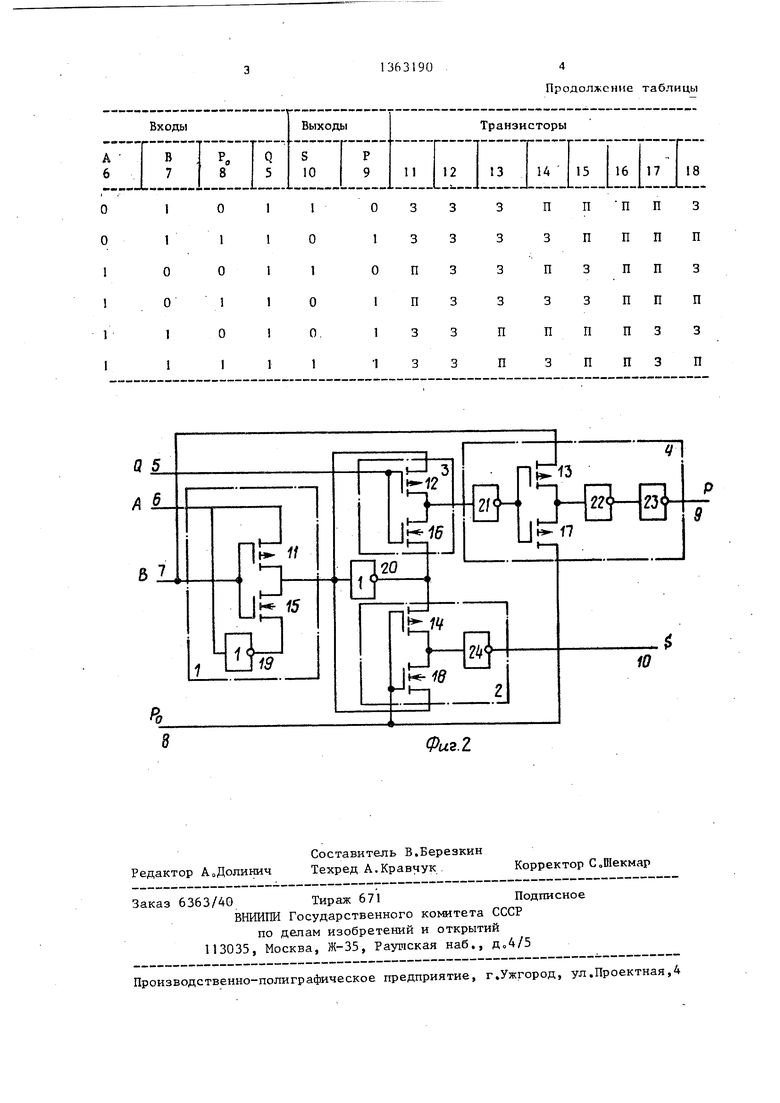

На фиг,1 представлена функциональная схема устройства; на фиг,2 - практаческая реализация его в базисе КМДП-транзисторов,

Сумматор содержит (фиг о 1) три элемента НЕРАВНбЗНАЧНОСТЬ 1,2 и 3, мультиплексор 4, вход 5 зшравления видом операции, входы 6 и 7 операндов, вход 8 переноса (заема), выход 9 переноса (заема), выход 10 суммы (разности).

Как показано на принципиальной электрической схеме. (4)гиг,2) сумматор содержит четьфе МДП-транзистора 11- 14 с каналом р-типа проводимости, четьфе транзистора 15-18 п-типа и шесть элементов НЕ (инверторов) 19- 24,

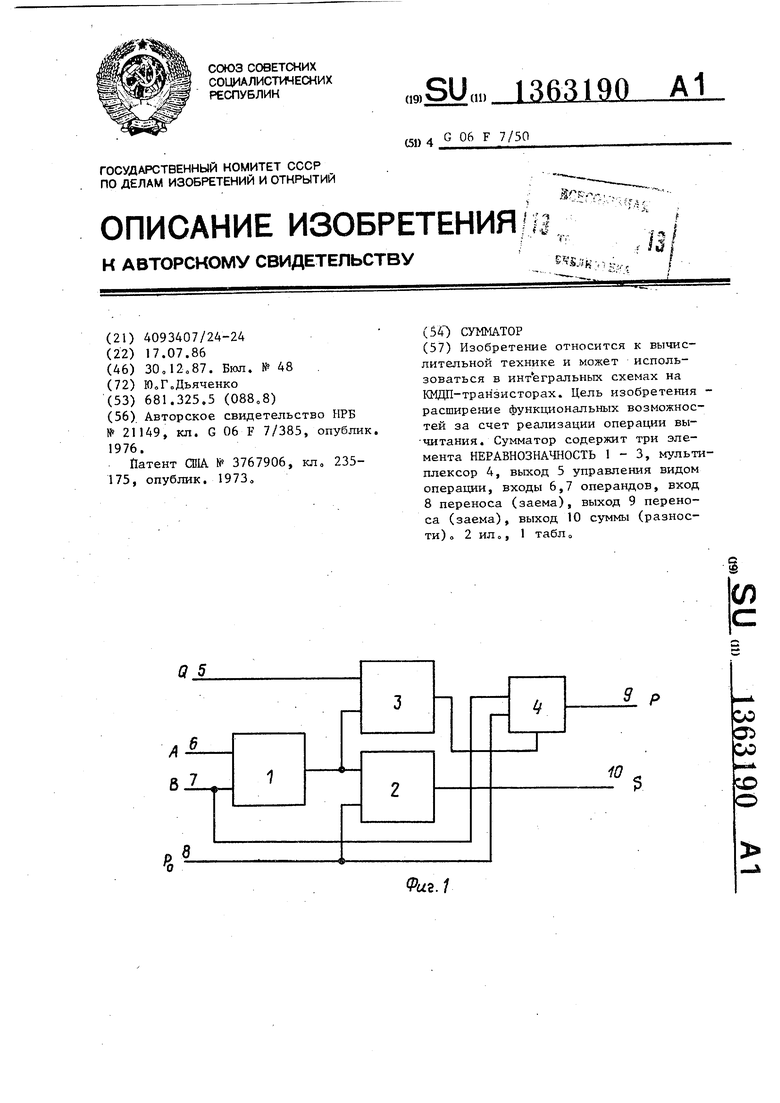

Работа сумматора иллюстрируется с помощью таблицу При значении упраляющего сигнала выполняются функции сумматора, при - вычитателя, В таблице приведены состояния тран- зисторов П-18 при различных комбина

о о 1 1

о о 1 1

о о

о I

о I

о 1

о 1 о

о

оо

ог 1

оо

о1

оо

оо

о 1 1

1

о 1

циях входных сигналов: П-проводящее (открытое), 3 - закрытое.

Формула изобретения

Сумматор, содержащий два элемента НЕРАВНОЗНАЧНОСТЬ и мультиплексор, выход которого является выходом переноса сумматора, входы первого и .второго операндов сумматора соединены с входами первого элемента НЕРАВНОЗНАЧНОСТЬ, выход которого соединен с первым входом второго элемента НЕРАВНО-. ЗНАЧНОСТЬ , второй вход которого соединен с входом переноса сумматора, выход второго элемента НЕРАВНОЗНАЧНОСТЬ является выходом суммы сумматора, первый и второй информационные входы мультиплекЬора соединены с входами второго операнда и переноса сумматора соответственно, отличающийся тем, что, с целью расширения функциональных возможностей за счет реализации операции вычитания, в него введен третий элемент НЕРАВНОЗНАЧНОСТЬ, входы которого соединены с выходом первого элемента НЕРАВНОЗНАЧНОСТЬ и входом управления видом операции сумматора, а .выход подключен к управляющему входу мультиплексора о

п п

3 3

п п

3 3

п п

п п п п п п п п

3 3

3

3

п п п п

3 3

п п

п

3

п

3

п

3

п

3

п

3

3 3

п п

3

3

п п

3

3

3 3

п п

33

33

X3

33

3п

3п

п 3 п 3

3

п

3

п

3

п

3

п

3

п

Редактор А Долинич

Составитель В.Березкин

Техред А.КравчукКорректор С„01екмар

Заказ 6363/40Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д„4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

Продолжение таблицы

Фи.г

| название | год | авторы | номер документа |

|---|---|---|---|

| Суммирующе-вычитающее устройство | 1986 |

|

SU1363192A1 |

| Комбинационный двоичный сумматор-вы-чиТАТЕль | 1979 |

|

SU824205A1 |

| Арифметико-логическое устройство | 1987 |

|

SU1481742A1 |

| Сумматор-вычитатель | 1987 |

|

SU1424012A1 |

| Параллельный накапливающий сумматор | 1988 |

|

SU1578710A2 |

| Суммирующе-вычитающее устройство | 1977 |

|

SU667967A1 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Одноразрядный сумматор-вычитатель | 1986 |

|

SU1368875A1 |

| Последовательное устройство для сложения в избыточной двоичной системе счисления | 1980 |

|

SU968807A1 |

| Одноразрядный двоичный сумматор | 1987 |

|

SU1411736A1 |

Изобретение относится к вычислительной технике и может использоваться в инт егральных схемах на КМДП-транзисторах. Цель изобретения - расширение функциональных возможностей за счет реализации операции вы- читания. Сумматор содержит три элемента НЕРАВНОЗНАЧНОСТЬ 1-3, мультиплексор 4, выход 5 управления видом операции, входы 6,7 операндов, вход 8 переноса (заема), выход 9 переноса (заема), выход 10 суммы (разности), 2 ил о, 1 табЛс, оо о: 00 (Paz.l

| Экономайзер | 1930 |

|

SU21149A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Патент CBIA № 3767906, кл, 235- 175, опублик | |||

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

Авторы

Даты

1987-12-30—Публикация

1986-07-17—Подача