ел

О)

о

00

ивтомати- програмШ

15

25

11425603

Изобретение относится к ке5 в частности к системам много управления.

Цель изобретения - повышение гибкости устройства упрощения ввода программ управления к сокращения времени перепрограммирования,

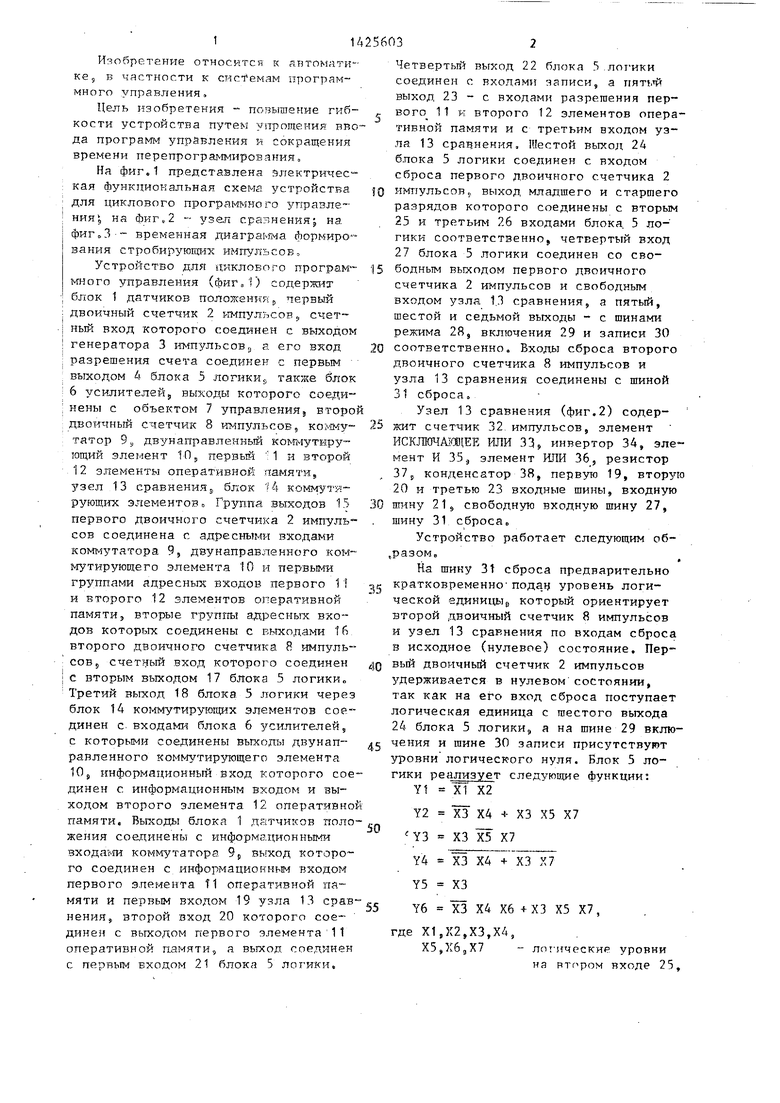

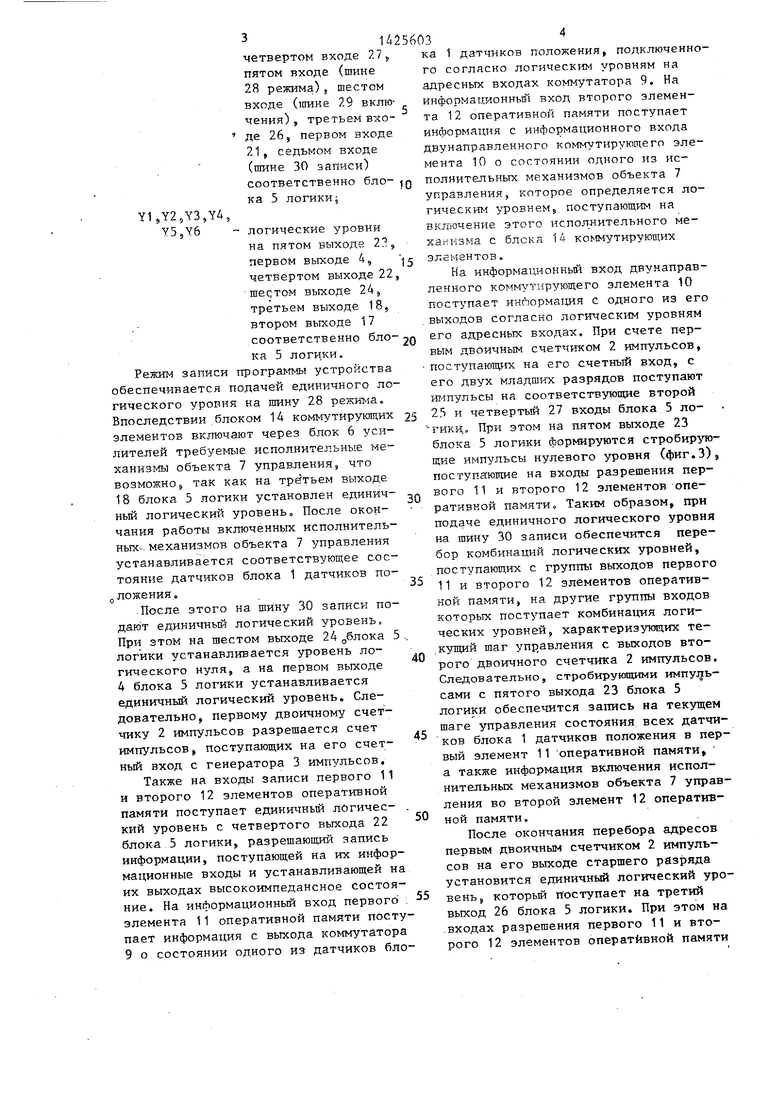

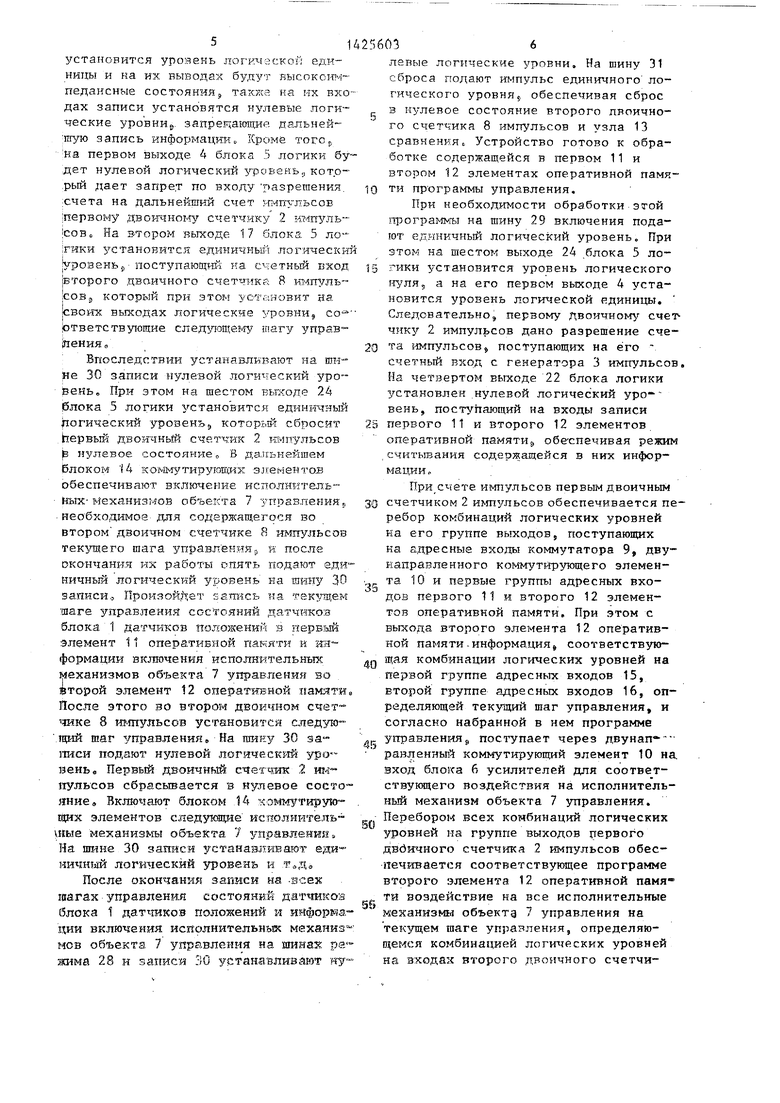

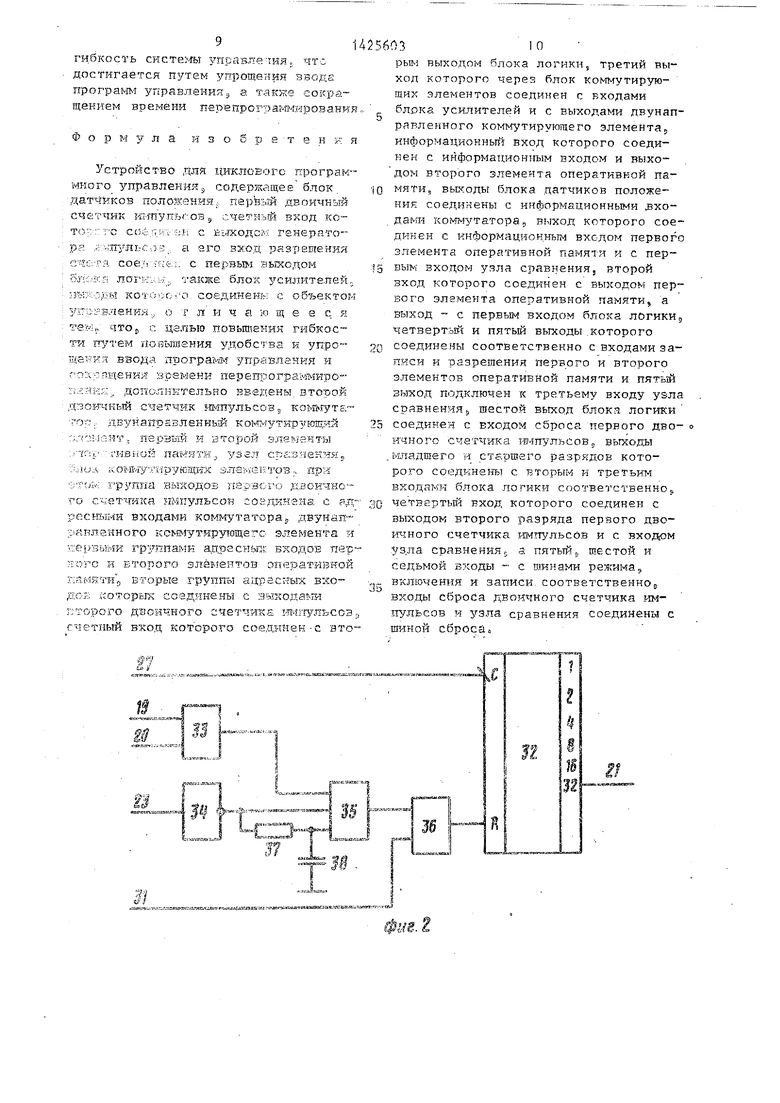

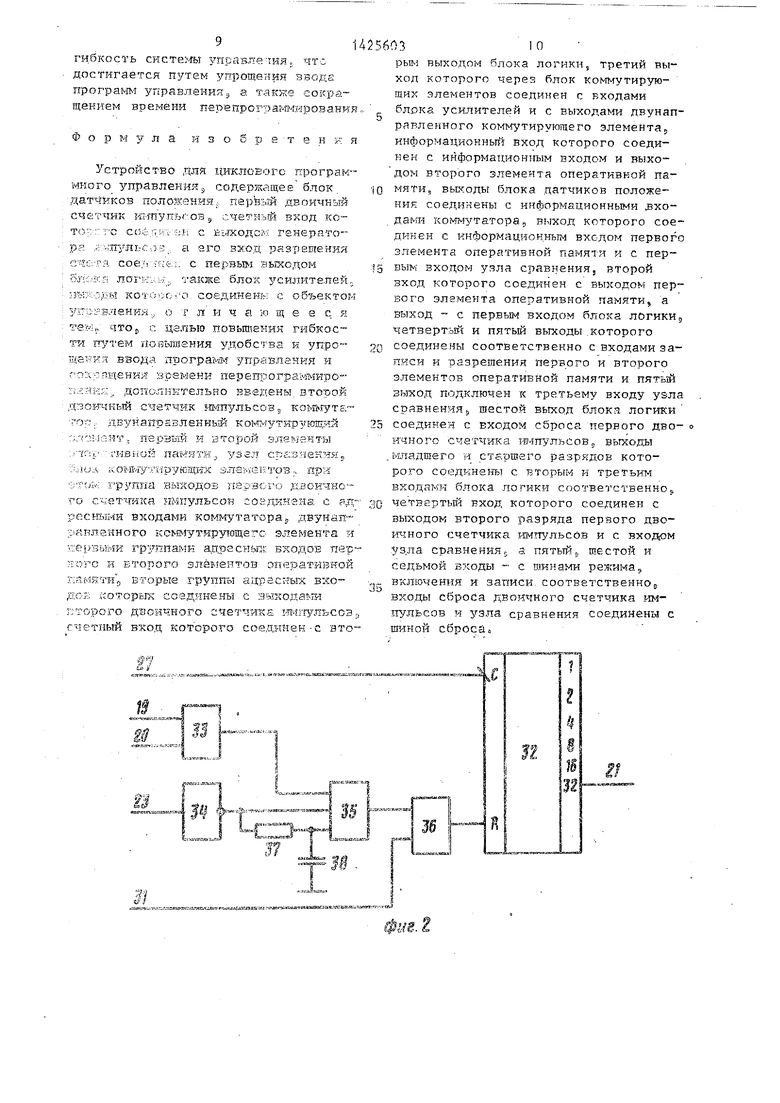

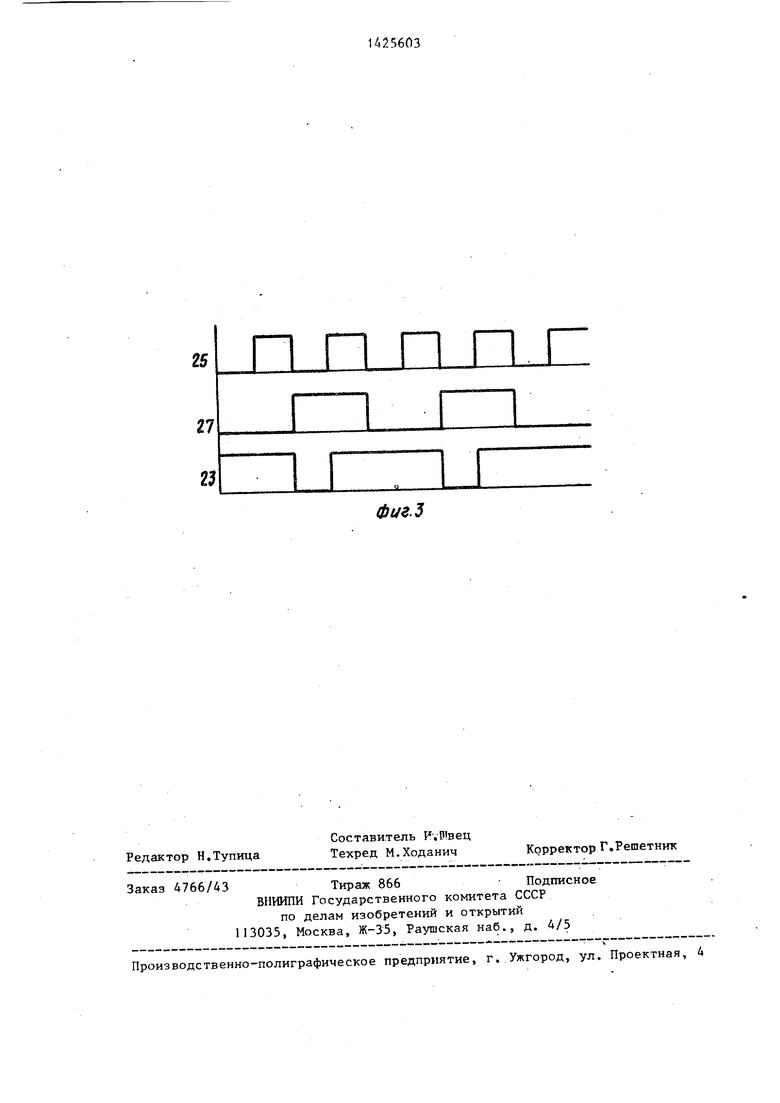

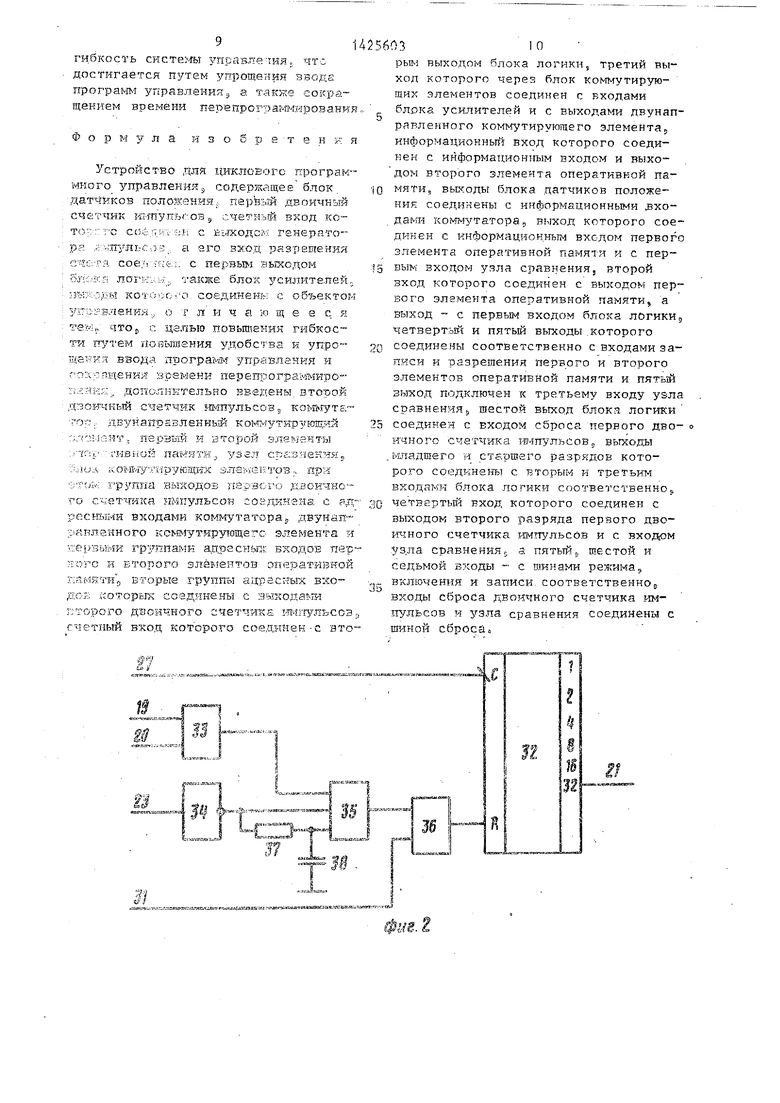

На фиг.1 представлена электрическая функциональная схема устройства ля циклового программного управления на фиг,2 узел сравнения на фиг„3 временная диаграмтча формиро™ зания стробиругоших импульсов.

Устройство для циклового програм- ного управления (фиг) содержит блок 1 датчиков положенц-я первый воичный счетчик 2 р-гмпул ьсов счет ный вход которого соединен с выходом генератора 3 ржпульсовв а его вход азрешения счета соединен с первым ыходом 4 блока 5 логики,; также блок усилителейэ выходы которого соедиены с объектом 7 управленияj второй воичный счетчик 8 импульсов, коммутатор 9, двунаправленный ком}.5утиру- ющий элемент Ш, первьй 1 и второй 12 элементы оперативной памяти, узел 13 сравненияS блок 14 коммутирующих элементов Группа выходов 15 первого двоичного счетчика 2 импуль сов соединена с адресными входами коммутатора 9, двунаправленного коммутирующего элемента 10 и первыми группами адресных входов первого 1I и второго 12 элементов оперативной памяти, вторые группы адресных входов которых соединены с выходами 16 второго двоичного счетчика 8 импуль- сов 5 счетный вход которого соединен с вторым выходом 17 блока 5 логики Третий выход 18 блока. 5 логики через блок 14 коммутирующих элементов соединен с. входами блока 6 усилителей, с которыми соединены выходы двунаправленного коммутирующего элемента lOj информационный вход которого соединен с информационным входом и выходом второго элемента 12 оперативной ггамяти, Вьпсоды блока 1 датчиков лоло- женин соединены- с информационными входаг-ш коммутатора 9 выход которого соединен с информационным входом первого элемента Т1 оперативной памяти и первым входом 19 узла 13 срав нения, второй вход 20 которого соеинен с выходом первого элемента 11 оперативной памяти, а выход соединен с nepBbiM входом 21 блока 5 логики.

30

33

40

45

с вы в т л с и г в ш с

ж м ш ш

,р

в в л ч г

50

55

5

5

0

3

0

5

Четвертьп выход 22 блока 5 .лог-ики соединен с входами записи, а пять й выход 23 - с входами раэрегаения первого 11 к второго 12 элементов оперативной памяти и с третьим входом узла 13 сравнения. Шестой выход 24 блока 5 логики соединен с входом сброса первого двоичного счетчика 2 импульсов;, выход младшего и старшего разрядов которого соединены с вторым 25 и третьим 26 входами блока, 5 ло- гики соответственно, четвертый вход 27 блока 5 логики соединен со свободным выходом первого двоичного счетчика 2 импульсов и свободным входом узла 1.3 сравнения, а пятый, шестой и седьмой выходы - с шинами режима 28, включения 29 и записи 30 соответственно. Входы сброса второго двоичного счетчика 8 импульсов и узла 13 сравнений соединены с шиной 31 сброса.

Узел 13 сравнения (фиг.2) содержит счетчик 32. импульсов, элемент ИСКЛЮЧА:ЩЕЕ или ЗЗ инвертор 34, элемент И 353 элемент ИЛИ 36, резистор 37 конденсатор 38, первую 19, вторую 20 и третью 23 входные шины, входную шину 21J свободную входную шину 27, шину 31 сброса

Устройство работает следующим об- ,разоме

На шику 3t сброса предварительно кратковременно-подац уровень логической единицы который ориентирует второй двоичный счетчик 8 импульсов и узел 13 сравнения по входам сброса в исходное (нулевое) состояние. Первый двоичный счетчик 2 импульсов удерживается в нулевом состоянии, так как на его вход сброса поступает логическая единица с шестого выхода 24 блока 5 логики, а на шине 29 включения и шине 30 записи присутствуют уровни логического нуля. Блок 5 логики реализует следующие функции:

где Х1,Х2,ХЗ,Х4,

Х5,)6дХ7 - лот-ическир. уровни

ня втором входе 25,

У1Д2ДЗДА,

четвертом входе 7.1 пятом входе (шине 28 режима), шестом входе (шине 29 включения) , третьем входе 26, первом входе 21, седьмом входе (шине 30 записи) соответственно блока 5 логики

- логические уровни на пятом выходе 23, первом выходе 4, четвертом выходе 22 шестом выходе 24, третьем выходе 18, втором выходе 17 соответственно бло ка 5 логи.ки

Режим записи программы устройства обеспечивается подачей единичного логического уровня на шину 28 режима. Впоследствии блоком 14 коммутирующих элементов включают через блок 6 усилителей требуемые исполнительные механизмы объекта 7 управления, что

18 блока 5 логики установлен единичный логический уровень После окончания работы включенных исполнительных-, механизмов объекта 7 управления устанавливается соответствующее состояние датчиков блока 1 датчиков по- ,ложеиия.

.После этого на шину 30 записи по- даю т единичный логический уровень. При этом на шестом выходе 24 блока 5 логики устанавливается уровень логического нуля, а на первом выходе 4 блока 5 логики устанавливается единичный логический уровень. Следовательно, первому двоичному счетчику 2 импульсов разрешается счет импульсов, поступающих на его счетный вход с генератора 3 импульсов,

Также на входы записи первого 11 и второго 12 элементов оперативной памяти поступает единичный лбгичес- . кий уровень с четвертого выхода 22 блока 5 логики, разрешающий запись информации, поступающей на их информационные входы и устанавливающей на их выходах высокоимпедансное состоя40

45

50

На информационный вход двунапра ленного коммути рующего элемента 10 поступает инЛормаид я с одного из е выходов согласно логическим уровням его адресных входах. При счете пер вым двоичным счетчиком 2 импульсов поступающргх на его счетный вход, с его двух младших разрядов поступаю иьшульсы на соответствующие второй 23 и четвертый 27 входы блока 5 ло Тики. при этом на пятом выходе 23 блока 3 логики формируются стробир щие импульсы нулевого уровня (фиг. поступающие на входы разрешения пе вого 11 и второго 12 элементов опе ративной памяти Таким образом, пр подаче единичного логического уров на шину 30 записи обеспечится пер бор комбинаций логических уровней, поступающих с группы выходов перво 11 и второго 12 элементов оператив ной памяти, на другие группы входо которых поступает комбинация логических уровней, характеризующих те .кущий шаг управления с выходов вто рого двоичного счетчика 2 импульсо Следовательно, стробирующими импу4| сами с пятого выхода 23 блока 5 логики обеспечится запись на текущ шаге управления состояния всех дат ков блока 1 датчиков положения в п вый элемент 11 оперативной памяти, а также информация включения испол нительных механизмов объекта 7 упр ления во второй элемент 12 операти ной памяти.

После окончания перебора адресо первым двоичным счетчиком 2 импуль сов на его выходе старшего разряда установится единичный логический у

ние. На информационный вход первого . вень, который поступает на третий

элемента 11 оперативной памяти поступает информация с выхода коммутатора 9 о состоянии одного из датчиков блоo

п

5

5

0

5

0

ка 1 датчиков положения, подключенного согласно логическим уровням на адресных входах коммутатора 9. На информационный вход второго элемента 12 оперативной памяти поступает информация с информационного входа двунаправленного коммутирующего элемента 10 о состоянии одного из исполнительных механизмов объекта 7 управления, которое определяется логическим уровнем5 поступающим на вктгючение этого исполнительного ме- xaниз зa с блока 14 коммутирующих элементов.

На информационный вход двунаправленного коммути рующего элемента 10 поступает инЛормаид я с одного из его выходов согласно логическим уровням его адресных входах. При счете первым двоичным счетчиком 2 импульсов, поступающргх на его счетный вход, с его двух младших разрядов поступают иьшульсы на соответствующие второй 23 и четвертый 27 входы блока 5 ло- Тики. при этом на пятом выходе 23 блока 3 логики формируются стробирую- щие импульсы нулевого уровня (фиг.З), поступающие на входы разрешения первого 11 и второго 12 элементов оперативной памяти Таким образом, при подаче единичного логического уровня на шину 30 записи обеспечится перебор комбинаций логических уровней, поступающих с группы выходов первого 11 и второго 12 элементов оперативной памяти, на другие группы входов которых поступает комбинация логических уровней, характеризующих те- .кущий шаг управления с выходов второго двоичного счетчика 2 импульсов. Следовательно, стробирующими импу4|Ь- сами с пятого выхода 23 блока 5 логики обеспечится запись на текущем шаге управления состояния всех датчиков блока 1 датчиков положения в первый элемент 11 оперативной памяти, а также информация включения исполнительных механизмов объекта 7 управления во второй элемент 12 оперативной памяти.

После окончания перебора адресов первым двоичным счетчиком 2 импульсов на его выходе старшего разряда установится единичный логический уровыход 26 блока 3 логики. При этом на входах разрешения первого 11 и второго 12 элементов оперативной памяти

устано Вится урозень логической единицы и ка их выводах будут высокошч- педансные состоянияj, такжа на их входах записи установятся кулевые логические уровни,, запрещающие дальней- пгую запись информации„ Кроме того,, На первом выходе. 4 блока 5 логики будет нулевой логический фовень,, кото- ,рьш дает запрет по входу разрешения, ;счета на дальнейший счет j-tMnynbcoB 1первому двоичному счетчику 2 ш-шуль- ICOB На втором выходе 17 блока 5 ло- :гики установится единичный логически урозень5, поступающий ка счетный вход второго двоичного счетчики В импуль™ jcoBj который при этом уО7 ановит на kiBOHx вьЕходах логические уровни, со Ьтветствугощие следующему тагу упраВ пения (,

Впоследствии устанавливают на шине 30 записи нулевой логический уровень. При этом на шестом выходе 24 блока 5 логики установится единичный логический уровень которьш сбросит Ьервый двои-цный счетчик 2 импульсов IB нулевое состояние В дальнейшем блоком 4 кONa syтирующих элементов обеспечивают включение исполнктел:ь- вых-Механизмов объекта 7 управления, необходимое для содержащегося во втором двоичном счетчике 8 импульсов текущего шага управления,j к после окончания их работы опять подают единичный логический уровень на шину 30 записи., Произой,1т;ет запись на шаге управления состояний датчиков блока 1 датчиков положений в первый элемент 11 оперативной пакяти и ка- формации включения исполнительных ijdexaHHSMOB объекта 7 управ ления so второй элемент 12 оперативной памяти После этого so втором двоичном счет- чике 8 импульсов установится следую .тций шаг управления. На шику 30 за- 11ИСИ подают нулевой логический уровень« Первый двоичный счетчик .2 ш--1 11ульсов сбрасывается з нулевое состо янивв Включают блоком 14 -коммутируиг- Ищх элементов следукяцяе исполнитель-- ные механизмы объекта / управления На шине 30 записи устанавливают единичный логический уровень и ,

После окончан1-1я записи на -зсех шагах управлени-й состояний датчиков блока t датчиков положений и ийформа дии включения исполнительных мехаииз нов объекта 7 управления на шинах: режима 28 и записи 30 устанавливают н-улевые логические уровни. На шину 31 сброса подают импульс единичного логического УРОВНЯ;, обеспечивая сброс в кулевое состояние второго двоичного счетчика 8 импульсов и узла 13 сравнения. Устройство готово к обработке содержащейся в первом 11 и втором 12 элементах оперативной памяти программы управления.

При необходимости обработки згой ni orpaMNw на шину 29 включения подают единичный логический уровень. При этом на шестом выходе 2А блока 5 логики установится уровень логического гтуляд а на его первом выходе 4 установится уровень логической ядиниды. Следовательно, первому двоичному счетчику 2 импульсов дано разрешение счета Ф1пульсов поступающих на его -.

счетный вход с генератора 3 импульсов. На четвертом выходе 22 блока логики установлен .нулевой логический уро вень, поступающий на входы записи

первого 11 и второго 12 элементов

оперативной памяти;, обеспечивая режим ,считывания содержащейся в них информации .При счете импульсов первьпч двоичным

счетчиком 2 импульсов обеспечивается перебор комбинаций логических уровней на его группе выходов, поступающих на адресные входь коммутатора 9, двунаправленного коммутирующего элемента 10 и первые группы адресных входов первого 11 и второго 12 элементов оперативной памяти. При этом с выхода второго элемента 12 оперативной памяти-информацияJ, соответств5по- щая комбинации логических уровней на первой группе адресных входов 15, второй группе адресных входов 16, определяющей текзпций шаг управления, и согласно набранной в нем программе

управления J поступает через деунап -

равленны) коммутирующий элемент 10 на вход блока 6 усилителей для соответствующего воздействия на исполнительный механизм объекта 7 управления. Переборок всех комбинаций логических уровней на группе выходов первого двоичного счетчика 2 импульсов обеспечивается соответствующее программе второго элемента 12 оперативной памяти воздействие на все исполнительные механизм1л объекта 7 управления на текущем шаге управления, определяющемся комбинацией логических уровней на аходак второго двоичного счетчи

10

15

ка 8 импульсов. Также на текущем шаге управления обеспечивается опрос датчиков блока 1 датчиков положений, информация состояния которых через коммутатор 9, согласно комбинации логических уровней на его адресных входах, поступает последовательно на первьй вход 19 узла 13 сравнения, на второй вход 20 которого пос- тупает последовательно информация с выхода первого элемента 11 оперативной памяти, в котором записаны согласно программе состояния датчиков на текущем шаге управления.

При равенстве текущего состояния блока 1 датчиков положения состоянию датчиков, записанному в элементе 11 оперативной памяти на данном шаге управления на выходе 21 уала 13 сравне- 20 кия устанавливается уровень логической единицы. При этом на втором выходе 17 блока 5 логики устанавливается уровень логической единицы, увеличивающий на единицу состояния второго двоичного счетчика 8 импульсов, т.е. происходит переход к следующему шагу управления.

Так как состояние датчиков блока 1 датчиков положения на следующем шаге управления не соответствует состоянию, записанному в элементе 11 оперативной памяти на данном шаге управления, то на выходе 21 узла 13 сравнения устанавливается уровень логического ну- ля., устанавливающий уровень логического нуля на втором выходе 17 блока 5 логики. Происходит отработка следующего шага управления: и т, д. о

Для функционирования узла 13 сравнения на его свободньй вход 27 поступает импульсная последовательность со свободного выхода первого двоичного счетчика 2 импульсов. Работа уз25

30

35

40

56038

элемента ИСКЛЮЧАЮиШЕ ИШ 33 устанавливается уровень логиче .кого нуля, а при их неравенстве - уровень логической единицы. Работа узла сравнения стробируется уровнем логического нуля, поступающим на третью

входную шину 23, Инвертор 34, резистор 37, конденсатор 38 обеспечивают задержку переднего фронта стро- бирующего импульса на время, достаточное для установления сравниваемой инсЬормапяи на первой :19 и второй 20 входных шинах. При несовпадении входной информации и наличии стро- бирующего импульса на выходе элемента И 35 устанавливается единичный логический уровень, сбрасьтающий двоичный счетчик 32 импульсов.

Импульс на счетный вход двоичного счетчика 32 импульсов поступает синхронно со стробируюшим импульсом (фиг.З). При совпадении информации на первой 19 и второ.й 20 входных ши- нах сброс двоичного с.четчика 32 импульсов не происходит и он обеспечи- вает Счет поступающего на свободную входную шину 27 импульса. После четь1- рехкратного сравнения последователь- костей логических уровней и отсутствии сброса с выхода элемента И 35 сброс двоичного счетчика .32 импульсов не происходит и на выходной шине 21 устанавливается единичный логический уровень.

Таким образом, повышается достоверность истинности сравнения последовательностей логических уровней, поступающих на первую 19 и вторую 20 входные шины. Следовательно, данное устройство для циклового програм - много управления имеет повышенную i гибкость за счет упрощения ввода управления и сокращения времени пере

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для циклового программного управления | 1986 |

|

SU1381432A1 |

| УСТРОЙСТВО СОРТИРОВКИ ИНФОРМАЦИИ МЕТОДОМ ПРЕОБРАЗОВАНИЯ ДАННЫХ В АДРЕС | 2008 |

|

RU2382396C2 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство для считывания графической информации | 1989 |

|

SU1683046A1 |

| ТРЕНАЖЕР МНЕМОСХЕМ | 1990 |

|

RU2101772C1 |

| Устройство для сопряжения с датчиками | 1989 |

|

SU1695286A1 |

| Многокоординатное устройство для управления | 1989 |

|

SU1777121A2 |

| Устройство для контроля логических схем | 1990 |

|

SU1718222A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| СИСТЕМА ПЕРЕДАЧИ И ОБРАБОТКИ СИГНАЛОВ О СОСТОЯНИИ ОБЪЕКТОВ | 1994 |

|

RU2087036C1 |

Изобретение относится к автоматике, в частности к системам программного управления. Цель изобретекия - повышение гибкости устройства путем упрощения ввода программ управления и сокращения Времени перепрограммирования. Устройство для циклового программного управления содержит блок датчиков положения 1, двоичные счетчики импульсов 2, 8, генератор импульсов 3, блок логики 5, коммутатор 9, двунаправленный коммутирующий элемент 10, узел сравнения 13, два элемента оперативной памяти 11 и 12, а также усилители 6, объект управления 7 и блок коммутирующих элементов 14, Метод программирования в данном устройстве требует незначительной квалификации обслуживающего персонала и не требует дополнительных средств и затрат на программиро- вание программоносителей. 3 ил. (Л

50

ла сравнения стробируется импульсами, 45 программирования, не требующей пред- поступаю1цими с пятого выхода 23 блока 5 логики.,.

Узел сравнения (фиг,2) работает следующим образом. При кратковремен- ной подаче единичного логического уровня на щину 31 сброса д воичный счетчик 32 импульсов устанавливается в иулевое состояние. На счетный вход двоичного счетчика 32 импульсов поступает последовательность импульсов со свободной входной щины 27. Сравниваемые логические уровни поступают на первую 19 и вторую 20 входные шины. При их логическом равенстве на выходе

55

варительной разработки программ управления и программирования программоносителей. На перепрограммирование предлагаемого устройства требуется меньше времени по сравнению с известными. Метод программирования в дннном устройстве требует незначительной квалификации обслуживающего персонала и не требует дополнительных технических средств и затрат на программирование программоносителей.

Таким образом, предлагаемое устройство для циклового программного управления обеспечивает повышенную

программирования, не требующей пред-

варительной разработки программ управления и программирования программоносителей. На перепрограммирование предлагаемого устройства требуется меньше времени по сравнению с известными. Метод программирования в дннном устройстве требует незначительной квалификации обслуживающего персонала и не требует дополнительных технических средств и затрат на программирование программоносителей.

Таким образом, предлагаемое устройство для циклового программного управления обеспечивает повышенную

Фиг.

| Устройство для циклового программного управления | 1981 |

|

SU1010600A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1988-09-23—Публикация

1987-01-12—Подача