18

(Л

ю

ел

OS

Изобретение относится к вычислительной технике и может быть исполь- i зовано при построении линий задержки цифровой информации.

Цель изобретения - упрощение устройства.

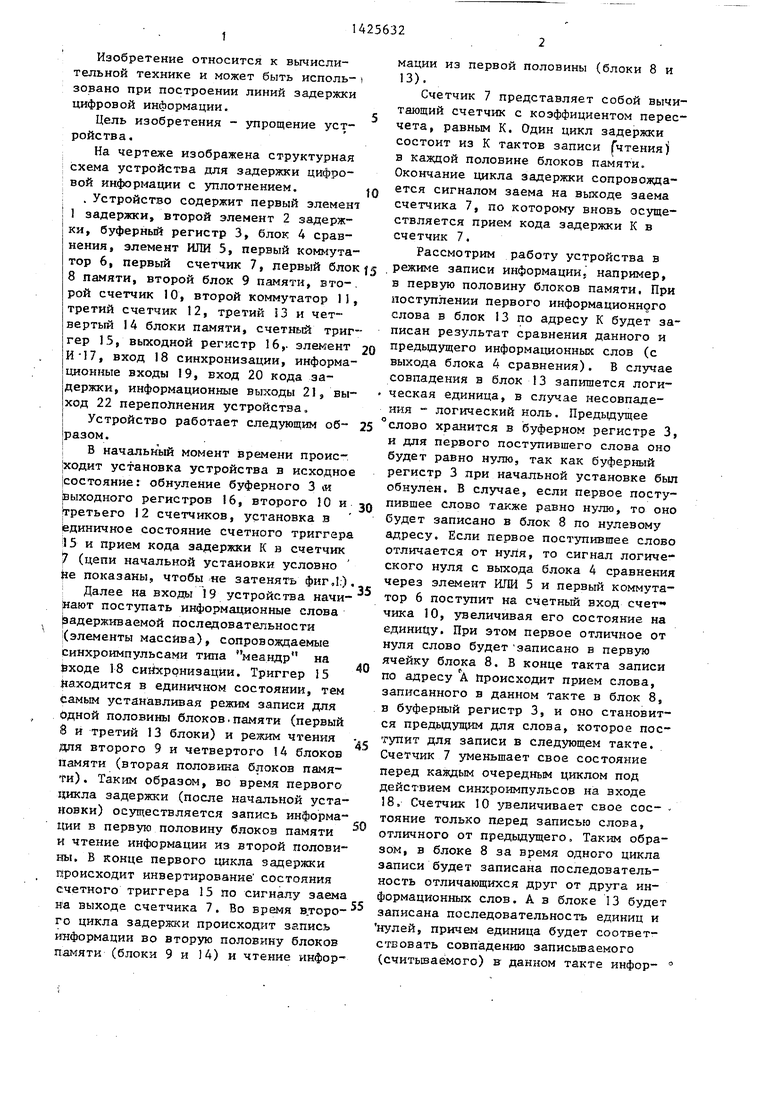

На чертеже изображена структурная схема устройства для задержки цифровой информации с уплотнением.

. Устройство содержит первый элемент 1 задержки, второй элемент 2 задержки, буферный регистр 3, блок 4 сравнения, элемент ИЛИ 5, первый коммутатор 6, первый счетчик 7, первый блок 8 памяти, второй блок 9 памяти, вто-. рой счетчик 10, второй коммутатор 11, третий счетчик 12, третий 13 и четвертый 14 блоки памяти, счетный триггер 1.5, выходной регистр 16,- элемент И-17, вход 18 синхронизации, информационные входы 19, вход 20 кода эа- держки, информационные выходы 21, выход 22 переполнения устройства.

Устройство работает следующим об- IpaaoM,

В начальнь1й момент времени проис- |ходит установка устройства в исходное состояние: обнуление буферного 3 « выходного регистров 16, второго 10 и frpeTbero 12 счетчиков, установка в единичное состояние счетного триггера 15 и прием кода задержки К в счетчик 7 (цепи начальной установки условно йе показаны, чтобы не затенять фиг,.). : Далее на входы 19 устройства начи- ают поступать информационные слова |эадерживаемой последовательности Кэлементы массива), сопровояадаемые

синхроимпульсами типа меандр на йходе 18 сийхррнизацйи. Триггер i5 находится в единичном состоянии, тем самым устанавливая режим записи для Одной половины блоков.памяти (первый 8 и третий 13 блоки) и режим чтения второго 9 и четвертого 4 блоков памяти (вторая половина блоков памяти). Таким образом, во время первого цикла задержки (после начальной установки) осуществляется запись информа™ дни в первую половину блоков памяти и чтение информации из второй половины. В конце первого цикла задержки происходит инвертирование состояния счетного триггера 15 по сигналу заема Н а выходе счетчика 7. Во время в.торого цикла задержки происходит запись информации во вторую половину блоков памяти (блоки 9 и 14) и чтение инфор

5 0

5

0

5

0

5

0

мации из первой половины (блоки 8 и 13).

Счетчик 7 представляет собой вычитающий счетчик с коэффициентом пересчета, равным К. Один цикл задержки состоит из К тактов записи чтения в каяодой половине блоков памяти. Окончание цикла задержки сопровождается сигналом заема на выходе заема счетчика 7, по которому вновь осуществляется прием кода задержки К в счетчик 7.

Рассмотрим работу устройства в режиме записи информации, например, в первую половину блоков памяти, При поступлении первого информационного слова в блок I3 по адресу К будет записан результат сравнения данного и предыдущего информационных слов (с выхода блока 4 сравнения). В случае совпадения в блок I3 запишется логи- ческая единица, в случае несовпадения - логический ноль. Предыдущее слово хранится в буферном регистре 3, и для первого поступившего слова оно будет равно нулю, так как буферный регистр 3 при начальной установке был обнулен. В случае, если первое поступившее слово также равно нулю, то оно будет записано в блок 8 по нулевому адресу. Если первое поступившее слово отличается от нуля, то сигнал логического нуля с выхода блока 4 сравнения через элемент ИЛИ 5 и первый коммутатор 6 поступит на счетный вход счет чика 10, увеличивая его состояние на единицу. При этом первое отличное от нуля слово будет записано в первую ячейку блока 8. В конце такта записи по адресу л Происходит прием слова, записанного в данном такте в блок 8, в буферный регистр 3, и оно становится предыдущим для слова, которое поступит для записи в следующем такте. Счетчик 7 уменьшает свое состояние перед каждым очередным циклом под действием синхроимпульсов на входе 18, Счеттчик 10 увеличивает свое сое- тояние только перед записью слова, отличного от предыдущего. Таким образом, в блоке 8 за время одного цикла записи будет записана последовательность отличающихся друг от друга информационных слов. А в блоке 13 будет записана последовательность единиц и нулей, причем единица будет соответ- стЕовать совпадению записываемого (считываемого) н данном такте инфор-

мационного слова со словом, записанным (считанным) в предыдущем такте. По окончании одного цикла записи через К. тактов синхроимпульсов на входе 18 произойдет переключение счет ного триггера 17 в ноль сигналом зае ма с выхода счетчика 7. Одновременно произойдет запись кода задержки в счетчик 7, обнуление счетчика 10, и начнется новый цикл задержки. При это первая половина блоков памяти (блоки 8 и 13) будет приведена в режим чтения. В первом такте режима чтения происходит чтение информации из бло- ка 13 по адресу К. Считанная информация (ноль гши единица) через первы коммутатор 6 поступит на счетный вход счетчика 10. Причем, если будет счи- тьшаться единица, то счетчик 10 не изменит свое состояние, а если будет считьшаться. ноль,то счетчик 10увеличит свое состояние на единицу.После эти го начнется чтение из блока 8 информационного слова, хранящегося по ад- ресу, установленному счетчиком 10. Пока должны будут считываться совпадающие слова информационной последовательности (.которым соответствует чтение логических единиц из блока 13), состояние счетчика 10 не будет изменяться, так как на его вхоге постоянно удерживается сигнал логической единицы. В выходной регистр 16 при зтом в каждом такте чтения счи- тьшается информация из одной и той же ячейки блока 8 адрес которой установлен счетчиком 10, При считьшании слов, отличающихся от предыдущего, из блока 13 на вход счетчика 10 пос- тупает сигнал логического нуля, увеличивающий его состояние на единицу и следующее, отличающееся слово буде считано по новому адресу из блока 8 в выходной регистр 16.

Аналогично работает и вторая половина блоков памяти (блоки 9 и 1А).

йсли количество соседних, отлиающихся друг от друга задерживаемых информационных слов в пределах одного цикла задержки превышает емкость блоков 8 или 9, то на выходе переполнения счетчиков 10 и 12 появится сигнал логического нуля, который через элемент И 17 поступает на выход 22 устройства, свидетельству, о превыще- нии емкости накопителя.

о g 0 5 О 0 5

0

5

Формула изобретения

Устройство для задержки цифровой информации с уплотнением, содержащее первый счетчик, первый и второй блоки памяти, элемент ИЛИ, элемент И, счетный триггер и выходной регистр, причем информационные входы первого и второго блоков памяти поразрядно объединены и являются информацион гы- ми входами устройства, информационные выходы первого и второго блоков памяти поразрядно объединены и подключены к информационным входам выходного регистра, выходы которого являются информационными выходами устройства, прямой выход счетного триггера подключен к входу управления режимом первого блока памяти, инверсньй выход счетного триггера подключен к входу управления режимом второго блока памяти, входы выборки первого и второго блоков памяти объединены и соединены с входом приема выходного регистра, вычитающий вход и информационные входы первого счетчика являются соответственно входом синхронизации и входом кода задержки устройства, отличающееся тем, что, с целью упрощения устройства, в него введены первый и второй элементы задержки, буферный регистр, блок сравнения, первый и второй коммутаторы, второй и третий счетчики, третий и че . вертый блоки памяти, причем вход первого элемента задержки, первый вход элемента ИЛИ и вход приема буферного регистра подключены к входу синхронизации устройства, выход первого элемента задержки подключен к входу второго элемента задержки и. входам выборки третьего и четвертого блоков памяти, выход второго элемента задержки соединен с входом приема выходного регистра, информационные входы буферного регистра соединены с информационными входами устройства, выход буферного регистра соединен с первьм входом блока сравнения, второй вход которого соединен с информационными входами устройства, выход блока сравнения соединен с информационными входами третьего и четвертого блоков памяти и вторьтм входом . элемента ИЛИ, выход которого соединен с первыми информационными входами первого и второго коммутаторов, вторые информационные входы которых подклю-.

чены к информационным выходам третьего и четвертого блоков памяти соот- ветственно, выходы первого и.второго Коммутаторов подключены к суммирующим :0ходам второго и третьего счетчиков соответственно, информационные выходы второго и третьего счетчиков под- шпочены соответственно к адресным 1)ходам первого и второго блоков памяти, входы установки в О второго II третьего счетчиков, вход счетного триггера, вход приема первого счетчика подключены к выходу эаема пер- lioro счетчика, информационные выходы

которого соединены с адресными входами третьего и четвертого блоков па мяти, управляющий вход первого коммутатора и вход управления режимом третьего блока памяти подключены к прямому выходу счетного триггера, управляющий вход второго коммутатора и вход управления режимом четвертого блока памяти подключены к инверсному вьпсоду счетного триггера, выходы переполнения второго, и третьего счетчиков подключены к входам элемента И, выход которого является .выходом переполнения устройства,

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

| Декодирующее устройство кода Рида-Соломона | 1988 |

|

SU1640830A1 |

| Таймер | 1985 |

|

SU1357939A1 |

| Устройство для контроля блоков оперативной памяти | 1983 |

|

SU1161993A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1990 |

|

SU1785034A1 |

| Многоканальное устройство ввода аналоговой информации | 1987 |

|

SU1418726A1 |

| Устройство для задержки цифровой информации | 1986 |

|

SU1383325A1 |

| Устройство для обмена данными между источником и приемником информации | 1988 |

|

SU1557566A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1988 |

|

SU1606996A1 |

| Устройство для программируемой задержки информации | 1986 |

|

SU1394213A1 |

Изобретение относится к вычислительной технике и может быть ис- пользовано при построении линий задержки цифровой информации. Цель изобретения - упрощение устройства за счет уменьшения затрат оборудования на его реализацию для задержки информации с последовательно повторяющимися элементами. Устройство содержит элементы 1 и 2 задержки, буферный регистр 3, блок 4 сравнения, элемент ИЛИ 5, коммутаторы 6 и 11, счетчики 7, 10 и 12, блоки 8, 9, 13 и 14 памяти, счетный триггер 15, выходной регистр 16 и элемент И 17. 1 ил.

| Электроника,№ 13, 1982, с.67 | |||

| Электроника, № 7, 1983, о62 |

Авторы

Даты

1988-09-23—Публикация

1987-02-16—Подача