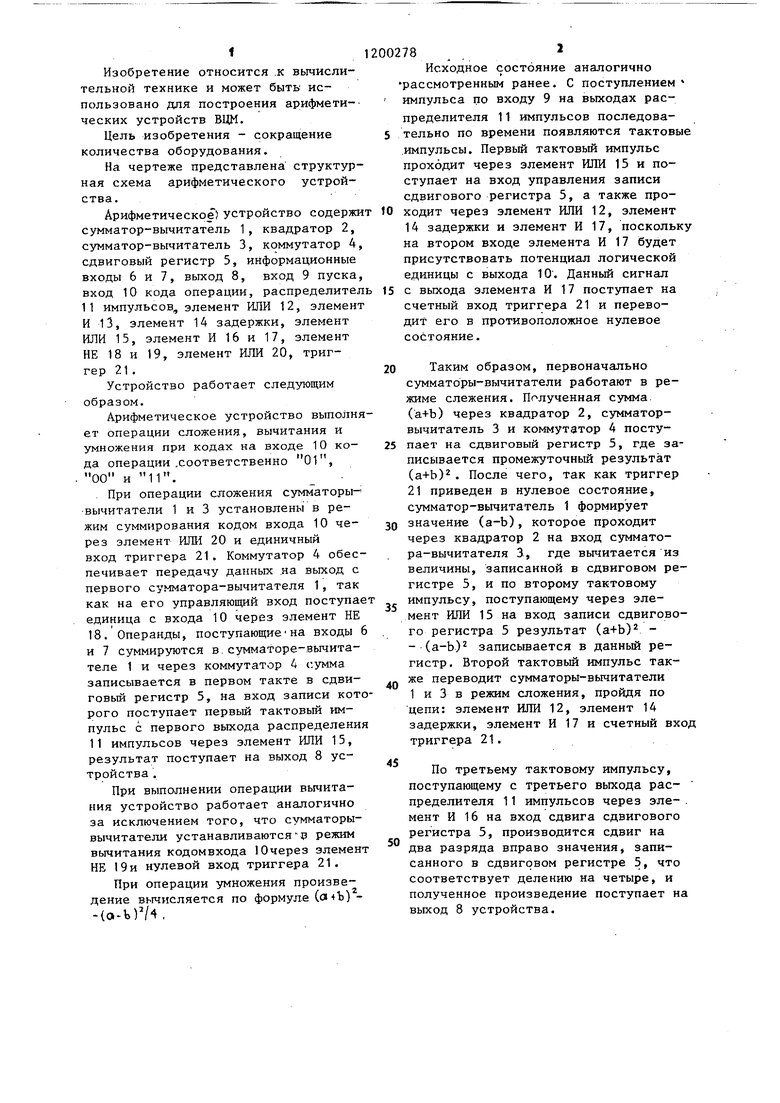

Изобретение относится .к вьгаислительнон технике и может бытв использовано для построения арифметических устройств ВЦМ. Цель изобретения - сокращение количества оборудования. На чертеже представлена структур ная схема арифметического устройства. Арифметическое)устройство содерж сумматор-вычитатель 1, квадратор 2, сумматор-вычитатель 3, коммутатор 4 сдвиговый регистр 5, информационные входы 6 и 7, выход 8, вход 9 пуска вход 10 кода операции, распределите 11 импульсов, элемент ИЛИ 12, элемен И 13, элемент 14 задержки, элемент ИЛИ 15, элемент И 16 и 17, элемент НЕ 18 и 19, элемент ИЛИ 20, триггер 21 . Устройство работает следующим образом. Арифметическое устройство выполн ет операции сложения, вычитания и умножения при кодах на входе 10 кода операции .соответственно 01, 00 и 11. При операции сложения сумматорывычитатели 1 и 3 установлены в режим суммирования кодом входа 10 через элемент ИЛИ 20 и единичный вход триггера 21. Коммутатор 4 обес печивает передачу данных .на выход с первого сумматора-вычитателя 1, так как на его управляющий вход поступа единица с входа 10 через элемент НЕ 18. Операнды, поступающиена входы и 7 суммируются в.сумматоре-вычитателе 1 и через коммутатор 4 сумма записывается в первом такте в сдвиговый регистр 5, на вход записи кот рого поступает первый тактовый импульс с первого выхода распределени 11 импульсов через элемент ИЛИ 15, результат поступает на выход 8 устройства . При выполнении операции вычитания устройство работает аналогично за исключением того, что сумматорывычитатели устанавливаютсяР режим вычитаиия кодомвхода Ючерез элемен НЕ 19и нулевой вход триггера 21. При операции умножения произведение вычисляется по формуле (о+Ъ) -{а-Ь)4, 78 Исходное состояние аналогично рассмотренным ранее. С поступлением импульса по входу 9 на выходах распределителя 11 импульсов последовательно по времени появляются тактовые .импульсы. Первый тактовый импульс проходит через элемент ИЛИ 15 и поступает на вход управления записи сдвигового регистра 5, а также проходит через элемент ИЛИ 12, элемент 14 задержки и элемент И 17, поскольку на втором входе элемента И 17 будет присутствовать потенциал логической единицы с выхода 10. Данный сигнал с выхода элемента И 17 поступает на счетный вход триггера 21 и переводит его в противоположное нулевое состояние. Таким образом, первоначально сумматоры-вычитатели работают в режиме слежения. Полученная сумма. (а+Ь) через квадратор 2, сумматорвычитатель 3 и коммутатор 4 поступает на сдвиговый регистр 5, где записывается промежуточный результат (а+Ь)2. После чего, так как триггер 21 приведен в нулевое состояние, сумматор-вычитатель 1 формирует значение (а-Ь), которое проходит через квадратор 2 на вход сумматора-вычитателя 3, где вычитается из величины, записанной в сдвиговом регистре 5, и по второму тактовому импульсу, поступающему через элемент ИЛИ 15 на вход записи сдвигового регистра 5 результат (а+Ь) - (а-Ь) записывается в данный регистр. Второй тактовый импульс также переводит сумматоры-вычитатели 1 и 3 в режим сложения, пройдя по цепи: элемент ИЛИ 12, элемент 14 задержки, элемент И 17 и счетный вход триггера 21. По третьему тактовому импульсу, поступающему с третьего выхода распределителя 11 импульсов через эле- . мент И 16 на вход сдвига сдвигового регистра 5, производится сдвиг на два разряда вправо значения, записанного в сдвиговом регистре 5, что соответствует делению на четыре, и полученное произведение поступает на выход 8 устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1987 |

|

SU1425656A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1988 |

|

SU1640709A1 |

| Устройство для поворота вектора | 1983 |

|

SU1144104A1 |

| Устройство для определения позиционных характеристик непозиционного кода | 1985 |

|

SU1283948A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Цифровой спектроанализатор | 1982 |

|

SU1092518A1 |

| Устройство для определения среднего арифметического значения | 1986 |

|

SU1310840A1 |

| Квадратор | 1987 |

|

SU1501049A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Преобразователь позиционного кода в модулярный код | 1987 |

|

SU1460772A1 |

АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО, содержащее два сумматора-вычитателя, квадратор, сдвиговый регистр, причем первый и второй информационные входы устройства соединены соответственно с первым и вторым информационными входами первого сумматоравычитателя, выход которого соединен с входом квадратора,выход которого . соединен с первым входом второго сумматора-вычитателя, а выход сдвигового регистра является выходом устройства, отличающееся тем, что, с целью сокращения оборудования, оно содержит коммутатор, распределитель импульсов, триггер, элемент задержки, три элемента И, три элемента ИЛИ, два элемента НЕ, причем выходы первого и второго сумматорО з-вычитателей соединены с соответствующими ин- , формационными входами коммутатора, выход которого соединен с информационным входом сдвигового регистра, выход которого соединен с вторым входом второго сумматора-вычитате--, С(щ:г 13 - . ,; .ля, вход пуска устройства соединен с входом распределителя импульсов, первый выход которого соединен с первыми входами первого и второго элементов ИЛИ, выходы которых соединены соответственно с входом элемента задержки и входом записи сдвигового регистра, второй выход распределителя 11мпульсов соединен с вторым входом первого элемента ИЛИ и с первым входом первого элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, третий выход распределителя импульсов соединен с первым входом второго 8 элемента И, выход которого соединен с входом сдвига сдвигового регистра, (Л первый разряд входа кода операции устройства соединен с вторыми входами первого и второго элементов И, с первыми входами третьих элементов И и ИЛИ и через первый элемент НЕ с управляющим входом коммутатора, второй разряд входа кода операции устройства соединен с вторым входом третьего элемента ИЛИ и входом второго элемента НЕ, выходы которых соединены соответственно с единичHbw и нулевым входами триггера, выход которого соединен с управляющими входами первого и второго сумматороввычитателей, вход элемента задержки соединен с вторым входом третьего элемента И, выход которого соединен со счетным входом триггера.

| Устройство для умножения одноразрядных @ -ичных чисел в системе остаточных классов | 1982 |

|

SU1100619A1 |

| ТИИЭР, 1980, Т.68, № 4, с.114.116, рис | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-12-23—Публикация

1984-07-30—Подача